Qu'est-ce qui détermine la vitesse SPI Un guide complet

L'interface périphérique série (SPI) est célèbre pour le transfert de données à grande vitesse. Ce protocole de communication synchrone permettent

LeInterface périphérique série(En)SPI) Est célèbre pourTransfert de données à grande vitesse. CeciProtocole de communication synchronePermet des données efficacesTransfertEntreDispositifs, Avec quelquesTaux de transfert de données Dépassant 100 MHz. Alors, pourquoi ton projetPerformanceFrappez toujours ces topTaux de transfert de données? Votre vraiVitesse de SPIEt globalementDébitSont limités par trois domaines clés.

💡La finalePerformanceDe n'importe quelleSPIDonnéesTransfertEst un équilibre de votreDispositifsLimites matérielles, la qualité de la connexion physique et la configuration de votre logiciel.

Les clés à emporter

- La vitesse de votre SPI dépend de trois facteurs principaux: les limites matérielles de vos appareils, la qualité de vos connexions physiques et la configuration de votre logiciel.

- Vérifiez toujours les limites de vitesse dans les fiches techniques pour vos appareils maître et esclave. L'appareil le plus lent définit la vitesse maximale de votre bus SPI.

- Une bonne conception de PCB est importante. Gardez les fils courts, faites correspondre les longueurs de trace et utilisez un plan de masse solide pour éviter les problèmes de signal à des vitesses élevées.

- Utilisation directeMémoireAccess (DMA) dans votre logiciel pour les meilleures performances. DMA laisse votreMicrocontrôleurEnvoyer des données rapidement sans ralentir le processeur principal.

Rôle du matériel dans la vitesse SPI

La première étape pour comprendre la vitesse SPI maximale de votre système consiste à examiner le matériel lui-même. Avant même d'écrire une ligne de code ou de concevoir un PCB, les fiches techniques de vos périphériques maîtres et esclaves fixent une limite supérieure. Votre performance finale est fondamentalement liée aux capacités de cesCircuits intégrés.

Limites de l'horloge maître

Votre périphérique maître, généralement un microcontrôleur, génère l'horloge SPI (SCK). Cet appareil a une fréquence maximale à laquelle il peutInterface périphérique série. Vous pouvez trouver cette limite dans leSection des caractéristiques électriques de sa fiche technique. Les tableaux spécifient souvent le maximumFSCK(Fréquence d'horloge de SPI) sous différentes tensions de fonctionnement.

Par exemple, la fiche technique d'un microcontrôleur peut présenter ses caractéristiques SPI comme ceci:

| Symbole | Paramètre | Conditions | Min | Typ | Max | Unité |

|---|---|---|---|---|---|---|

| FSCK | Fréquence d'horloge SPI | Contrôleur récepteur mode 2.7 V <VDD< 3.6 V | - | - | 45 | MHz |

| Mode émetteur contrôleur 2.7 V <VDD< 3.6 V | - | - | 45 | MHz |

Note:Les valeurs dans le tableau ci-dessus sont basées sur

FPCLKx/3, OùFPCLKxEst l'horloge périphérique. La valeur maximale réelle dépend de l'architecture spécifique du microcontrôleur.

L'horloge système du maître joue également un rôle. Le périphérique SPI fonctionne souvent sur une horloge dérivée de l'horloge système principale.

- L'architecture d'horloge interne d'un microcontrôleur peut limiter l'horloge d'entrée du module SPI. Par exemple, un module peut seulement accepter une entrée maximale de48 MHz.

- Cette horloge d'entrée est ensuite divisée pour générer le signal SCK final pour le transfert SPI.

- Cela signifie que même si le périphérique SPI peut théoriquement fonctionner plus rapidement, ses performances sont plafonnées par l'horloge que vous lui donnez.

Contraintes d'horloge esclave

Considérons maintenant le dispositif esclave. Chaque esclave SPI, que ce soit unCapteur, Puce de mémoire, ou un autre microcontrôleur, a également une fréquence d'horloge maximale qu'il peut gérer. C'est souvent le goulot d'étranglement le plus important dans une configuration maître/esclave.Dépasser cette limite entraînera l'esclave à mal interpréter les données, entraînant une corruption des données pendant le transfert..

💡Votre bus SPI est aussi rapide que son appareil le plus lent. La vitesse de communication finale doit être réglée sur le plus faible des deux maximums (maître ou esclave).

Vous devez vérifier soigneusement la fiche technique de l'esclave. Vous pouvez trouver différents taux de transfert de données maximum en fonction de l'opération. Par exemple, unLe microcontrôleur STM32 en mode esclave pourrait prendre en charge 40 MHz pour recevoir des données, mais une vitesse inférieure comme 24 MHz pour une communication full-duplex. Ces différences peuvent provenir de la logique interne nécessaire pour échantillonner et envoyer des données simultanément. Pour la plupart des périphériques esclaves SPI, une règle de base sûre est de maintenir le taux d'horloge SPI inférieurUn dixième de la fréquence d'horloge système de l'esclavePour assurer un transfert de données fiable.

Retards de traitement des esclaves

Une fréquence d'horloge élevée n'est pas toujours égale à un débit élevé. La véritable mesure de la performance est la quantité de données que vous pouvez transférer au fil du temps. De nombreux appareils esclaves ont besoin d'une pause entre les transactions pour traiter les informations. Ceci est connu commeTemps de traitement esclaveOuRetard inter-transaction.

Imaginez que vous envoyez une commande à un capteur. Le capteur a besoin de temps pour effectuer une mesure avant d'avoir des données prêtes pour le prochain transfert. Une horloge SPI rapide est inutile si le maître doit attendre longtemps que l'esclave soit prêt. Ce délai a un impact considérable sur votre débit de données global.

Certains scénarios courants nécessitant ce délai comprennent:

| Scénario | Pourquoi un délai est nécessaire |

|---|---|

| L'esclave a une logique interne lente | L'appareil a besoin de temps pour traiter l'octet de données précédent. |

| Protocoles SPI multi-trames | Le protocole lui-même nécessite un intervalle de temps spécifique entre les trames. |

| SPI Flash page écrit | La puce de mémoire doit faire une pause pour verrouiller une adresse avant d'écrire des données. |

| Éviter les erreurs de chronométrage | Un petit retard peut aider à prévenir les erreurs à des vitesses d'horloge SPI très élevées. |

Alors, comment savez-vous quand l'esclave est prêt pour le prochain transfert? Les appareils utilisent plusieurs méthodes pour signaler leur état:

- Pin occupé:Certains appareils ont une broche de sortie dédiée qu'ils affirment pour signaler qu'ils sont occupés à traiter.

- Registre d'état:Vous pouvez interroger un registre d'état sur l'esclave. Ce registre contient souvent des bits comme

Trdy(Transmettre prêt) ouRrdy(Recevoir prêt) pour indiquer son état. - Interrompt:L'esclave peut utiliser ces bits de statut pour déclencher une interruption sur le maître, signalant activement qu'il est prêt pour la prochaine transaction SPI.

La couche physique de l'interface périphérique série

Une fois que vous avez compris les limites de votreCircuits intégrésIl faut voir les liens physiques entre eux. Les traces de circuits imprimés (PCB) et les fils qui forment votre bus SPI ne sont pas des conducteurs parfaits. À hautes fréquences, ces chemins physiques introduisent leur propre ensemble de défis qui peuvent dégrader la qualité du signal et limiter vos performances globales.

Chemin et mise en page du signal

Les longs fils et les traces de PCB peuvent agir comme de minuscules antennes. Ce comportement introduit un retard de propagation, qui est le temps qu'il faut pour qu'un signal se déplace du maître aux périphériques esclaves. A basse vitesse, ce retard est négligeable. À des taux de transfert de données élevés, cela devient un problème majeur.

Les décalages dans la longueur de trace entre l'horloge (SCK) et les lignes de données (MOSI/MISO) entraînent des erreurs de synchronisation. Le signal d'horloge peut arriver au récepteur à un moment différent de celui des données. Cela peut amener le périphérique esclave à verrouiller le mauvais bit de données, corrompant ainsi tout le transfert. Au fur et à mesure que la fréquence de votre signal augmente, la période d'horloge raccourcit, ce qui rend votre conception beaucoup plus sensible aux petites différences de retard de propagation.

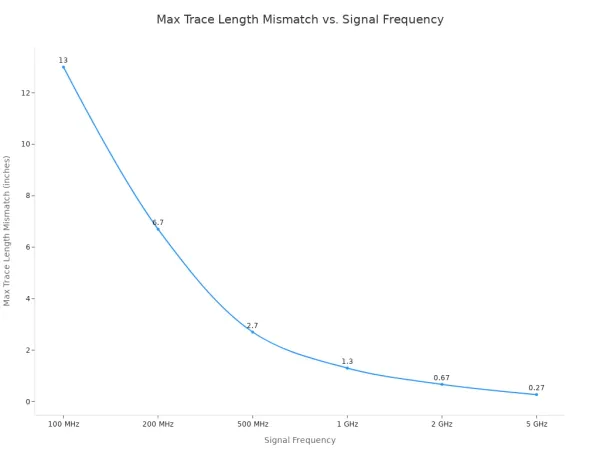

Le tableau ci-dessous montre à quelle vitesse la tolérance pour l'inadéquation de longueur de trace se rétrécit à mesure que la fréquence d'horloge SPI augmente.

| Fréquence du signal | Période d'horloge (T) | Max Tolérance Inclinaison (20% T) | Retard de propagation (FR4) | Déadéquation de la longueur de la trace max |

|---|---|---|---|---|

| 100 MHz | 10 NS | 2 NS | ~ 150 ps/dans | ~ 13 dans |

| 200 MHz | 5 NS | 1 NS | ~ 150 ps/dans | ~ 6.7 dans |

| 500 MHz | 2 NS | 0,4 ns | ~ 150 ps/dans | ~ 2.7 dans |

| 1 GHz | 1 NS | 0,2 ns | ~ 150 ps/dans | ~ 1.3 dans |

| 2 GHz | 0,5 ns | 0,1 ns | ~ 150 ps/dans | ~ 0,67 dans |

| 5 GHz | 0,2 ns | 0,04 ns | ~ 150 ps/dans | ~ 0,27 dans |

Astuce Pro:Lorsque votre bus SPI fonctionne dans la plage 50-100 MHz, vous devez traiter les traces comme des lignes de transmission. Pour empêcher des réflexions de signal et la sonnerie, vous pouvez ajouter la petite terminaison de sérieRésistances(Par exemple, 22-33Ω) près des broches du pilote. Placez-les sur les lignes SCK, MOSI et CS au niveau du maître et sur la ligne MISO à chaque esclave.

Capacité et intégrité du bus

Chaque élément sur votre PCB, à partir duGoupilles d'ICAux traces elles-mêmes, ajoute une petite quantité de capacité indésirable. Ceci est appeléCapacité parasite. Il existe entre la trace du signal et son plan de référence le plus proche, généralement le plan de masse. Bien que vous ne pouvez pas l'éliminer, vous devez le gérer.

Cette capacité a un impact direct sur le temps de montée de votre signal. Le temps de montée est la rapidité avec laquelle le signal peut passer d'une basse tension à une haute tension.La capacité élevée du bus agit comme un obstacle, résistant à la capacité du signal à s'élever. Cela ralentit le temps de montée et arrondit les arêtes vives de votre signal d'horloge. Si le bord d'horloge devient trop lent, le périphérique esclave peut ne pas l'enregistrer correctement, ce qui limite votre fréquence d'horloge maximale. Intéressant,La capacité a un effet beaucoup plus petit sur le temps de chute du signal.

L'ajout de périphériques esclaves au bus SPI augmente la capacité de charge totale, ce qui peut dégrader davantage l'intégrité du signal. Vous pouvez contrôler cet effet parasite grâce à une conception minutieuse des PCB.

- Utiliser des stratifiés de couche de surface plus mincesPour réduire la distance au plan de masse adjacent.

- Choisissez des matériaux à faible Dk (constante diélectrique)Pour que votre PCB abaisse la capacité totale.

- Sélectionnez des composants avec des tailles de plomb plus petitesMinimiser leur contribution.

Discussion croisée et bruit

La diaphonie se produit lorsque l'énergie électromagnétique d'une trace de signal "fuit" dans une trace voisine. Sur un PCB, cela se produit souvent entre deux traces SPI fonctionnant côte à côte. Cette énergie couplée crée du bruit sur la trace "victime". Si le bruit est suffisamment important, il peut provoquer de fausses transitions de signaux et corrompre votre transfert de données.

Ce phénomène est principalement dû au couplage capacitif. La meilleure façon de lutter contre la diaphonie et les autres bruits externes est d'utiliser un plan de sol bien conçu.

Un plan de masse solide fournit un chemin de retour à faible impédance pour les courants de signal. Cela resserre les champs électromagnétiques autour de la trace du signal, les contenant et les empêchant d'interférer avec d'autres signaux.Un plan de référence plus proche conduit à un couplage plus serré et moins de bruit.

Pour améliorer votre conception et atteindre des taux de transfert de données plus élevés, vous devez:

- Maximisez votre plan au sol:Utilisez autant d'espace libre que possible sur le PCB pour le plan de masse.

- Utilisez des couches de sol dédiées:Dans les cartes multicouches, un plan de masse dédié assure une excellente séparation et réduit le bruit.

- Ajouter des vias de couture:Si vous devez diviser un plan de masse, utilisez des vias pour "assembler" les zones séparées, créant ainsi un chemin continu à faible impédance.

En gérant soigneusement la disposition, la capacité et la mise à la terre de votre PCB, vous pouvez préserver l'intégrité du signal. Cela vous permet d'exécuter votre bus SPI à une vitesse de spi plus élevée et d'obtenir un meilleur débit global.

L'impact du logiciel sur les performances SPI

Votre matériel etPCB mise en pageDéfinir le potentiel de communication à haute vitesse, mais votre logiciel détermine si vous pouvez réellement le réaliser. Les choix que vous faites dans votre code, des paramètres de protocole de base aux méthodes de traitement des données, contrôlent directement vos performances et votre débit SPI finaux.

Mode SPI et Timing

LeProtocole SPIEst synchrone, ce qui signifie que les périphériques maître et esclave doivent s'entendre sur le timing. Vous configurez cette synchronisation en sélectionnant le mode SPI correct. Une inadéquation ici entraînera l'échec total du transfert. Le mode est défini par deux paramètres dans la fiche technique du périphérique esclave:

- Polarité d'horloge (CPOL):Ceci règle l'état de repos du signal d'horloge (bas ou haut).

- Phase d'horloge (ACSP):Ceci détermine si les données sont échantillonnées sur le premier (en tête) ou le deuxième (en fin) bord d'horloge.

Ces deux réglages se combinent pour créer quatre modes SPI possibles. Si votre maître est placé au mode 0 (CPOL = 0, CPHA = 0), il s'attend à échantillonner des données sur un bord croissant d'horloge. Votre appareil esclave doit également être configuré pour ce mode afin d'assurer un transfert de données réussi. Se tromper est une source courante d'erreurs qui empêche la communication entre les appareils.

Conducteur et frais généraux d'OS

La façon dont votre microcontrôleur déplace les données a un impact énorme sur les performances. Vous avez généralement deux choix pour gérer un transfert SPI: interruptions ou accès direct à la mémoire (DMA). L'utilisation d'interruptions est plus simple pour un transfert de base, mais elle crée une surcharge CPU importante qui limite vos taux de transfert de données maximum. Pour la haute performance, DMA est la méthode supérieure.

💡DMA permet au périphérique SPI de transférer des données directement vers ou à partir de la mémoire sans impliquer le CPU. Cela libère le processeur pour effectuer d'autres tâches, augmentant considérablement l'efficacité de votre système et permettant un débit de données plus élevé.

Le tableau ci-dessous compare les deux approches:

| Caractéristique | SPI axé sur l'interruption | SPI piloté par DMA |

|---|---|---|

| Frais généraux de CPU | Haut; CPU gère chaque transfert d'octet. | Faible; le CPU est libre après le démarrage du transfert. |

| Débit | Inférieur; Limité par la capacité du CPU à interrompre le service. | Plus haut; Peut atteindre la vitesse maximale de SPI. |

| Cas d'utilisation | Bon pour faible tauxCapteursOu des commandes simples. | Idéal pour le streaming à haute vitesse et les gros blocs de données. |

Lorsque vous devez atteindre les taux de transfert de données les plus élevés à partir de composants tels que les ADC haute résolution ou la mémoire flash, vous devez utiliser DMA. Cette approche minimise les retards logiciels et permet à votre bus SPI de fonctionner plus près de ses limites matérielles.

Votre vitesse finale SPI dépend de trois facteurs clés. Ce sont les limites de votre matériel, vos connexions physiques et l'efficacité de votre logiciel. Vous devez tenir compte des trois domaines pour atteindre les taux de transfert de données élevés pour lesquels SPI est connu. Un système rapide nécessite une approche complète.

💡À emporter exploitable:Pour trouver votre véritable vitesse maximale, vérifiez d'abord la fiche technique du périphérique esclave pour connaître sa limite de vitesse. Ensuite, testez cette vitesse avec la disposition et le logiciel de votre PCB. Ajustez à la baisse à partir de là pour trouver le taux stable le plus rapide pour votre projet spécifique.