Integrated Circuit Packaging: Technologien, Standards und zukünftige Trends

Die Verpackung integrierter Schaltkreise hilft bei der Entscheidung, wie Halbleiter in Zukunft funktionieren werden. Ingenieure verwenden Verpackungen, um Halbleiter besser arbeiten zu lassen. Es hilft auch, Geräte kleiner und schneller zu machen.

Die Verpackung integrierter Schaltkreise hilft bei der Entscheidung, wie Halbleiter in Zukunft funktionieren werden. Ingenieure verwenden Verpackungen, um Halbleiter besser arbeiten zu lassen. Es hilft auch, Geräte kleiner und schneller zu machen. Die Industrie begann mit einfachen Verpackungen für integrierte Schaltkreise. Jetzt werden fortschritt liche Lösungen für komplexere Systeme verwendet. Diese Lösungen helfen auch beim Mischen verschiedener Arten von Teilen. Die Verpackung ist jetzt sehr wichtig, um Halbleiter besser zu machen. Menschen, die Verpackungs änderungen beobachten, können dazu beitragen, neue Ideen zu entwickeln.

Wichtige Imbiss buden

-

Integrierte Schaltung Verpackung hält Chips sicher. Es verbindet verschiedene Teile miteinander. Es hilft auch, Geräte kleiner und schneller zu werden. Dadurch arbeiten sie besser und halten länger.

-

Fortschritt liche Verpackungs methoden wie 3D-Stapeln, fächerlose Wafer-Level-Verpackungen und Chiplet-Designs sorgen dafür, dass die Dinge besser funktionieren. Sie verbrauchen weniger Strom. Sie helfen auch beim Aufbau komplexerer Systeme.

-

Industries tandards von JEDEC und IPC stellen sicher, dass Verpackung und Prüfung gut sind. Sie helfen, die Dinge sicher zu halten und sicher zustellen, dass Teile zusammenarbeiten.

-

Neue Materialien und Kühlt echno logien helfen, die Wärme zu kontrollieren. Sie machen auch moderne Halbleiter pakete länger halten.

-

Unternehmen arbeiten zusammen und erfinden immer wieder neue Dinge. Dies hilft, Probleme bei der Herstellung von Chips zu lösen. Es hilft auch, die Verpackung in Zukunft zu verbessern.

Verpackung für integrierte Schaltkreise Übersicht

Zweck und Funktionen

Verpackung für integrierte SchaltkreiseIst sehr wichtig, wie gut Elektronik funktioniert. Ingenieure verwendenIc verpackungUm Chips und andere Teile zusammen zusetzen. Dies macht ein vollständiges System. Es hilft, Dinge kleiner zu machen und sie schneller arbeiten zu lassen. Kleinere Teile wie 0201 und 01005 zeigen, wieIc verpackungSchrumpft Geräte, fügt aber weitere Funktionen hinzu.

Einige Hauptberufe vonIc verpackungSind:

-

Unterstützung für Schaltkreise und andere Teile

-

Elektrische Pfade für schnelle Signale und Daten herstellen

-

Umgang mit Wärme mit Kühl werkzeugen wie Mikro heatrohren

-

Halten Sie dieIcSicher vor Schäden und der Umwelt

-

Hilfe beim Stapeln von Teilen in 3D mit System auf Paket und Paket auf Paket

-

Mit starken Tests und neuen Materialien die Lebensdauer der Dinge verlängern

Ingenieure suchen nach neuen Materialien, wieKohlenstoff nanoröhren, Zu machenIc verpackungBesser. Das Substrat inIc verpackungIst auch der Schlüssel, um Dinge kleiner zu machen und besser zu funktionieren.

Entwicklung der IC-Verpackung

Die Geschichte vonIc verpackungZeigt, wie schnell sich Halbleiter verändert haben. In den 1970er Jahren begannen Multi-Chip-Module, verschiedene Teile zu mischen. AltIc verpackungWege in neue verwandelt, die Logik setzen,Erinnerung,SensorenUnd Antennen zusammen. Moores Gesetz konnte nicht nur mit 2D mithalten, daher wechselte die Industrie zum 3D-Stapeln und Mischen von Teilen.

Neue Ideen wie Durch-Silizium-Vias, Inter poser undFan-out-Verpackung auf Wafer-EbeneGeändertIc verpackung. Dadurch können Geräte besser arbeiten, kleiner werden und mehr tun. Jetzt arbeiten Geräte-, Paket-und PCB-Design für kunden spezifische Lösungen im Bereich High-Speed-Computing und IoT zusammen. Diese Veränderung zeigt, wieIntegrierte Schaltung verpackungGing von einfachen Boxen zu komplexen Systemen mit vielen Technologien.

Branchen-Schnapp schuss:

Schlüssels tatistik

Details

Markt größe (2024)

Projizierte Markt größe (2033)

90,18 Mrd. USD

CAGR (2025-2033)

9,35%

Größter Regional markt

Asien-Pazifik

Am schnellsten wachsende Region

Nordamerika

Dominantes Typen segment

Organische Substrate

Dominantes Endbenutzer segment

Unterhaltung elektronik

Schlüssel verpackungs technologien

SOP, DFN, GA, FOWLP

Markt treiber

Nachfrage nach Unterhaltung elektronik, 5G, Verpackungs innovationen

Wichtige Markt teilnehmer

Amkor, ASE Group, Henkel, Hitachi Chemical, Sumitomo Bakelit, LG Chem, Power tech, Toray

Bemerkens werte Trends

Annahme von FOWLP für Leistung und Miniatur isierung

Regionale Highlights

Chinas Industrie wuchs 2023 um 18,5%; Die USA führen Nordamerika mit einem Anteil von 75% an

Strategische Faktoren

F & E, Kooperationen, Regierungs initiativen

IC Verpackungs technologien

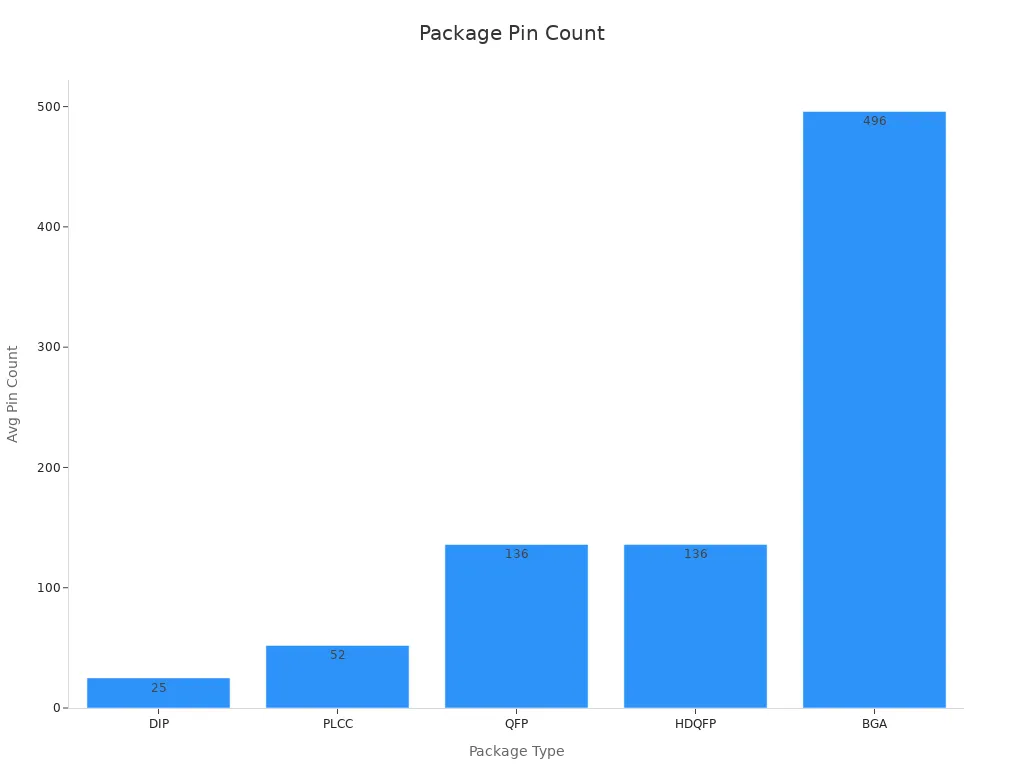

Traditionelle Pakete

Ingenieure haben traditionelle verwendetIc verpackungSeit vielen Jahren. Diese Pakete helfen, Chips zu schützen und zu verbinden. Einige gebräuchliche Typen sind Dual In-Line Package (DIP), Plastic Leaded Chip Carrier (PLCC) und Quad Flat Package (QFP). Jeder Typ funktioniert am besten für bestimmte Geräte.

-

DIP hat zwei Reihen von Pins. Es kann 8 bis 42 Pins haben.Die Stifte haben einen Abstand von 1,778 bis 2,54mm. DIP ist gut für die Durch loch montage. Keramische DIPs sind sehr zuverlässig.

-

PLCC hat J-förmige Leitungen. Es kann 20 bis 84 Pins haben. PLCC spart Platz und kann auf Oberflächen oder in Steckdosen montiert werden.

-

QFP hat Möwen flügel leitungen. Es kann 32 bis 240 Pins haben. Der Stift abstand kann nur 0,4mm betragen. QFP verfügt über freiliegende Pads, um bei Hitze zu helfen.

Diese traditionellenIc verpackungTypen sind ausgereift und kosten weniger. Sie funktionieren gut für viele Zwecke. Aber sie haben Grenzen in der Anzahl der Stifte, der Größe und ihrer Leistung. Da Geräte kleiner und komplexer werden, benötigen Ingenieure neue Möglichkeiten, Chips zu verpacken.

Anmerkung:TraditionellIc verpackungLängere Verbindungen verwendet. Dies kann zu mehr Signal verlust und geringerer Dichte führen.

|

Paket typ |

Pin Count Range |

Tonhöhen bereich (mm) |

Abmessungen des Körpers (mm) |

Dicke Bereich (mm) |

Wichtige Leistungs highlights |

|---|---|---|---|---|---|

|

DIP |

8-42 |

1.778 - 2.54 |

Breite: 6, 35-13, 97 |

0,81-12,96 |

Reife, kosten günstige Durchgangs loch montage, keramische Versionen für hohe Zuverlässigkeit |

|

PLCC |

20-84 |

1.27 |

Breite/Länge: 9-29. 28 |

3.56 - 4.57 |

J-Leads, Oberflächen-oder Sockel halterung, platzsparende Bleiform |

|

QFP |

32 - 240 |

0, 4-0, 8 |

Breite/Länge: 5-45, 7 |

1-4. 9 |

Möwen flügel leitungen, Oberflächen montage, Keramik versionen für hohe Zuverlässigkeit, freiliegende Pads für Wärme absenkung |

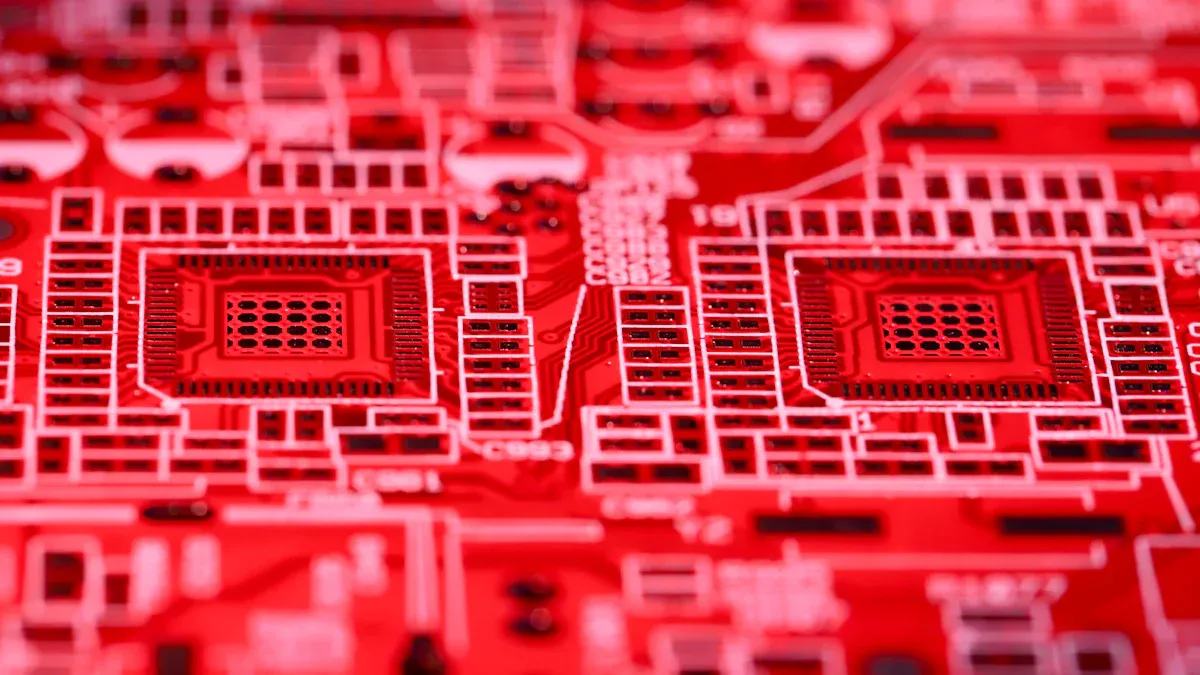

Fortschritt liche Lösungen

Fortschritt liche Verpackungen haben die Art und Weise verändert, wie Ingenieure entwerfenIc verpackung. Diese neuen Möglichkeiten umfassen Ball Grid Array (BGA), Chip Scale Package (CSP), Wafer Level Package (WLP), Fan-Out Wafer-Level Package (FOWLP) und System-in-Package (SiP). Diese tragen dazu bei, die Verbindungen zu verkürzen, mehr Pins hinzuzufügen und die Signale zu verbessern.

-

BGA verwendet Löt kugeln anstelle von Leitungen. Es kann bis zu 975 Pins haben. BGA gibt bessere Wärme und elektrische Leistung.

-

CSP und WLP machen das Paket fast so klein wie der Chip. Dies hilft, Geräte noch kleiner zu machen.

-

Mit FOWLP passen mehr Teile in ein Paket. Es hilft auch bei Hitze.

-

SiP setzt andersIcTypen, wie Logik, Speicher und RF, zusammen. Dies hilft, komplexe Geräte herzustellen.

Ingenieure nutzen diese fortschritt lichen Methoden für schnelle Daten, geringe Größe und bessere Wärme kontrolle. Diese Methoden reduzieren auch Interferenzen und machen Geräte zuverlässiger.Flip-Chip-Bindung und durch Silizium-Vias (TSVs)Winzige Verbindungen herstellen. Diese Funktionen helfen Signale und reduzieren unerwünschte Effekte.

-

In Smartphones, fort geschrittenIc verpackungSetzt Prozessoren, Speicher und RF-Module zusammen. Dies macht Telefone leistungs stark und klein.

-

In Autos helfen starke SiP-Module der Elektronik, an schwierigen Orten zu arbeiten.

-

In Rechen zentren verwenden schnelle Prozessoren fortschritt liche Verpackungen für bessere Geschwindigkeit und weniger Leistung.

Tipp:Fort geschritteneIc verpackungKönnen sich Chips stapeln und kürzere Verbindungen verwenden. Dies bedeutet schnellere Geschwindigkeiten, weniger Verzögerung und bessere Leistung.

3D IC Verpackung

3DIc verpackungIst ein großer Schritt in der Chip-Technologie. Diese Methode stapeltIcSchichten übereinander. Es werden Dinge wie Durch-Silizium-Vias und Silizium-Inter poser verwendet. Ingenieure verwenden 3DIc verpackungFür höhere Dichte, bessere Signale und weniger Strom verbrauch.

-

Im Jahr 2024,Über 42 Milliarden 3D-gestapelte Matrizen einheiten ausgeliefert. Dies zeigt, dass viele Menschen 3D verwendenIc verpackungJetzt.

-

3D-Pakete können bis zu 2.300 Verbindungen pro cm² haben.

-

FOWLP hat einen thermischen Widerstand von nur 0,6 °C/W. Das hilft bei Hitze.

-

3D-gestapelte Verpackungen machen jetzt 28% des Umsatzes mit Logik chips aus.

|

Metrik/Trend |

Wert/Statistik |

Beschreibung |

|---|---|---|

|

3D-gestapelte Matrizen einheiten versendet (2024) |

Über 42 Milliarden |

Schnelle Einführung von 3D-IC-Verpackungen |

|

Verbindungs dichte in 3D-Paketen |

2.300 I/Os pro cm² |

Erhöhte Integrations dichte |

|

Thermischer Widerstand in FOWLP |

0,6 °C/W |

Verbesserte thermische Leistung |

|

Umsatz anteil für 3D-gestapelte Verpackungen |

28% des Gesamtumsatzes mit Logik chips |

Bedeutender Markt beitrag |

|

KI-Beschleuniger mit fortschritt licher Verpackung |

Über 72% (2024) |

Hohe Akzeptanz in Leistungs segmenten |

|

Verbesserung der Signal integrität (FO-PLP) |

30% besser als FO-WLP |

Verbesserte Signal qualität |

|

Reduktion der parasitären Induktivität |

24% Rückgang |

Elektrische Leistungs gewinne |

|

TSV-Widerstands verbesserung |

19% besser |

Fortschritte in der vertikalen Verbindungs technologie |

|

Stroms paren über Chiplet-Verpackungen |

18% durchschnitt liche Einsparungen |

Energie effizienz gewinne |

|

Die Stapel werte im kommerziellen DRAM |

Bis zu 8 Schichten |

Fortschritt in der vertikalen Integration |

Ingenieure verwenden Chiplet-Designs, um komplexe Systeme mit kleinen, wieder verwendbaren Blöcken zu bauen. Mit der Chiplet-Verpackung können sie verschiedene Funktionen wie Logik, Speicher und Analog in einem SiP mischen. Dies hilft Chiplet-Designs von Dritt anbietern und beschleunigt die Entwicklung von Produkten.

-

Chiplet-Verpackungen verkürzen die Anschlüsse und signalisieren besser.

-

Die Embedded-Düse-Technologie reduziert die Verzögerung um 22% und spart bis zu 18% Strom.

-

Der Flip-Chip-Bump-Pitch beträgt jetzt in sub-5nm Designs etwa 80 µm. Dies hilft, die Dinge kleiner zu machen.

Anmerkung:Der Markt für fortschritt liche Verpackungen belief sich im Jahr 2024 auf 70,3 Milliarden US-Dollar. Sie wuchs jedes Jahr um 13,2%. Bis 2026 werden über 40% der Prozessor gewinne vonIc verpackungVerbesserungen.

Ingenieure verwenden SiP-und Chiplet-Lösungen für neue Geräte. Diese Möglichkeiten tragen dazu bei, Geräte kleiner, schneller und billiger zu machen. Wenn die Industrie wächst,Ic verpackungWird für eine bessere Leistung und neue Ideen noch wichtiger sein.

Industries tandards

JEDEC und IPC

JEDEC und IPC machen wichtige Regeln für die Verpackung von integrierten Schaltkreisen. Diese Gruppen schreiben Dokumente, um Unternehmen bei der Entwicklung und Prüfung von Produkten zu unterstützen. JEDEC macht Regeln für Halbleiter bauelemente. IPC macht Regeln für Leiterplatten und Baugruppen. Sie arbeiten zusammen, um Produkte sicher und von hoher Qualität zu halten.

|

Standard-/Dokument titel |

Standard nummer |

Datum |

Zweck |

Ausschuss (e) |

|---|---|---|---|---|

|

Einstufung der Feuchtigkeit-/Reflow-Empfindlichkeit für nicht hermetische SMDs |

J-STD-020F |

Dez 2022 |

Definiert die Feuchtigkeit empfindlichkeit für sichere Verpackung und Handhabung |

JC-14, JC-14.1 |

|

Handhabung, Verpackung, Versand und Verwendung von feuchtigkeit empfindlichen SMDs |

J-STD-033D |

Apr 2018 |

Standard isiert Handhabung und Versand, um Schäden zu vermeiden |

JC-14, JC-14.1 |

|

Vor konditionierung von nicht hermetischen Oberflächen montage vorrichtungen vor Zuverlässigkeit tests |

JESD22-A113I |

Apr 2020 |

Setzt den Vor konditionierung fluss für die Zuverlässigkeit prüfung |

JC-14.1 |

|

Paket-Warpage-Messung von oberflächen montierten ICs bei erhöhter Temperatur |

JESD22-B112C |

Nov 2023 |

Misst Paket verwerfend während des Lötens |

JC-14, JC-14.1 |

|

Adapter Test Platine Zuverlässigkeit Test Richtlinien |

JEP176A |

Jun 2025 |

Ldenen Zuverlässigkeit tests für ICs mit Adapter platinen |

JC-14, JC-14.3 |

Diese Regeln helfen Unternehmen, weniger Fehler zu machen und besser zusammen zuarbeiten. Sie helfen Unternehmen auch dabei, Gesetze für Medizin-, Auto-und Heime lektronik einzuhalten.

Qualität und Inter operabilität

Qualität und Inter operabilität sind für die Verpackung von integrierten Schaltkreisen sehr wichtig.IPC-Regeln wie IPC-A-600 und IPC-6012Setzen Sie klare Schritte für gutes Aussehen und Leistung. Die folgende Tabelle zeigt einige wichtige IPC-Regeln und was sie tun:

|

IPC-Standard |

Fokus bereich |

Rolle bei der Validierung der Zuverlässigkeit der IC-Verpackungs technologie |

|---|---|---|

|

IPC-A-600 |

Visuelle Akzeptanz von Leiterplatten |

Stellt sicher, dass nur fehlerfreie PCBs die Inspektion bestehen, was die Zuverlässigkeit der Verpackung unterstützt. |

|

IPC-6012 |

Qualifikation und Leistung von starren PCB |

Definiert Anforderungen an Haltbarkeit und langfristige Zuverlässigkeit. |

|

IPC-A-610 |

Zulässigkeit von elektronischen Baugruppen |

LeitfädenMontageQualität, Löten und Komponenten platzierung. |

|

IPC-2221 |

Generischer Standard für PCB-Design |

Legt Best Practices fest, um Fehler zu reduzieren und die Konsistenz zu verbessern. |

|

IPC-7711/7721 |

Nacharbeit, Modifikation und Reparatur |

Bietet sichere Nacharbeit und Reparatur prozesse, Aufrechterhaltung der Qualität nach Modifikationen. |

Tests sind wichtig, um sicher zustellen, dass Produkte gut zusammenarbeiten:

-

Eingebaute Selbsttest-AlgorithmenProbleme in schnellen Verbindungen finden.

-

Signal integrität monitore überprüfen den Zustand von Chip-Links.

-

Redundanz und Reparatur verwenden zusätzliche Fahrspuren, um die Signale stark zu halten.

-

Hochgeschwindigkeits-Zugangs-und Testfunktionen helfen bei jedem Schritt, Chips zu testen.

-

Umwelt tests überprüfen, wie Chips mit Änderungen in Wärme, Strom und Prozess arbeiten.

Unternehmen verwenden diese Regeln und Tests, um sicher zustellen, dass ihre Produkte stark sind und für wichtige Jobs gut funktionieren.

Trends in der IC-Verpackung

3D-Integration

3D-Integration ist ein großer Trend inIc verpackung. Diese Methode stapelt vieleIcSchichten übereinander. Sie verbinden die Schichten mit speziellen Verbindungen, die als Durch-Silizium-Vias bezeichnet werden. Unternehmen verwenden 3D-Stacking, um Geräte besser funktionieren zu lassen und weniger Strom zu verbrauchen. Es hilft auch, Geräte kleiner zu machen. Die Branche prüft Fortschritte mit Schlüsseln ummern wiePaket, Leistung, Leistung, Profil, Kosten und Zykluszeit. Doug Yu von TSMC hat diese Zahlen erstellt, um neue Ideen zu leiten.

|

Aspekt |

Details |

|---|---|

|

Wichtige Leistungs indikatoren (KPIs) |

Paket, Leistung, Leistung, Profil, Kosten, Zykluszeit (PPPCC) |

|

Adoption herausforderungen |

TSV-Technologie in kosten sensiblen mobilen Anwendungen aufgrund von Kosten-und technischen Problemen nicht weit verbreitet |

|

Die Schließung von Qui monda im Jahr 2008 verzögerte die Einführung des DRAM-Stapels |

|

|

Die Konkurrenz durch fan-out Wafer-Level-Verpackungen (FOWLP) verdrängte die Akzeptanz von 3D-IC |

|

|

Adoption beispiele |

Einige Smartphones verwenden TSV-basierte 3D-ICs, was auf die Serien produktion hinweist |

|

Meilensteine |

SK Hynix führte 2015 3D TSV DRAM Stacks (HBM) ein |

|

3D-Systemintegration über Wafer-zu-Wafer (W2W) und die-zu-Wafer-Stapelung (D2W) voraussicht lich um 2022 |

|

|

Zukünftige Entwicklungen |

Hybrid bindung und Pitch-Skalierung zur Verbesserung der Ausbeute und Leistung beim D2W-Stapeln |

|

Branchen-Roadmap und Experten konsens unterstützen die laufenden Fortschritte bei der 3D-Integration |

Ingenieure arbeiten weiter daran, Kosten und technische Probleme bei der 3D-Integration zu beheben. Hybrid bindung und Pitch-Skalierung können dazu beitragen, mehr Chips herzustellen und die Leistung zu steigern. Viele Smartphones verwenden jetzt 3DIc verpackung, Also ist dieser Trend jetzt üblich. Experten glauben, dass die 3D-Integration weiter zunehmen wird, wenn neue Chip-Designs erscheinen.

Fan-Out und Wafer-Level

Fan-Out-Verpackung auf Wafer-Ebene und Verpackung auf Wafer-Level-Chip-Skala haben sich geändertIc verpackungEine Menge. Diese neuen Typen tragen dazu bei, Geräte kleiner zu machen und mehr Teile zu verpacken. Der Markt für Wafer-Level-Chip-Verpackungen warFast 4,9 Milliarden Dollar im Jahr 2023. Es könnte bis 2031 auf über 37 Milliarden US-Dollar anwachsen. Dieses schnelle Wachstum zeigt, dass viele Unternehmen diese neuen Wege nutzen.

-

Mit dem Fan-In WLCSP können Geräte mit mehr Teilen kleiner und billiger sein.

-

Die fächerbare Verpackung auf Wafer ebene fügt mehr E/A hinzu, indem Drähte außerhalb des Chips verteilt werden. Das hilft bei Hitze und lässt mehr Teile passen.

-

Bessere Pitch-Technologie und neue Materialien tragen dazu bei, mehr gute Chips herzustellen und die Kosten zu senken.

-

Kürzere Verbindungen und eine bessere Wärme kontrolle sorgen dafür, dass Geräte besser funktionieren und länger halten.

📈Branchen einsicht:

Fan-Out-Verpackungen auf Wafer ebene und Verpackungen im Chip-Maßstab auf Wafer ebene tragen dazu bei, Geräte kleiner zu machen und die Chip ausbeute zu verbessern. Auf diese Weise können Unternehmen kleinere, stärkere Geräte für weniger Geld herstellen.

Ingenieure verwenden diese Verpackungs typen für Telefone, Wearables und Auto elektronik. Der Vorstoß für kleinere, bessere Geräte fährt immer wieder neuIc verpackungIdeen.

Heterogene Integration

Heterogene Integration ist jetzt ein Haupt trend inIc verpackung. Auf diese Weise setzt verschiedeneIcTypen, Materialien und Jobs in einem Paket. Ingenieure verwenden Durch-Silizium-Vias, um viele Chips auf einem Substrat zu verbinden. Damit werden alte Größen grenzen gebrochen. Es hilft auch, Systeme billiger zu machen und ermöglicht Chiplet-basierte Systeme.

NeuHeterogene 3D-IntegrationKönnen Chips in sehr kleinen Größen verbinden, sogar bis hin zu Sub mikron. Die Branche verwendet jetzt 3D-Stapeln, Mischen vieler Jobs und Hybrid integration. Diese Änderungen bringen eine hohe Dichte, einen geringeren Strom verbrauch, eine geringere Größe und eine bessere Zuverlässigkeit.

Chiplet-Designs sind für diesen Trend sehr wichtig. Designer können Chiplets für Logik-, Speicher-oder analoge Jobs auswählen. Dies macht System-in-Paket-Lösungen flexibel und schnell zu bauen. Es hilft auch, neue Produkte schneller heraus zubringen und unterstützt neue Ideen in Chips.

💡Tipp:

Heterogene Integration und Chiplet-Designs helfen Ingenieuren, komplexe Systeme schneller und einfacher zu machen. Dieser Trend erfüllt den Bedarf an kleiner, leistungs starker Elektronik.

Fort geschrittene Materialien

Fort geschrittene MaterialienStehen hinter vielen neuen Trends inIc verpackung. Ingenieure wählen Materialien aus, die Wärme gut bewegen, besser mit Elektrizität arbeiten und länger halten. Diese Materialien helfen bei High-PowerIcBedürfnisse. Kupfer verbindungen, Low-k-Dielektrik und neue Substrate ermöglichen neue Verpackungs typen wie 3D-Verpackungen und Verpackungen auf Wafer ebene.

-

Neue Kühl materialien wie Mikro fluid ik kühlung und eingebaute Wärmer ohre halten die Chips kühl und halten länger.

-

Bessere Materialien für die thermische Schnitts telle helfen Chips, mehr Wärme zu verarbeiten.

-

Die heterogene Integration verwendet viele Halbleiter materialien in einem Paket. Dies steigert die Leistung und unterbricht den Strom verbrauch.

-

Die Industrie macht recycelbare und umwelt freundliche Verpackungen, um dem Planeten zu helfen.

-

Die Verpackung muss mit Wärme, Strom, Temperatur änderungen und Signal problemen wie EMI und Übersprechen umgehen.

-

Kleinere Geräte benötigen winzige, komplexe Pakete, die immer noch gut funktionieren und weniger kosten.

Ingenieure suchen immer wieder nach neuen Materialien, um neue Technologien und Chip designs zu unterstützen. Diese Bemühungen stellen sicher, dassIc verpackungHält mit dem Schritt, was moderne Chips brauchen.

🔍Anmerkung:

Die Umstellung auf fortschritt liche Materialien und neue Verpackungs wege wird die Zukunft derIc verpackung. Unternehmen, die an diesen Bereichen arbeiten, werden die nächsten großen Änderungen bei den Chips anführen.

Herausforderungen und Überlegungen

Fertigungs komplexität

Verpackung von integrierten Schaltkreisen hat viele Probleme bei der Herstellung von Produkten. Die Industrie muss viele Schritte und strenge Regeln befolgen. Studien zeigen einige große Probleme bei der Herstellung dieser Produkte:

-

Nicht genug Halbleiter fabrikenBedeutet, dass weniger Chips hergestellt werden. Dies verlangsamt neue Technologie.

-

Wenn Sie sich auf Teile aus anderen Ländern konzentrieren, kann dies zu Problemen in der Lieferkette führen.

-

Harte Regierungs regeln machen es schwierig, neue Fabriken zu bauen. Dies verlangsamt den Markt.

Diese Dinge machen es schwieriger, mehr Verpackungen herzustellen. Unternehmen müssen bessere Maschinen kaufen und Fachkräfte einstellen. Für diese Arbeit werden Rein räume und Spezial werkzeuge benötigt. Wenn die Verpackung besser wird, muss jeder Schritt höheren Standards entsprechen.

Prüfung und Zuverlässigkeit

Prüfung und Zuverlässigkeit sind in der Verpackung sehr wichtig. Unternehmen nutzen neue Qualitäts kontroll systeme, um bessere Ergebnisse zu erzielen. Zum Beispiel:

-

Ein Unternehmen in Taiwan testete eineNeues Echtzeit-Qualitäts kontroll system.

-

Das System verwendet spezielle Methoden, um die besten Einstellungen zu finden.

-

Dies hilft, bessere Produkte und weniger Fehler zu machen.

-

Qualitäts prüfungen zeigen, wie gut Schaltkreis sonden tests funktionieren.

-

Das System hilft intelligenten Fabriken, vor der Verpackung hohe Standards einzuhalten.

Diese Möglichkeiten helfen Unternehmen, Probleme frühzeitig zu finden und sicher zustellen, dass Produkte gut funktionieren. Wenn die Chips kleiner werden, müssen die Tests noch vorsichtiger sein.

Kosten und Skalierbar keit

Kosten und Skalierbar keit sind große Sorgen bei der Verpackung. Neue Verpackungen brauchen teure Materialien und Maschinen. Unternehmen müssen neue Dinge ausprobieren, aber auch die Preise niedrig halten. Mehr Produkte zu machen kann Geld und Ressourcen verbrauchen. Kleine Unternehmen haben möglicher weise Probleme, mit größeren zu konkurrieren. Die Branche sucht nach Möglichkeiten, Geld zu sparen, aber dennoch gute Produkte herzustellen und die Nachfrage zu befriedigen.

Zusammenarbeit im Ökosystem

Die Zusammenarbeit mit Ökosystemen hilft der Verpackung, voran zukommen. Ein Unternehmen kann nicht alles alleine machen. Die Zusammenarbeit mit Lieferanten und Geräte herstellern hilft dabei, neue Ideen zu entwickeln. Regeln teilen und offen reden macht es einfacher, Probleme zu beheben und schneller zu arbeiten. Teamwork hilft auch bei Problemen mit der Lieferkette und sorgt dafür, dass Teile kommen.

💡Gute Teamarbeit im Ökosystem bringt schnellere Fortschritte und bessere Verpackungs lösungen.

Die Verpackung integrierter Schaltkreise ist für Halbleiter immer noch sehr wichtig. Die folgende Tabelle zeigt, wie Verpackungen der Branche helfen, zu wachsen und sich zu verändern:

|

Metrik/Trend |

Details |

|---|---|

|

~ 697 Milliarden US-Dollar |

|

|

Markt wachstums rate (2025-2030) |

7%-9% jährlich |

|

Schlüssel technologien |

3D-Stapel-Verpackung, System-in-Package-Verpackung auf Wafer-Ebene |

Menschen, die Verpackungs trends beobachten, können mit neuen Bedürfnissen Schritt halten. Sie können auch helfen, neue Technologien zu führen. Die Verpackung bleibt wichtig für eine bessere Leistung und neue Anwendungen in der Zukunft.

FAQ

Was ist eine Verpackung mit integrierten Schaltkreisen und warum ist sie wichtig?

Integrierte Schaltung Verpackung hält Chips sicher vor Schaden. Es verbindet Chips mit anderen Teilen in einem Gerät. Es hilft auch, Wärme vom Chip weg zu bewegen. Dadurch funktionieren Geräte besser und halten länger. Ingenieure verwenden Verpackungen, um Elektronik stärker und schneller zu machen.

Wie verbessern fortschritt liche Verpackungs technologien die Halbleiter leistung?

Fortschritt liche Verpackungs technologien verkürzen die Verbindungen. Dies hilft, Signale schneller und besser zu bewegen. Auf diese Weise passen mehr Teile auf kleinem Raum. Geräte können schneller laufen und weniger Strom verbrauchen. Dadurch funktioniert die Elektronik gut und spart Energie.

Was sind Chiplet-basierte Designs und warum sind sie beliebt?

Chiplet-basierte Designs verwenden kleine Blöcke, die als Chiplets bezeichnet werden. Ingenieure können verschiedene Chiplets in einem Paket mischen. Dies hilft, neue Geräte schneller zu machen. Mit Chiplet-Designs können Unternehmen Teile von anderen verwenden. Universal Chiplet Interconnect Express hilft dabei, Chiplets miteinander zu verbinden.

Welche Standards leiten die Verpackungs-und Herstellungs prozesse von ic?

JEDEC und IPC legen Regeln für die Verpackung und Prüfung von ic fest. Diese Regeln helfen Unternehmen, gute und sichere Produkte herzustellen. Sie helfen auch verschiedenen Unternehmen bei der Zusammenarbeit. Die Regeln unterstützen neue Möglichkeiten zur Herstellung und Prüfung von ic-Verpackungen.

Welche Trends prägen die Zukunft der ic-Verpackung?

Zu den Trends gehören 3D-Stapeln, Chiplets ysteme und neue Materialien. Ingenieure verwenden diese, um kleinere und schnellere Geräte herzustellen. Die Industrie arbeitet auch an grünen Verpackungen, um dem Planeten zu helfen. Neue Ideen helfen der Elektronik, besser zu arbeiten und länger zu halten.