Was bestimmt SPI-Geschwindigkeit Eine vollständige Anleitung

Die serielle periphere Schnitts telle (SPI) ist berühmt für die Hoch geschwindigkeit daten übertragung. Dieses synchrone Kommunikation protokoll ermöglichen

DieSerielle periphere Schnitts telle(SPI) Ist berühmt fürHochgeschwindigkeits-Daten übertragung. DieseSynchrones Kommunikation protokollErmöglicht effiziente DatenTransferZwischenGeräte, Mit einigenDaten übertragungs raten Mehr als 100 MHz. Also, warum ist dein Projekt nichtLeistungImmer diese top getroffenDaten übertragungs raten? Deine wahreSPI-GeschwindigkeitUnd insgesamtDurchsatzSind durch drei Schlüssel bereiche begrenzt.

💡Das FinaleLeistungVon jedemSPIDatenTransferIst ein Gleichgewicht IhrerGeräte'Hardware-Limits, die physische Verbindungs qualität und Ihre Software-Konfiguration.

Wichtige Imbiss buden

- Ihre SPI-Geschwindigkeit hängt von drei wichtigen Dingen ab: den Hardware-Limits Ihrer Geräte, der Qualität Ihrer physischen Verbindungen und der Art und Weise, wie Sie Ihre Software einrichten.

- Überprüfen Sie immer die Geschwindigkeit begrenzungen in den Datenblättern für Ihre Master-und Slave-Geräte. Das langsamste Gerät stellt die Höchst geschwindigkeit für Ihren SPI-Bus ein.

- Gutes PCB-Design ist wichtig. Halten Sie die Drähte kurz, passen Sie die Spuren längen an und verwenden Sie eine starke Erdung ebene, um Signal probleme bei hohen Geschwindigkeiten zu vermeiden.

- Verwenden Sie DirectGedächtnisZugriff (DMA) in Ihrer Software für die beste Leistung. DMA lässt IhreMikro controllerSenden Sie Daten schnell, ohne den Hauptprozessor zu verlangsamen.

Die Rolle der Hardware in der SPI-Geschwindigkeit

Der erste Schritt, um die maximale SPI-Geschwindigkeit Ihres Systems zu verstehen, besteht darin, die Hardware selbst zu betrachten. Bevor Sie überhaupt eine Code zeile schreiben oder eine Leiterplatte entwerfen, legen die Datenblätter für Ihre Master-und Slave-Geräte eine harte Obergrenze fest. Ihre Abschluss leistung ist grunds ätzlich an die Fähigkeiten dieser gebundenIntegrierte Schaltungen.

Master Clock Limits

Ihr Haupt gerät, normaler weise ein Mikro controller, erzeugt den SPI-Takt (SCK). Dieses Gerät hat eine maximale Frequenz, mit der es seineSerielle Peripherie schnitts telle. Diese Grenze finden Sie in derAbschnitt für elektrische Eigenschaften seines Datenblattes. Die Tabellen geben oft das Maximum anFSCK(SPI-Taktfrequenz) unter verschiedenen Betriebs spannungen.

Beispiels weise kann das Datenblatt eines Mikro controllers seine SPI-Eigenschaften folgender maßen aufweisen:

| Symbol | Parameter | Bedingungen | Min | Typ | Max | Einheit |

|---|---|---|---|---|---|---|

| FSCK | SPI Taktfrequenz | Controller-Empfänger-Modus 2,7 V <VDD <3,6 V | - | - | 45 | MHz |

| Controller-Sender-Modus 2,7 V <VDD <3,6 V | - | - | 45 | MHz |

Anmerkung:Die Werte in der obigen Tabelle basieren auf

FPCLKx/3, WoFPCLKxIst die periphere Uhr. Der tatsächliche Maximalwert hängt von der spezifischen Architektur des Mikro controllers ab.

Auch die meister eigene System uhr spielt eine Rolle. Das SPI-Peripherie gerät läuft häufig auf einer Uhr, die von der Haupt system uhr abgeleitet ist.

- Die interne Takt architektur eines Mikro controllers kann den Eingangs takt des SPI-Moduls einschränken. Beispiels weise akzeptiert ein Modul möglicher weise nur eine maximale Eingabe von48 MHz.

- Dieser Eingangs takt wird dann aufgeteilt, um das endgültige SCK-Signal für die SPI-Übertragung zu erzeugen.

- Dies bedeutet, dass selbst wenn das SPI-Peripherie gerät theoretisch schneller laufen kann, seine Leistung durch die Uhr begrenzt wird, die Sie es einspeisen.

Einschränkungen der Sklaven uhr

Betrachten Sie nun das Slave-Gerät. Jeder SPI-Sklave, ob es einSensor, Speicherchip oder ein anderer Mikro controller hat ebenfalls eine maximale Taktfrequenz, die er verarbeiten kann. Dies ist häufig der bedeutendste Engpass in einer Master-/Slave-Konfiguration.Wenn Sie diese Grenze überschreiten, wird der Slave Daten falsch interpretieren, was zu einer Daten beschädigung während der Übertragung führt.

💡Ihr SPI-Bus ist nur so schnell wie sein langsamstes Gerät. Die endgültige Kommunikation geschwindigkeit muss auf das untere der beiden Höchstwerte (Master oder Slave) eingestellt werden.

Sie müssen das Datenblatt des Sklaven sorgfältig prüfen. Je nach Operation finden Sie möglicher weise unterschied liche maximale Daten übertragungs raten. Zum Beispiel einDer Mikro controller STM32 im Slave-Modus unterstützt möglicher weise 40 MHz für den Empfang von Daten, aber eine niedrigere Geschwindigkeit wie 24 MHz für die Vollduplex-Kommunikation. Diese Unterschiede können sich aus der internen Logik ergeben, die zum Abtasten und Senden von Daten gleichzeitig erforderlich ist. Für die meisten SPI-Slave-Geräte besteht eine sichere Faustregel darin, die SPI-Taktrate unterEin Zehntel der eigenen System taktfrequenz des SklavenUm eine zuverlässige Daten übertragung zu gewährleisten.

Verzögerungen bei der Sklaven verarbeitung

Eine hohe Taktfrequenz entspricht nicht immer einem hohen Durchsatz. Das wahre Maß für die Leistung ist, wie viele Daten Sie im Laufe der Zeit übertragen können. Viele Slave-Geräte benötigen eine Pause zwischen Transaktionen, um Informationen zu verarbeiten. Dies ist bekannt alsSlave verarbeitung szeitOderVerzögerung zwischen Transaktionen.

Stellen Sie sich vor, Sie senden einen Befehl an einen Sensor. Der Sensor benötigt Zeit, um eine Messung durch zuführen, bevor er Daten für die nächste Übertragung bereit hält. Eine schnelle SPI-Uhr ist nutzlos, wenn der Master lange warten muss, bis der Slave bereit ist. Diese Verzögerung wirkt sich dramatisch auf Ihren gesamten Daten durchsatz aus.

Einige häufige Szenarien, die diese Verzögerung erfordern, umfassen:

| Szenario | Warum eine Verzögerung erforderlich ist |

|---|---|

| Sklave hat langsame interne Logik | Das Gerät benötigt Zeit, um das vorherige Daten byte zu verarbeiten. |

| Multi-Frame-SPI-Protokolle | Das Protokoll selbst erfordert eine bestimmte Zeit lücke zwischen Frames. |

| SPI Flash-Seite schreibt | Der Speicherchip muss anhalten, um eine Adresse zu verriegeln, bevor Daten geschrieben werden. |

| Timing-Fehler vermeiden | Eine kleine Verzögerung kann dazu beitragen, Fehler bei sehr hohen SPI-Taktgeschwindigkeiten zu vermeiden. |

Woher wissen Sie, wann der Sklave für den nächsten Transfer bereit ist? Geräte verwenden mehrere Methoden, um ihren Status zu signalisieren:

- Beschäftigter Pin:Einige Geräte verfügen über einen dedizierten Ausgangs pin, von dem sie behaupten, dass sie mit der Verarbeitung beschäftigt sind.

- Status register:Sie können ein Status register auf dem Slave abfragen. Dieses Register enthält oft Bits wie

Trdy(Senden bereit) oderRrdy(Bereit empfangen), um seinen Zustand anzugeben. - Unterbricht:Der Slave kann diese Status bits verwenden, um einen Interrupt auf dem Master auszulösen und aktiv zu signalisieren, dass er für die nächste SPI-Transaktion bereit ist.

Die serielle periphere Schnitts telle physikalische Schicht

Sobald Sie die Grenzen IhrerIntegrierte SchaltungenMüssen Sie sich die physischen Verbindungen zwischen ihnen ansehen. Die Leiterplatte spuren und Drähte, die Ihren SPI-Bus bilden, sind keine perfekten Leiter. Bei hohen Frequenzen stellen diese physischen Pfade ihre eigenen Herausforderungen vor, die die Signal qualität beeinträchtigen und Ihre Gesamt leistung einschränken können.

Signalweg und Layout

Lange Drähte und PCB-Spuren können wie winzige Antennen wirken. Dieses Verhalten führt zu einer Ausbreitung verzögerung. Dies ist die Zeit, die ein Signal benötigt, um vom Master zu den Slave-Geräten zu gelangen. Bei niedrigen Geschwindigkeiten ist diese Verzögerung verna ch lässig bar. Bei hohen Daten übertragungs raten wird es zu einem großen Problem.

Fehl paarungen in der Spuren länge zwischen den Taktlinien (SCK) und Daten (MOSI/MISO) verursachen Zeitfehler. Das Taktsignal kann zu einem anderen Zeitpunkt als die Daten beim Empfänger ankommen. Dies kann dazu führen, dass das Slave-Gerät das falsche Daten bit verriegelt und die gesamte Übertragung beschädigt. Mit zunehmender Signal frequenz wird die Taktzeit kürzer, wodurch Ihr Design selbst für kleine Unterschiede in der Ausbreitung verzögerung viel empfindlicher wird.

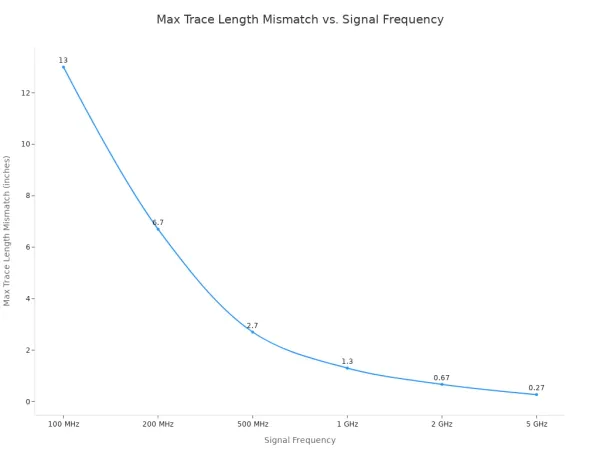

Die folgende Tabelle zeigt, wie schnell die Toleranz für Nicht übereinstimmung der Spuren länge mit steigender SPI-Taktfrequenz schrumpft.

| Signal frequenz | Zeit der Uhr (T) | Max Schräg toleranz (20% T) | Ausbreitung verzögerung (FR4) | Max Spuren länge Nicht übereinstimmung |

|---|---|---|---|---|

| 100 MHz | 10 ns | 2 ns | ~ 150 ps/in | ~ 13 in |

| 200 MHz | 5 ns | 1 ns | ~ 150 ps/in | ~ 6,7 in |

| 500 MHz | 2 ns | 0.4 ns | ~ 150 ps/in | ~ 2,7 in |

| 1 GHz | 1 ns | 0.2 ns | ~ 150 ps/in | ~ 1,3 in |

| 2 GHz | 0,5 ns | 0,1 ns | ~ 150 ps/in | ~ 0,67 in |

| 5 GHz | 0.2 ns | 0,04 ns | ~ 150 ps/in | ~ 0,27 in |

Pro-Tipp:Wenn Ihr SPI-Bus im Bereich von 50-100 MHz arbeitet, sollten Sie die Spuren als Übertragungs leitungen behandeln. Um Signal reflexionen und Klingeln zu verhindern, können Sie eine Kleinserien-Terminierung hinzufügenWiderstände(Z. B. 22-33Ω) in der Nähe der Treibers tifte. Platzieren Sie sie auf den SCK-, MOSI-und CS-Linien am Master und auf der MISO-Linie bei jedem Slave.

Bus kapazität und Integrität

Jedes Element auf Ihrer Leiterplatte, von derIC-StifteZu den Spuren selbst, fügt eine kleine Menge unerwünschter Kapazität hinzu. Das nennt manParasitäre Kapazität. Es existiert zwischen der Signals pur und ihrer nächsten Referenz ebene, normaler weise der Erdung ebene. Obwohl Sie es nicht beseitigen können, müssen Sie es verwalten.

Diese Kapazität wirkt sich direkt auf die Anstiegs zeit Ihres Signals aus. Die Anstiegs zeit ist, wie schnell das Signal von einer niedrigen Spannung zu einer hohen Spannung übergehen kann.Hohe Bus kapazität wirkt wie eine Hürde und wider setzt sich der Anstiegs fähigkeit des Signals. Dies verlangsamt die Anstiegs zeit und rundet die scharfen Kanten Ihres Taktsignals ab. Wenn die Takt kante zu langsam wird, kann das Slave-Gerät sie möglicher weise nicht richtig registrieren, wodurch Ihre maximale Taktrate begrenzt wird. Interessanter weise,Die Kapazität wirkt sich viel geringer auf die Herbstzeit des Signals aus.

Das Hinzufügen weiterer Slave-Geräte zum SPI-Bus erhöht die Gesamt last kapazität, wodurch die Signal integrität weiter beeint rächt igt werden kann. Sie können diesen parasitären Effekt durch sorgfältiges PCB-Design steuern.

- Verwenden Sie dünnere Oberflächen schicht laminateUm den Abstand zur angrenzenden Boden ebene zu verringern.

- Wählen Sie Materialien mit niedriger Dk (Diele ktrizitäts konstante)Für Ihre Leiterplatte, um die Gesamt kapazität zu senken.

- Wählen Sie Komponenten mit kleineren Blei größen ausUm ihren Beitrag zu minimieren.

Übersprechen und Lärm

Übersprechen geschieht, wenn die elektro magnetische Energie einer Signals pur in eine benachbarte Spur "leckt". Auf einer Leiterplatte tritt dies häufig zwischen zwei nebeneinander verlaufenden SPI-Spuren auf. Diese gekoppelte Energie erzeugt Lärm auf der "Opfer"-Spur. Wenn das Rauschen groß genug ist, kann es zu falschen Signal übergängen führen und Ihre Daten übertragung beschädigen.

Dieses Phänomen ist haupt sächlich auf die kapazitive Kopplung zurück zuführen. Der beste Weg, um Übersprechen und andere äußere Geräusche zu bekämpfen, ist eine gut gestaltete Boden ebene.

Eine feste Erdung ebene bietet einen Rückweg mit niedriger Impedanz für Signals tröme. Dies strafft die elektro magnetischen Felder um die Signals pur, enthält sie und verhindert, dass sie andere Signale stören.Eine engere Referenz ebene führt zu einer engeren Kopplung und weniger Lärm.

Um Ihr Design zu verbessern und höhere Daten übertragungs raten zu erreichen, sollten Sie:

- Maximieren Sie Ihre Boden ebene:Nutzen Sie für die Boden ebene so viel freien Platz wie möglich auf der Leiterplatte.

- Verwenden Sie dedizierte Bodenschichten:Bei mehr schicht igen Brettern bietet eine dedizierte Boden ebene eine hervorragende Trennung und reduziert Geräusche.

- Fügen Sie Nähte Vias hinzu:Wenn Sie eine Grundfläche teilen müssen, verwenden Sie Vias, um die einzelnen Bereiche zusammen zunähen und einen kontinuier lichen Pfad mit niedriger Impedanz zu erstellen.

Durch die sorgfältige Verwaltung Ihres PCB-Layouts, Ihrer Kapazität und Ihrer Erdung können Sie die Signal integrität erhalten. Auf diese Weise können Sie Ihren SPI-Bus mit einer höheren Spi-Geschwindigkeit betreiben und einen besseren Gesamt durchsatz erzielen.

Auswirkungen der Software auf die SPI-Leistung

Ihre Hardware undPCB-LayoutLegen Sie das Potenzial für Hoch geschwindigkeit kommunikation fest, aber Ihre Software bestimmt, ob Sie es tatsächlich erreichen können. Die Auswahl, die Sie in Ihrem Code treffen, von den grundlegenden Protokoll einstellungen bis hin zu den Daten verarbeitung methoden, steuern direkt Ihre endgültige SPI-Leistung und den Durchsatz.

SPI-Modus und Timing

DieSPI-ProtokollIst synchron, was bedeutet, dass sich die Master-und Slave-Geräte auf das Timing einigen müssen. Sie konfigurieren dieses Timing, indem Sie den richtigen SPI-Modus auswählen. Ein Miss verhältnis hier führt dazu, dass die Übertragung vollständig fehlschlägt. Der Modus wird durch zwei Parameter im Datenblatt des Slave-Geräts definiert:

- Uhr polarität (CPOL):Dies stellt den Leerlauf zustand des Taktsignals (niedrig oder hoch) ein.

- Uhr phase (CPHA):Dies bestimmt, ob Daten an der ersten (führenden) oder zweiten (nachlaufen den) Takt kante abgetastet werden.

Diese beiden Einstellungen werden kombiniert, um vier mögliche SPI-Modi zu erstellen. Wenn Ihr Master auf Modus 0 eingestellt ist (CPOL = 0, CPHA = 0), wird erwartet, dass Daten auf einer steigenden Takt kante abgetastet werden. Ihr Slave-Gerät muss auch für diesen Modus konfiguriert sein, um eine erfolgreiche Daten übertragung sicher zustellen. Wenn Sie dies falsch machen, ist dies eine häufige Fehler quelle, die die Kommunikation zwischen Geräten verhindert.

Treiber und OS Overhead

Wie Ihr Mikro controller Daten bewegt, hat einen großen Einfluss auf die Leistung. Für die Abwicklung einer SPI-Übertragung haben Sie im Allgemeinen zwei Möglichkeiten: Interrupts oder Direct Memory Access (DMA). Die Verwendung von Interrupts ist für eine grundlegende Übertragung einfacher, erzeugt jedoch einen erheblichen CPU-Overhead, der Ihre maximalen Daten übertragungs raten begrenzt. Für hohe Leistung ist DMA die überlegene Methode.

💡Mit DMA kann das SPI-Peripherie gerät Daten direkt zum oder vom Speicher übertragen, ohne die CPU einzu beziehen. Dadurch kann die CPU andere Aufgaben ausführen, was die Effizienz Ihres Systems dramatisch erhöht und eine höhere Datenrate ermöglicht.

Die folgende Tabelle vergleicht die beiden Ansätze:

| Feature | Interrupt-getriebene SPI | DMA-getriebene SPI |

|---|---|---|

| CPU Overhead | Hoch; CPU verwaltet jede Byte übertragung. | Niedrig; Die CPU ist nach dem Start der Übertragung frei. |

| Durchsatz | Niedriger; Begrenzt durch die Fähigkeit der CPU, Interrupts zu bedienen. | Höher; Kann die maximale SPI-Geschwindigkeit erreichen. |

| Anwendungs fälle | Gut für niedrige RateSensorenOder einfache Befehle. | Ideal für High-Speed-Streaming und große Daten blöcke. |

Wenn Sie die höchsten Daten übertragungs raten von Komponenten wie hoch auflösenden ADCs oder Flash-Speicher erreichen müssen, sollten Sie DMA verwenden. Dieser Ansatz minimiert Software verzögerungen und ermöglicht es Ihrem SPI-Bus, näher an seinen Hardware-Grenzen zu arbeiten.

Ihre endgültige SPI-Geschwindigkeit hängt von drei Schlüssel faktoren ab. Dies sind die Grenzen Ihrer Hardware, Ihre physischen Verbindungen und die Effizienz Ihrer Software. Sie müssen alle drei Bereiche berücksichtigen, um die hohen Daten übertragungs raten zu erreichen, für die SPI bekannt ist. Ein schnelles System erfordert einen vollständigen Ansatz.

💡Takeaway umsetzbar:Um Ihre wahre Höchst geschwindigkeit zu ermitteln, überprüfen Sie zunächst das Datenblatt des Slave-Geräts auf seine Geschwindigkeit begrenzung. Als nächstes testen Sie diese Geschwindigkeit mit Ihrem PCB-Layout und Software. Stellen Sie von dort aus nach unten ein, um die schnellste stabile Rate für Ihr spezifisches Projekt zu finden.