Emballage de circuits intégrés: technologies, normes et tendances futures

L'emballage de circuits intégrés aide à décider comment les semi-conducteurs fonctionneront à l'avenir. Les ingénieurs utilisent l'emballage pour améliorer le fonctionnement des semi-conducteurs. Cela permet également de rendre les appareils plus petits et plus rapides.

L'emballage de circuits intégrés aide à décider comment les semi-conducteurs fonctionneront à l'avenir. Les ingénieurs utilisent l'emballage pour améliorer le fonctionnement des semi-conducteurs. Cela permet également de rendre les appareils plus petits et plus rapides. L'industrie a commencé avec un simple emballage de circuits intégrés. Maintenant, il utilise des solutions avancées pour des systèmes plus complexes. Ces solutions aident également à mélanger différents types de pièces. L'emballage est maintenant très important pour améliorer les semi-conducteurs. Les gens qui regardent les changements d'emballage peuvent aider à créer de nouvelles idées.

Les clés à emporter

-

L'emballage de circuit intégré maintient des puces sûres. Il relie différentes parties ensemble. Cela aide également les appareils à devenir plus petits et plus rapides. Cela les rend plus efficaces et durent plus longtemps.

-

Des méthodes d'emballage avancées telles que l'empilement 3D, l'emballage au niveau de la plaquette en éventail et les conceptions de chiplet améliorent le fonctionnement. Ils utilisent moins de puissance. Ils aident également à construire des systèmes plus complexes.

-

Les normes de l'industrie de JEDEC et IPC s'assurent que l'emballage et l'essai sont bons. Ils aident à garder les choses en sécurité et à s'assurer que les pièces fonctionnent ensemble.

-

De nouveaux matériaux et technologies de refroidissement aident à contrôler la chaleur. Ils permettent également aux boîtiers semi-conducteurs modernes de durer plus longtemps.

-

Les entreprises travaillent ensemble et continuent d'inventer de nouvelles choses. Cela aide à résoudre les problèmes dans la fabrication de puces. Il contribue également à améliorer l'emballage à l'avenir.

Aperçu des emballages de circuits intégrés

But et fonctions

Emballage de circuits intégrésEst très important pour le bon fonctionnement de l'électronique. Les ingénieurs utilisentEmballage d'icPour mettre des puces et d'autres pièces ensemble. Cela fait un système complet. Cela aide à rendre les choses plus petites et les permet de travailler plus rapidement. Les petites pièces comme 0201 et 01005 montrent commentEmballage d'icRétrécit les appareils mais ajoute plus de fonctionnalités.

Certains emplois principaux deEmballage d'icSont:

-

Soutien aux circuits et autres pièces

-

Faire des chemins électriques pour des signaux et des données rapides

-

Manipulation de la chaleur avec des outils de refroidissement comme les micro heatpipes

-

Garder leIcÀ l'abri des dommages et de l'environnement

-

Aider à empiler les pièces en 3D avec System on Package et Package on Package

-

Faire durer les choses plus longtemps avec des tests solides et de nouveaux matériaux

Les ingénieurs recherchent de nouveaux matériaux, commeNanotubes de carbone, Pour faireEmballage d'icMieux. Le substrat dansEmballage d'icEst également essentiel pour rendre les choses plus petites et mieux fonctionner.

Evolution de l'emballage IC

L'histoire deEmballage d'icMontre à quelle vitesse les semi-conducteurs ont changé. Dans les années 1970, les modules multi-puces ont commencé à mélanger différentes parties. VieuxEmballage d'icManières changées en nouvelles qui mettent la logique,Mémoire,CapteursAntennes ensemble. La loi de Moore ne pouvait pas suivre juste la 2D, ainsi l'industrie s'est déplacée aux pièces 3D d'empilement et de mélange.

Nouvelles idées comme vias à travers-silicium, interposeurs, etEmballage de niveau de gaufrette de fan-outChangéEmballage d'ic. Ceux-ci permettent aux appareils de mieux fonctionner, de devenir plus petits et de faire plus. Désormais, l'appareil, le package et la conception de PCB fonctionnent ensemble pour des solutions personnalisées dans l'informatique haute vitesse et l'IoT. Ce changement montre commentEmballage de circuit intégréSont passés de simples boîtes à systèmes complexes avec de nombreuses technologies.

Aperçu de l'industrie:

Statistique clé

Détails

Taille du marché (2024)

Taille projetée du marché (2033)

90,18 milliards de dollars

TCAC (2025-2033)

9,35%

Le plus grand marché régional

Asie-Pacifique

Région à la croissance la plus rapide

Amérique du Nord

Type dominant Segment

Substrats organiques

Segment d'utilisateur final dominant

Electronique grand public

Technologies clés de l'emballage

SOP, DFN, GA, FOWLP

Les moteurs du marché

Demande pour l'électronique grand public, la 5G, les innovations d'emballage

Principaux acteurs du marché

Amkor, groupe ASE, Henkel, Hitachi Chemical, Bakélite Sumitomo, LG Chem, Powertech, Toray

Tendances notables

Adoption de FOWLP pour la performance et la miniaturisation

Faits saillants régionaux

L'industrie chinoise a augmenté de 18,5% en 2023; Les États-Unis mènent l'Amérique du Nord avec 75% de part

Facteurs stratégiques

R & D, collaborations, initiatives gouvernementales

Technologies d'emballage IC

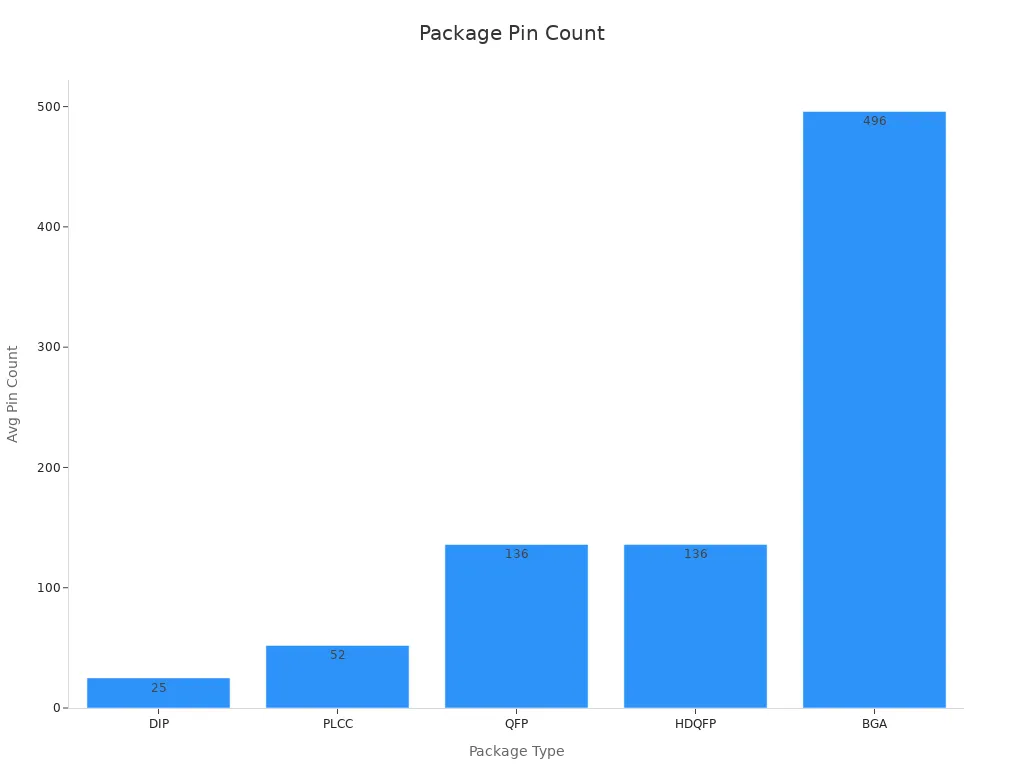

Les forfaits traditionnels

Les ingénieurs ont utilisé des méthodes traditionnellesEmballage d'icDepuis de nombreuses années. Ces paquets aident à protéger et connecter les puces. Quelques types communs sont le double paquet intégré (DIP), transporteur plombé en plastique de puce (PLCC), et paquet plat de quadruple (QFP). Chaque type fonctionne mieux pour certains appareils.

-

DIP a deux rangées de broches. Il peut avoir 8 à 42 broches.Les broches sont espacées de 1,778 à 2,54mm. DIP est bon pour le montage à travers le trou. Les DIP en céramique sont très fiables.

-

PLCC a des avances en forme de J. Il peut avoir 20 à 84 broches. Le PLCC économise de l'espace et peut être monté sur des surfaces ou dans des douilles.

-

QFP a des pistes de mouette. Il peut avoir 32 à 240 broches. L'espacement des broches peut être aussi petit que 0,4mm. QFP a des coussinets exposés pour aider à la chaleur.

Ces traditionnellesEmballage d'icLes types sont mûrs et coûtent moins cher. Ils fonctionnent bien pour de nombreuses utilisations. Mais ils ont des limites en nombre de broches, en taille et en performance. À mesure que les appareils deviennent plus petits et plus complexes, les ingénieurs ont besoin de nouvelles façons d'emballer les puces.

Remarque:TraditionnelEmballage d'icUtilise des connexions plus longues. Cela peut entraîner une perte de signal plus importante et une densité plus faible.

|

Type de paquet |

Gamme de compte de goupille |

Gamme de lancement (mm) |

Dimensions du corps (mm) |

Gamme d'épaisseur (mm) |

Principaux faits saillants du rendement |

|---|---|---|---|---|---|

|

DIP |

8 à 42 |

1,778-2,54 |

Largeur: 6. 35-13. 97 |

0,81-12,96 |

Montage à trous traversés, peu coûteux, versions en céramique pour une fiabilité élevée |

|

PLCC |

20 à 84 |

1.27 |

Largeur/Longueur: 9-29. 28 |

3, 56-4, 57 |

J-conduit, bâti de surface ou de prise, forme espace-efficace d'avance |

|

QFP |

32 à 240 |

0. 4-0. 8 |

Largeur/longueur: 5-45. 7 |

1 à 4,9 |

Cordons de Mouette-aile, bâti extérieur, versions en céramique pour la fiabilité élevée, protections exposées pour le naufrage de la chaleur |

Solutions avancées

L'emballage avancé a changé la façon dont les ingénieurs conçoiventEmballage d'ic. Ces nouvelles méthodes incluent Ball Grid Array (BGA), Chip Scale Package (CSP), Wafer-Level Package (WLP), Fan-Out Wafer-Level Package (FOWLP) et System-in-Package (SiP). Ceux-ci aident à raccourcir les connexions, à ajouter plus de broches et à améliorer les signaux.

-

BGA utilise des billes de soudure au lieu de pistes. Il peut avoir jusqu'à 975 broches. BGA donne une meilleure performance thermique et électrique.

-

CSP et WLP rendent le paquet presque aussi petit que la puce. Cela aide à rendre les appareils encore plus petits.

-

FOWLP permet à plus de pièces de s'adapter dans un seul paquet. Il aide également à la chaleur.

-

SiP met différentIcTypes, comme la logique, la mémoire, et rf, ensemble. Cela aide à fabriquer des appareils complexes.

Les ingénieurs utilisent ces méthodes avancées pour obtenir des données rapides, une petite taille et un meilleur contrôle de la chaleur. Ces méthodes réduisent également les interférences et rendent les appareils plus fiables.Liaison de puce de renverser et vias d'à travers-silicium (TSVs)Faire de minuscules connexions. Ces fonctionnalités aident les signaux et réduisent les effets indésirables.

-

Dans les smartphones, avancéEmballage d'icRassemble processeurs, mémoire et modules RF. Cela rend les téléphones puissants et petits.

-

Dans les voitures, les modules SiP puissants aident l'électronique à fonctionner dans les endroits difficiles.

-

Dans les centres de données, les processeurs rapides utilisent un emballage avancé pour une meilleure vitesse et moins de puissance.

Astuce:AvancéEmballage d'icPermet aux puces d'empiler et d'utiliser des connexions plus courtes. Cela signifie des vitesses plus rapides, moins de retard et de meilleures performances.

Emballage de 3D IC

3DEmballage d'icEst une grande étape dans la technologie de puce. Cette méthode empileIcDes couches les unes sur les autres. Il utilise des choses comme les vias à travers le silicium et les interposeurs de silicium. Les ingénieurs utilisent la 3DEmballage d'icPour une densité plus élevée, de meilleurs signaux et moins de consommation d'énergie.

-

En 2024,Plus de 42 milliards d'unités de filière empilées en 3D expédiées. Cela montre que beaucoup de gens utilisent la 3DEmballage d'icMaintenant.

-

Les packages 3D peuvent avoir jusqu'à 2 300 connexions par cm².

-

FOWLP a la résistance thermique aussi basse que 0.6 °C/W. Cela aide avec la chaleur.

-

L'emballage empilé en 3D représente désormais 28% des revenus des puces logiques.

|

Métrique/Tendance |

Valeur/Statistique |

Description |

|---|---|---|

|

Unités de matrices empilées en 3D expédiées (2024) |

Plus de 42 milliards |

Adoption rapide de l'emballage 3D IC |

|

Densité d'interconnexion dans les boîtiers 3D |

2 300 I/Os par cm² |

Densité d'intégration accrue |

|

Résistance thermique dans FOWLP |

0,6 °C/W |

Performance thermique améliorée |

|

Part des revenus des emballages empilés en 3D |

28% du chiffre d'affaires total de la puce logique |

Importante contribution du marché |

|

Accélérateurs d'IA utilisant un emballage avancé |

Plus de 72% (2024) |

Une forte adoption dans les segments de performance |

|

Amélioration de l'intégrité du signal (FO-PLP) |

30% mieux que FO-WLP |

Qualité de signal améliorée |

|

Réduction d'inductance parasite |

Diminution de 24% |

Gains de performance électrique |

|

Amélioration de la résistance TSV |

19% mieux |

Progrès dans la technologie d'interconnexion verticale |

|

Économies d'énergie via l'emballage chiplet |

18% d'économies moyennes |

Gains d'efficacité énergétique |

|

Die niveaux d'empilage dans DRAM commerciale |

Jusqu'à 8 couches |

Avancement de l'intégration verticale |

Les ingénieurs utilisent des conceptions de chiplet pour construire des systèmes complexes avec de petits blocs réutilisables. L'emballage chiplet leur permet de mélanger différentes fonctions, comme la logique, la mémoire et l'analogique, dans un seul SiP. Cela aide les conceptions de chiplet tiers et rend les produits plus rapides à développer.

-

L'emballage de chiplet rend les connexions plus courtes et les signaux meilleurs.

-

La technologie incorporée de matrice coupe le retard de 22% et économise jusqu'à 18% de puissance.

-

Le lancement de bosse de puce de secousse est maintenant environ le µm 80 dans sub-5nm conceptions. Cela aide à rendre les choses plus petites.

Remarque:Le marché de l'emballage avancé était de 70,3 milliards de dollars en 2024. Il a augmenté de 13,2% chaque année. D'ici 2026, plus de 40% des gains de processeur proviendront deEmballage d'icAméliorations.

Les ingénieurs utilisent les solutions SiP et chiplet pour les nouveaux appareils. Ces moyens aident à rendre les appareils plus petits, plus rapides et moins chers. Alors que l'industrie se développe,Emballage d'icSera encore plus important pour de meilleures performances et de nouvelles idées.

Normes de l'industrie

JEDEC et IPC

JEDEC et IPC font des règles importantes pour le conditionnement des circuits intégrés. Ces groupes écrivent des documents pour aider les entreprises à concevoir et tester des produits. Le JEDEC établit des règles pour les dispositifs à semi-conducteurs. L'IPC établit des règles pour les circuits imprimés et les assemblages. Ils travaillent ensemble pour garder les produits sûrs et de haute qualité.

|

Titre de norme/document |

Numéro standard |

Date |

But |

Comité (s) |

|---|---|---|---|---|

|

Classification de la sensibilité à l'humidité/au reflux pour les SMD non hermétiques |

J-STD-020F |

Déc 2022 |

Définit les niveaux de sensibilité à l'humidité pour un emballage et une manipulation sûrs |

JC-14, JC-14.1 |

|

Manipulation, emballage, expédition et utilisation des SMD sensibles à l'humidité/refusion |

J-STD-033D |

Avr 2018 |

Normalisation de la manutention et de l'expédition pour éviter les dommages |

JC-14, JC-14.1 |

|

Préconditionnement des dispositifs non hermétiques à montage en surface avant les essais de fiabilité |

JESD22-A113I |

Avr 2020 |

Définit le flux de préconditionnement pour les tests de fiabilité |

JC-14.1 |

|

Mesure de gauchement de paquet d'IC de Surface-bâti à la température élevée |

JESD22-B112C |

Nov 2023 |

Mesures gauchage du paquet lors de la soudure |

JC-14, JC-14.1 |

|

Guide de test de fiabilité Carte de test de l'adaptateur |

JEP176A |

Juin 2025 |

Guides tests de fiabilité pour les CI avec cartes adaptateurs |

JC-14, JC-14.3 |

Ces règles aident les entreprises à faire moins d'erreurs et à mieux travailler ensemble. Ils aident également les entreprises à suivre les lois pour l'électronique médicale, automobile et domestique.

Qualité et interopérabilité

La qualité et l'interopérabilité sont très importantes pour le conditionnement des circuits intégrés.Règles IPC comme IPC-A-600 et IPC-6012Définir des étapes claires pour une bonne apparence et des performances. Le tableau ci-dessous montre quelques règles principales de la CIB et ce qu'elles font:

|

Norme d'IPC |

Zone de focus |

Rôle dans la validation de la fiabilité de la technologie d'emballage IC |

|---|---|---|

|

IPC-A-600 |

Acceptabilité visuelle des planches imprimées |

Assure seulement l'inspection sans défaut de passage de PCBs, soutenant la fiabilité de empaquetage. |

|

IPC-6012 |

Qualification et performance des PCB rigides |

Définit les exigences en matière de durabilité et de fiabilité à long terme. |

|

IPC-A-610 |

Acceptabilité des assemblages électroniques |

GuidesAssembléeQualité, soudure, et placement de composant. |

|

IPC-2221 |

Norme générique sur la conception de PCB |

Établit les meilleures pratiques pour réduire les erreurs et améliorer la cohérence. |

|

IPC-7711/7721 |

Retravailler, modifier et réparer |

Offre des processus de reprise et de réparation sûrs, en maintenant la qualité après modifications. |

Les tests sont importants pour s'assurer que les produits fonctionnent bien ensemble:

-

Algorithmes d'auto-test intégrésTrouver des problèmes dans les connexions rapides.

-

Les moniteurs d'intégrité de signal vérifient la santé des liens de puce.

-

La redondance et la réparation utilisent des voies supplémentaires pour maintenir des signaux forts.

-

Les fonctionnalités d'accès et de test haute vitesse aident à tester les puces à chaque étape.

-

Les tests environnementaux vérifient comment les puces fonctionnent avec les changements de chaleur, de puissance et de processus.

Les entreprises utilisent ces règles et tests pour s'assurer que leurs produits sont solides et fonctionnent bien pour des tâches importantes.

Tendances IC Packaging

Intégration 3D

L'intégration 3D est une grande tendance dansEmballage d'ic. Cette méthode empile de nombreuxIcDes couches les unes sur les autres. Ils relient les couches avec des liens spéciaux appelés vias à travers le silicium. Les entreprises utilisent l'empilage 3D pour améliorer le fonctionnement des appareils et utiliser moins d'énergie. Cela aide également à rendre les appareils plus petits. L'industrie vérifie les progrès avec des chiffres clés commePaquet, performance, puissance, profil, coût, et temps de cycle. Doug Yu de TSMC a fait ces chiffres pour aider à guider de nouvelles idées.

|

Aspect |

Détails |

|---|---|

|

Indicateurs clés de performance (KPI) |

Paquet, représentation, puissance, profil, coût, temps de cycle (PPPCC) |

|

Défis liés à l'adoption |

La technologie TSV n'est pas largement adoptée dans les applications mobiles sensibles aux coûts en raison de problèmes techniques et de coûts |

|

La fermeture de Quimonda en 2008 a retardé l'adoption de l'empilement des DRAM |

|

|

La concurrence de la fan-out wafer-level packaging (FOWLP) déplacé certains 3D IC adoption |

|

|

Exemples d'adoption |

Certains smartphones utilisent des CI 3D basés sur TSV, indiquant la production en volume |

|

Jalons |

SK Hynix a présenté les piles 3D TSV DRAM (HBM) en 2015 |

|

Intégration du système 3D via l'empilement wafer-to-wafer (W2W) et die-to-wafer (D2W) attendu vers 2022 |

|

|

Développements futurs |

Collage hybride et mise à l'échelle de pas pour améliorer le rendement et la performance dans l'empilement D2W |

|

Feuille de route de l'industrie et le consensus des experts soutiennent les progrès de l'intégration 3D en cours |

Les ingénieurs continuent à travailler pour résoudre les problèmes techniques et de coût dans l'intégration 3D. La liaison hybride et la mise à l'échelle du pitch peuvent aider à fabriquer plus de puces et à améliorer les performances. De nombreux smartphones utilisent désormais la 3DEmballage d'icCette tendance est maintenant courante. Les experts pensent que l'intégration 3D continuera de croître à mesure que de nouvelles conceptions de puces apparaîtront.

Fan-Out et Wafer-Level

L'emballage au niveau de la plaquette et l'emballage de l'échelle de puce au niveau de la plaquette ont changéEmballage d'icBeaucoup. Ces nouveaux types aident à rendre les appareils plus petits et à les emballer dans plus de pièces. Le marché de l'emballage à l'échelle de la puce au niveau de la plaquette étaitPrès de 4,9 milliards de dollars en 2023. Il pourrait atteindre plus de 37 milliards de dollars d'ici 2031. Cette croissance rapide montre que de nombreuses entreprises utilisent ces nouvelles méthodes.

-

Fan-in WLCSP permet aux appareils d'être plus petits et moins chers avec plus de pièces.

-

L'emballage au niveau de la plaquette de fan-out ajoute plus d'E/S en écartant des fils en dehors de la puce. Cela aide avec la chaleur et permet à plus de pièces de s'adapter.

-

Une meilleure technologie de lancement et de nouveaux matériaux aident à faire plus de bonnes puces et à réduire les coûts.

-

Des liens plus courts et un meilleur contrôle de la chaleur font que les appareils fonctionnent mieux et durent plus longtemps.

📈Insight de l'industrie:

L'emballage au niveau de la plaquette de fan-out et l'emballage au niveau de la plaquette d'échelle de puce aident à rendre des dispositifs plus petits et à améliorer des rendements de puce. Ces moyens permettent aux entreprises de fabriquer des appareils plus petits et plus puissants pour moins d'argent.

Les ingénieurs utilisent ces types d'emballage pour les téléphones, les appareils portables et l'électronique automobile. La poussée pour des appareils plus petits et meilleurs continue de conduire de nouveauxEmballage d'icIdées.

Intégration hétérogène

L'intégration hétérogène est maintenant une tendance principale dansEmballage d'ic. De cette façon, met différentsIcTypes, matériaux, et travaux dans un paquet. Les ingénieurs utilisent des vias à travers le silicium pour relier de nombreuses puces sur un substrat. Cela brise les anciennes limites de taille. Il contribue également à rendre les systèmes moins chers et permet aux systèmes à base de chiplet de fonctionner.

NouveauIntégration 3D hétérogèneLaisse des puces se relier aux tailles très petites, même vers le bas au submicron. L'industrie utilise maintenant l'empilement 3D, le mélange de nombreux travaux et l'intégration hybride. Ces changements apportent une densité élevée, une consommation d'énergie plus faible, une taille plus petite et une meilleure fiabilité.

Les conceptions de chiplet sont très importantes pour cette tendance. Les concepteurs peuvent choisir des chiplets pour la logique, la mémoire ou les travaux analogiques. Cela rend les solutions système-in-package flexibles et rapides à construire. Il aide également les nouveaux produits à sortir plus rapidement et prend en charge de nouvelles idées dans les puces.

💡Astuce:

L'intégration hétérogène et les conceptions de chiplet aident les ingénieurs à rendre les systèmes complexes plus rapides et plus faciles. Cette tendance répond au besoin de petits appareils électroniques puissants.

Matériaux avancés

Matériaux avancésSont derrière de nombreuses nouvelles tendances dansEmballage d'ic. Les ingénieurs choisissent des matériaux qui déplacent bien la chaleur, fonctionnent mieux avec l'électricité et durent plus longtemps. Ces matériaux aident à haute puissanceIcBesoins. Les liaisons cuivre, les diélectriques à faible k et les nouveaux substrats rendent possibles de nouveaux types d'emballages, comme les emballages 3D et les emballages au niveau des plaquettes.

-

Les nouveaux matériaux de refroidissement, comme le refroidissement microfluidique et les caloducs intégrés, aident à garder les copeaux au frais et à durer plus longtemps.

-

De meilleurs matériaux d'interface thermique aident les puces à gérer plus de chaleur.

-

L'intégration hétérogène utilise de nombreux matériaux semi-conducteurs dans un seul boîtier. Cela augmente les performances et réduit l'utilisation de l'énergie.

-

L'industrie produit des emballages recyclables et écologiques pour aider la planète.

-

L'emballage doit gérer la chaleur, la puissance, les changements de température et les problèmes de signal tels que EMI et la diaphonie.

-

Les petits appareils ont besoin de petits paquets complexes qui fonctionnent toujours bien et coûtent moins cher.

Les ingénieurs continuent à rechercher de nouveaux matériaux pour aider les nouvelles technologies et les conceptions de puces. Ces efforts font en sorteEmballage d'icSe maintient avec ce que les puces modernes ont besoin.

🔍Remarque:

Le passage aux matériaux avancés et aux nouvelles manières d'emballage façonnera l'avenir deEmballage d'ic. Les entreprises qui travaillent dans ces domaines mèneront les prochains grands changements dans les puces.

Défis et considérations

Complexité de la fabrication

L'emballage de circuits intégrés pose de nombreux problèmes dans la fabrication de produits. L'industrie doit suivre de nombreuses étapes et des règles strictes. Des études montrent quelques gros problèmes dans la fabrication de ces produits:

-

Pas assez d'usines de semi-conducteursSignifie que moins de puces sont faites. Cela ralentit les nouvelles technologies.

-

S'appuyer sur des pièces provenant d'autres pays peut causer des problèmes de chaîne d'approvisionnement.

-

Les règles strictes du gouvernement rendent difficile la construction de nouvelles usines. Cela ralentit le marché.

Ces choses rendent plus difficile la fabrication d'emballages. Les entreprises doivent acheter de meilleures machines et embaucher des travailleurs qualifiés. Des salles blanches et des outils spéciaux sont nécessaires pour ce travail. À mesure que les emballages s'améliorent, chaque étape doit répondre à des normes plus élevées.

Tests et fiabilité

Les tests et la fiabilité sont très importants dans l'emballage. Les entreprises utilisent de nouveaux systèmes de contrôle de la qualité pour obtenir de meilleurs résultats. Par exemple:

-

Une entreprise taïwanaise a testé unNouveau système de contrôle de qualité en temps réel.

-

Le système utilise des méthodes spéciales pour trouver les meilleurs paramètres.

-

Cela permet de faire de meilleurs produits et moins d'erreurs.

-

Les contrôles de qualité examinent le fonctionnement des tests de sonde de circuit.

-

Le système aide les usines intelligentes à maintenir des normes élevées avant l'emballage.

Ces moyens aident les entreprises à trouver les problèmes tôt et à s'assurer que les produits fonctionnent bien. Comme les puces deviennent plus petites, les tests doivent être encore plus prudents.

Coût et scalabilité

Le coût et l'évolutivité sont de gros soucis dans l'emballage. Les nouveaux emballages nécessitent des matériaux et des machines coûteux. Les entreprises doivent essayer de nouvelles choses, mais aussi maintenir les prix bas. Faire plus de produits peut utiliser de l'argent et des ressources. Les petites entreprises peuvent avoir du mal à concurrencer les plus grandes. L'industrie cherche des moyens d'économiser de l'argent tout en fabriquent de bons produits et en répondant à la demande.

Collaboration dans les écosystèmes

La collaboration écosystémique aide les emballages à progresser. Une entreprise ne peut pas tout faire seule. Collaborer avec les fournisseurs et les fabricants d'équipements aide à créer de nouvelles idées. Le partage des règles et la discussion ouverte facilitent la résolution des problèmes et permettent de travailler plus rapidement. Le travail d'équipe contribue également aux problèmes de chaîne d'approvisionnement et maintient les pièces à venir.

💡Un bon travail d'équipe dans l'écosystème apporte des progrès plus rapides et de meilleures solutions d'emballage.

L'emballage des circuits intégrés est toujours très important pour les semi-conducteurs. Le tableau ci-dessous montre comment l'emballage aide l'industrie à se développer et à changer:

|

Métrique/Tendance |

Détails |

|---|---|

|

~ 697 milliards de dollars |

|

|

Taux de croissance du marché (2025-2030) |

7%-9% par an |

|

Technologies clés |

3D empilant, système-dans-paquet, emballage niveau de gaufrette de fan-out |

Les personnes qui observent les tendances d'emballage peuvent répondre aux nouveaux besoins. Ils peuvent également aider à diriger de nouvelles technologies. L'emballage restera important pour de meilleures performances et de nouvelles utilisations à l'avenir.

FAQ

Qu'est-ce que le conditionnement des circuits intégrés et pourquoi est-ce important?

L'emballage de circuit intégré protège les puces contre les dommages. Il connecte les puces à d'autres parties d'un appareil. Il aide également à éloigner la chaleur de la puce. Cela rend les appareils fonctionnent mieux et durent plus longtemps. Les ingénieurs utilisent des emballages pour rendre l'électronique plus forte et plus rapide.

Comment les technologies d'emballage avancées améliorent-elles les performances des semi-conducteurs?

Les technologies d'emballage avancées rendent les connexions plus courtes. Cela aide les signaux à se déplacer plus rapidement et mieux. Ces moyens permettent à plus de pièces de s'adapter dans un petit espace. Les appareils peuvent fonctionner plus rapidement et consomment moins d'énergie. Cela permet à l'électronique de bien fonctionner et d'économiser de l'énergie.

Que sont les conceptions basées sur les chiplet et pourquoi sont-elles populaires?

Les conceptions basées sur les chiplet utilisent de petits blocs appelés chiplet. Les ingénieurs peuvent mélanger différents chiplets dans un paquet. Cela permet de rendre les nouveaux appareils plus rapides. Les conceptions de chiplet permettent aux entreprises d'utiliser des pièces provenant d'autres entreprises. Universal chiplet interconnect express aide à relier les chiplets ensemble.

Quelles normes guident les processus d'emballage et de fabrication?

JEDEC et IPC font des règles pour l'emballage et l'essai d'ic. Ces règles aident les entreprises à fabriquer des produits bons et sûrs. Ils aident également différentes entreprises à travailler ensemble. Les règles soutiennent de nouvelles façons de faire et tester les emballages ic.

Quelles sont les tendances qui façonnent l'avenir de l'emballage de l'ic?

Les tendances incluent l'empilement 3d, les systèmes de chiplet et les nouveaux matériaux. Les ingénieurs les utilisent pour fabriquer des appareils plus petits et plus rapides. L'industrie travaille également sur des emballages verts pour aider la planète. De nouvelles idées aident l'électronique à mieux fonctionner et à durer plus longtemps.