Processo de design ASIC: um guia passo a passo para criar circuitos integrados específicos de aplicativos

O processo ASIC ajuda a criar chips para usos especiais. Ao contrário dos processadores comuns, os ASICs oferecem alto desempenho para tarefas específicas.

OProcesso do projeto ASICAjuda a fazer chips para usos especiais. Ao contrário dos processadores comuns, os ASICs oferecem alto desempenho para tarefas específicas. Esses chips personalizados funcionam melhor, custam menos e fazem mais. OASICAs etapas do projeto precisam o planeamento e o trabalho cuidadosos. Eles são importantes para indústrias como carros, telefones e gadgets. Por exemplo, carros elétricos usam ASICs para gerenciar energia e conversar com peças. As etapas claras no design ASIC ajudam a criar chips confiáveis e economizadores de energia para as necessidades atuais.

Principais Takeaways

-

Objetivos claros são muito importantes. Eles orientam o design ASIC e evitam grandes erros.

-

Verificar a função do chip garante que ele funcione direito. Esta etapa encontra problemas cedo, economizando tempo e dinheiro.

-

Usar ferramentas inteligentes para codificação e layout ajuda muito. Essas ferramentas fazem chips fortes e rápidos.

-

Projetos amigáveis ao teste facilitam o teste. Eles ajudam a encontrar e corrigir problemas cedo para que o chip funcione bem mais tarde.

-

Um bom arquivo GDSII é necessário para fazer chips. Ele garante que o projeto segue as regras da fábrica e funciona corretamente.

Especificação e RTL Code Generation

Definindo as especificações

O primeiro passo para criar um ASIC é definir especificações. Isso significa decidir o que o chip deve fazer, quão rápido ele deve funcionar e quaisquer limites que ele tenha. Esta etapa mantém o processo de design organizado e no caminho certo. AEspecificação clara funciona como um plano, Orientando todo o projeto. Ajuda a evitar erros que possam atrasar o trabalho ou aumentar os custos. Este passo geralmente leva 2 a 6 semanas porque requer muita atenção.

As especificações também ajudam você a descobrir os principais recursos do chip. Por exemplo, se você está fazendo um chip para um smartphone, você pode se concentrar em economizar energia e trabalhar mais rápido. As especificações claras garantem que o chip faça o que é suposto fazer.

Escrevendo código RTL

Após definir as especificações, você pode começar a escrever o código RTL (Register Transfer Level). Este código mostra como o chip funciona e é construído. Ele usa linguagens especiais como Verilog ou VHDL. O código RTL transforma as especificações em um modelo funcional do chip.

Nesta fase, você precisa verificar se o código RTL corresponde às especificações. Verificar muitas vezes ajuda a encontrar erros cedo e economiza tempo depois. Por exemplo, usar checkpoints durante a depuração pode ajudar a encontrar partes ausentes ou erros mais rapidamente, tornando o processo mais suave.

Ferramentas para especificações e código RTL

Existem ferramentas para ajudar a definir especificações e escrever código RTL. Essas ferramentas facilitam o processo e melhoram o design. Por exemplo, as ferramentas de simulação permitem testar o código RTL para garantir que ele funcione conforme o planejado.

Um estudo de caso mostra como as ferramentas RTL podem ser úteis. A depuração com checkpoints ajudou a encontrar problemas mais rapidamente do que apenas usar logs. EsteMelhorou a taxa de aprovação de 72,4% para 93,6%-A. Ele mostra como ferramentas avançadas podem melhorar o design ASIC.

|

Configuração |

Passe Taxa (%) |

Melhoria (%) |

|---|---|---|

|

Baunilha LLM |

72,4 |

N/A |

|

Agente único |

83,9 |

11,5 |

|

Multi-agente |

93,6 |

21.2 |

O uso dessas ferramentas pode tornar seu ASIC mais confiável e funcionar melhor.

Verificação Funcional

Verificação funcional verifica se o chip funciona como planejado.Isso garante que o chip atinja seus objetivos e evite erros. Ignorar essa etapa pode causar falhas, desperdiçar dinheiro e incomodar os clientes. Verificar antecipadamente ajuda a detectar erros e torna o chip mais confiável.

Ter certeza que o design está correto

Esta etapa garante que o chip corresponda ao seu plano e funcione bem. Ele reduz riscos como chips quebrados ou mau desempenho. Para empresas sem fábricas, constrói a confiança do cliente entregando bons chips. As fábricas também perdem menos material quando os projetos são verificados.

-

Por que a verificação funcional importa:

-

Faz o chip seguir o seu plano.

-

Reduz as chances de problemas com chips.

-

Constrói a confiança do cliente.

-

Poupa materiais durante a produção.

-

Usando simulações

Simulações testam o chip em diferentes situações. Eles encontram problemas antes de fazer o chip. Estes testes verificam como o chip se comporta e executa. Métodos como testes lógicos e verificações formais são comuns para esta etapa.

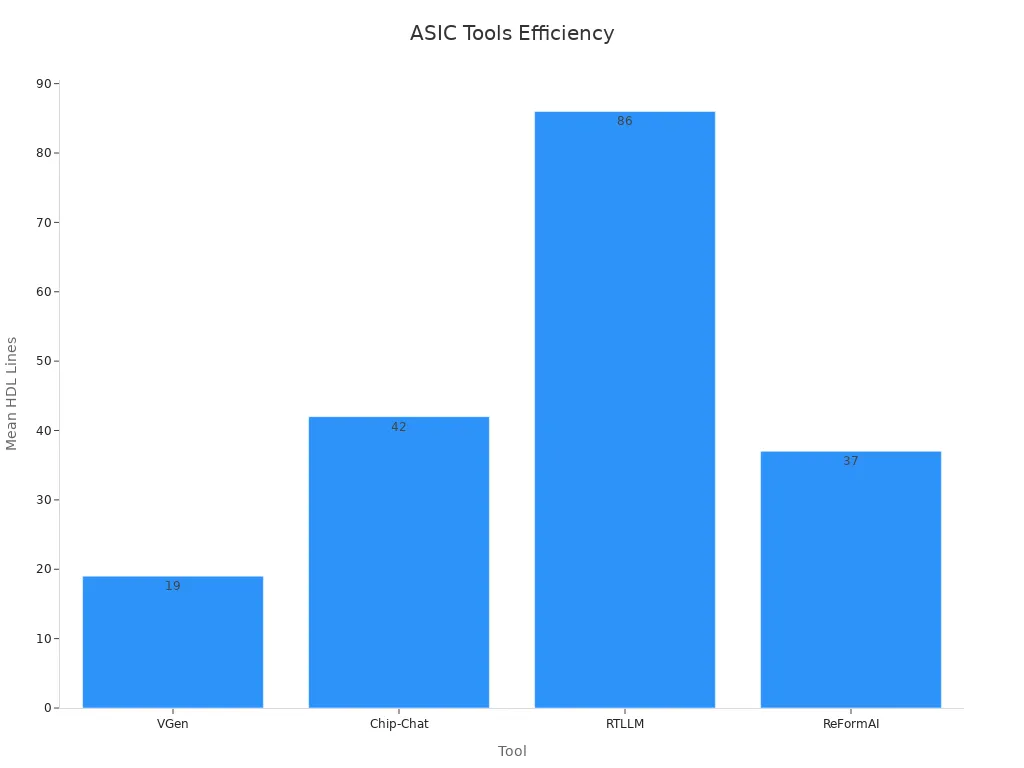

Por exemplo, ferramentas como VGen e RTLLM ajudam a testar chips de tamanhos diferentes.A tabela abaixo mostra o quão bem essas ferramentas lidam com diferentes quantidades de código:

|

Ferramenta |

Projetos testados |

Linhas código totais |

Linhas médias |

Linhas Max |

Linhas código totais |

|---|---|---|---|---|---|

|

VGN |

17 |

0,3 K |

19 |

48 |

0,3 K |

|

Chip Chat |

8 |

0,3 K |

42 |

72 |

0,3 K |

|

RTLLM |

30 |

2,5 mil |

86 |

518 |

2,5 mil |

|

ReFormAI |

30 |

2227K |

37 |

773 |

2227K |

Ferramentas para Verificar Designs

Ferramentas especiais tornam a verificação dos projetos mais fácil e melhor. Essas ferramentas encontram e corrigem problemas rapidamente. Eles também ajudam o chip a atingir seus objetivos e funcionar bem.

O gráfico abaixo mostra quanto código diferentes ferramentas podem manipular:

O uso dessas ferramentas torna o processo de verificação mais rápido e melhora o sucesso do chip.

RTL para Gate-Level Netlist

O que é Síntese?

Síntese é um passo importante para fazer ASICs. Ele muda o código RTL (Register Transfer Level) para um netlist de nível de portão. Este netlist mostra as portas lógicas físicas do chip. A síntese conecta a ideia do projeto ao chip real. Isso garante que o chip possa ser construído e ainda funcione como planejado.

Em síntese, o design é melhorado em termos de velocidade, tamanho e potência. Essas melhorias ajudam o chip a atingir seus objetivos sem perder desempenho. Por exemplo, ferramentas de síntese transformam o código RTL em células padrão de uma biblioteca. Isso cria um design que é ao mesmo tempo bom e fácil de fazer.

Como RTL Se Torna Uma Netlist De Nível De Portão

Alterar RTL para um netlist de nível de portão tem etapas. Primeiro, as ferramentas de síntese transformam o código RTL em um design básico de portão. Em seguida, o design é melhorado para torná-lo mais rápido, usar menos energia e trabalhar melhor. Finalmente, o netlist é verificado para corresponder ao plano original.

Esse processo também segue regras como prazos e limites de tamanho. Essas regras garantem que o chip funcione bem na vida real. Por exemplo, ao fazer CPUs ou chips criptográficos, as ferramentas de síntese recuperam registros muito bem.A tabela abaixo mostra como as ferramentas de síntese funcionam para diferentes projetos:

|

Tipo do projeto do hardware |

Recuperação Taxa |

Notas |

|---|---|---|

|

Co-processadores criptográficos |

Quase perfeito |

Recupera registros de alto nível efetivamente |

|

CPU |

Quase perfeito |

Funciona bem em muitos projetos |

|

OpenTitan (SoC) |

Quase perfeito |

Apoiado por especialistas do setor |

Ferramentas para Fazer Netlists de Nível Gate

Muitas ferramentas ajudam a criar netlists de nível de porta para ASICs. Os mais populares são Synopsys Design Compiler, Cadence Genus e Mentor Graphics Precision. Essas ferramentas tornam a síntese mais fácil e precisa. Eles também verificam o tempo e melhoram o uso de energia, que são fundamentais para bons chips.

O uso dessas ferramentas torna a síntese mais rápida e reduz erros. Por exemplo, o Synopsys Design Compiler verifica o tempo e aumenta o desempenho. Cadence Genus ajuda a reduzir o uso de energia, tornando-se uma ótima ferramenta para o design ASIC.

Layout do projeto ASIC

Básico de Layout Design

O layout de um ASIC é como um mapa para sua estrutura. Mostra onde as partes vão e como elas se conectam. Um bom layout ajuda o chip a funcionar bem, usar menos energia e atingir seus objetivos. Este passo é muito importante porque afeta o quão confiável e útil o chip será.

Durante esta etapa, você deve pensar em muitas coisas. Estes incluem onde colocar os portões, como conectá-los e seguir as regras de design. Cada escolha muda a forma como o chip funciona e como é fácil de fazer. Por exemplo, um layout menor pode tornar os sinais mais rápidos e economizar energia.

Passos para Fazer um Layout

Fazer um layout tem muitas etapas para transformar o design em um chip real. Primeiro, o planejamento do piso organiza as principais partes do chip. Em seguida, a colocação decide exatamente onde cada parte vai. Depois disso, o roteamento conecta as peças com fios, evitando problemas como atrasos.

Verificar o layout é muito importante nesta etapa. Você precisa ter certeza de que segue as regras e cumpre o plano. As ferramentas verificam problemas como sinais ruins ou problemas de tempo. Essas verificações impedem erros caros antes de fazer o chip.

Hoje,O aprendizado de máquina ajuda com muitas dessas tarefas-A. Melhora o posicionamento e o roteamento para melhorar os chips e usar menos energia. Isso torna o processo mais rápido e cria layouts de maior qualidade.

Ferramentas para melhores layouts

Ferramentas especiais tornam o design do layout mais fácil e rápido. As ferramentas baseadas em IA testam muitos projetos para encontrar o melhor layout. Eles economizam tempo, melhoram o desempenho e fazem com que os chips usem menos energia. Ao usar dados passados, essas ferramentas criam layouts melhores mais rapidamente do que métodos mais antigos.

Por exemplo, as ferramentas de machine learning lidam melhor com tarefas do que os humanos. Eles fazem chips de alta qualidade e os preparam mais rápido. O uso dessas ferramentas torna o processo de design ASIC mais suave e bem-sucedido.

Projeto para técnicas do teste

Tornando os testes mais fáceis

Tornar os testes mais fáceis garanteASICFunciona bem depois de feito. Projetar com testes em mente ajuda a encontrar e corrigir problemas cedo. Isso torna seu chip mais confiável e evita erros dispendiosos durante a produção.

Testes melhores também melhoram os resultados após a construção do chip. Por exemplo:

-

Sondas especiais ajudam a medir materiais remanescentes como o fluxo.

-

Testes aprimorados fornecem resultados de testes elétricos mais precisos.

-

Embora complicado,Sondas de ponta de cinzelSão fundamentais para os melhores resultados.

O foco nos testes garante suaASICFunciona bem e cumpre seus objetivos em uso real.

Formas comuns de projetar para testes

Projeto para o teste (DFT) Métodos tornam os chips mais fáceis de verificar e corrigir. Esses métodos incluem:

-

Correntes Digitalizar: Vincular registros internos em uma cadeia para encontrar falhas.

-

Auto-teste incorporado (BIST): Permite o teste próprio da microplaqueta, precisando menos equipamento.

-

Fronteira varredura: Verifica as conexões entre chips para garantir que eles se comuniquem.

Usar esses métodos torna os testes mais simples e melhora a qualidade do seu chip.

Ferramentas para testar o design

Muitas ferramentas ajudam comDFTTécnicas. Os mais populares são Synopsys DFTMAX, Cadence Modus e Mentor Tessent. Essas ferramentas automatizam tarefas como adicionar scan chains e criar testes padrões.

Por exemplo, Synopsys DFTMAX aumenta a testabilidade sem prejudicar o desempenho. Cadence Modus corta o tempo do teste e encontra mais falhas. Mentor Tessent adiciona recursos avançados para BIST e varredura limite.

O uso dessas ferramentas torna os testes mais rápidos e garante suaASICÉ confiável e executa bem.

Planejamento do piso

Organizando peças Chip

O planejamento do piso é um passo fundamental para fazer ASICs. Isso significa organizar as peças do chip para funcionar bem e ter um melhor desempenho. Nesta etapa, você decide para onde vai cada parte do chip. Você pensa em coisas como como as peças se conectam, o fluxo de energia e a força do sinal. Uma boa planta baixa ajuda o chip a correr mais rápido, usar menos energia e atingir seus objetivos.

Uma parte importante do planeamento do assoalho é segurar redes. Redes são as ligações entre as partes do chip. Por exemplo,60-70%De redes se conectam a apenas uma outra parte. Essas redes geralmente ligam partes próximas e têm padrões que são fáceis de detectar. Redes que se conectam a mais de uma parte têm uma propagação mais uniforme. Conhecer esses padrões ajuda a planejar os fios e evitar problemas com potência ou velocidade.

|

Descrição estatística |

Valor/Detalhes |

|---|---|

|

Percentagem de redes com FO = 1 |

60-70% |

|

Características de FO = 1 |

Cauda longa, picos para vizinhos próximos e roteamento do subgrupo |

|

Características de FO > 1 |

Distribuição simétrica e plana |

|

Abordagem da tabela da fio-carga |

80-90% percentil para estimativa de capacitância no pior caso |

|

Variação do comprimento líquido |

Depende do tamanho do bloco (por exemplo, 25 k-gate vs. 5 k-gate) |

|

Dependência na forma do bloco |

Estatísticas calculadas para blocos quadrados |

|

Dependência do tipo netlist |

Varia com base em restrições de síntese (por exemplo, atraso mínimo vs. área mínima) |

Fatores importantes do planeamento do assoalho

Ao planejar um layout de chip, você precisa pensar em muitas coisas. Estes incluem o tamanho e a forma das peças, controle de calor e fluxo de energia. Por exemplo, o planejamento do calor pode ajudar o chip a ficar frio e funcionar melhor. Além disso, colocar as peças nos pontos certos pode tornar os sinais mais rápidos e os fios mais curtos.

As ferramentas AI agora ajudam no planejamento do pisoFazendo as tarefas automaticamente. A IA analisa projetos rapidamente e encontra os melhores layouts. Isso economiza tempo e faz melhores fichas do que fazê-lo à mão.

Ferramentas para o planeamento do assoalho

Ferramentas modernas tornam o planejamento do piso mais fácil e melhor. Essas ferramentas permitem que você experimente diferentes layouts e corrija problemas com tempo ou energia. Ferramentas alimentadas por IA podem criar layouts que equilibram velocidade e uso de energia. Eles também encontram áreas quentes e sugerem correções para manter o chip confiável.

O uso dessas ferramentas torna o planejamento do piso mais rápido e preciso. Este passo é muito importante para fazer ASICs que funcionam bem na vida real.

Colocação

Organizando componentes para melhor desempenho

Colocar componentes em um chip é muito importante. Isso afeta o quão rápido e eficiente o chip funciona. Colocação significa organizar peças para reduzir atrasos e economizar energia. A boa colocação também facilita a conexão dos fios mais tarde.

Para verificar a qualidade do posicionamento, os designers usam certas medidas. Dois comuns são osComprimento do fio do meio perímetro (HPWL)EPior Slack Negativo (WNS)-A. Isso ajuda a mostrar como o posicionamento afeta a velocidade e o uso da energia. O quadro seguinte explica estas medidas:

|

Métrica |

O Que Significa |

Por que é importante |

|---|---|---|

|

HPWL |

Caminhos mais curtos do fio |

Poupa energia e acelera o fluxo de dados |

|

WNS |

Problemas do sincronismo |

Corrigi-los melhora o desempenho |

|

FRIQ |

Velocidade do chip |

Maior frequência significa operação mais rápida |

Ao se concentrar nesses, os designers podem garantir que o chip atinja seus objetivos.

Maneiras de Colocar Componentes

Existem diferentes maneiras de organizar as peças em um chip. Um método é o “posicionamento padrão de células”, onde pequenas partes são alinhadas em linhas. Isso economiza espaço e encurta os fios. Outra maneira é a "colocação macro", que coloca as partes grandes primeiro. Peças menores são adicionadas mais tarde para melhorar o desempenho.

Métodos avançados como recozimento simulado e particionamento também são usados. Essas técnicas testam muitos layouts para encontrar o melhor deles. Por exemplo, o recozimento simulado move as peças para reduzir o comprimento do fio e evitar áreas lotadas.

Ferramentas para colocação mais fácil

Ferramentas especiais ajudam a automatizar tarefas e melhorar os resultados. Ferramentas como Cadence Innovus, Synopsys IC Compiler II, e Mentor Graphics Olympus-SoC são populares. Eles verificam problemas como fios lotados, problemas de tempo e uso de energia.

A tabela abaixo mostra o que essas ferramentas medem:

|

Métrica |

O que verifica |

|---|---|

|

Pior Slack Negativo (WNS) |

Encontra o maior problema de tempo no design. |

|

Slack negativo total (TNS) |

Adiciona todos os problemas de tempo para ver o desempenho geral. |

|

Número de Caminhos Violadores (NVP) |

Conta caminhos que falham regras cronometrando. |

|

Congestionamento |

Verifica se os fios estão muito lotados em algumas áreas. |

|

Comprimento do fio (WL) |

Mede o comprimento total dos fios no chip. |

|

Comprimento do fio do meio perímetro (HPWL) |

Estimativas comprimento do fio, somando metade perímetros de caixas delimitadoras. |

|

Macro HPWL (mHPWL) |

Concentra-se no comprimento do fio apenas para peças grandes. |

O uso dessas ferramentas ajuda a criar chips rápidos, eficientes e confiáveis.

Relógio Árvore Síntese

Mantendo as peças do Chip em sincronia

A árvore do relógio é uma parte fundamental de um chip. Isso garante que todas as partes do chip trabalhem juntas ao mesmo tempo. Se o tempo estiver desligado, o chip pode não funcionar bem. A árvore do relógio envia o sinal do relógio para cada parte do chip. Isso mantém o tempo estável e ajuda o chip a funcionar sem problemas. É muito importante para fazer um ASIC confiável e eficiente.

A síntese da árvore do relógio funciona para equilibrar o tempo do sinal do relógio. Esse equilíbrio é chamado de inclinação do relógio e deve permanecer pequeno para evitar problemas. Um bom design da árvore do relógio reduz atrasos e ajuda o chip a ter melhor desempenho.

Passos para desenhar uma árvore do relógio

Fazer uma árvore do relógio tem várias etapas para melhorar o tempo e a potência. Primeiro, decida de onde vêm os sinais do relógio e como eles se espalharão. Em seguida, verifique se o sinal do relógio atinge todas as partes ao mesmo tempo. Uma maneira de economizar energia é o gating do relógio, que desativa partes não utilizadas da árvore do relógio. O gating do relógio pode economizar até 20% de energia, mas pode tornar o chip um pouco maior.

Outro método é o posicionamento da árvore do relógio. Isto reduz o poder de comutação líquido25,3% e potência total em 11,4%-A. Ele faz isso com pouco efeito no tempo (2,0%) e tamanho do chip (1,2%). O design Multi-Corner Multi-Mode (MCMM) também ajuda a melhorar o tempo, a potência e as regras de fabricação em diferentes situações.

Ferramentas para Fazer Árvores Relógio

Ferramentas especiais tornam a síntese árvore relógio mais fácil. Os mais populares são Synopsys PrimeTime, Cadence Innovus e Mentor Graphics Olympus-SoC. Essas ferramentas ajudam a projetar e verificar as árvores do relógio para atender às necessidades de tempo e energia. Eles também incluem recursos para gating relógio e MCMM, tornando o processo mais rápido.

O uso dessas ferramentas ajuda seu design ASIC a funcionar melhor e durar mais tempo. Eles resolvem problemas de temporização e reduzem o uso de energia, criando um chip bem cronometrado e eficiente.

Roteamento

Conectando componentes

O roteamento liga partes de um chip com fios. Garante que os sinais se movam rápida e corretamente entre as seções do chip. Esta etapa é muito importante porque o roteamento ruim pode retardar o chip, desperdiçar energia e prejudicar o desempenho. Planejar caminhos do fio cuidadosamente evita áreas lotadas e mantém o chip funcionando bem.

O roteamento cria caminhos para sinais enquanto segue as regras do projeto. Essas regras incluem manter os fios separados, evitar sobreposições e reduzir problemas de sinal. Um bom roteamento torna o chip mais confiável e melhor para o seu trabalho.

Estratégias Roteamento

Boas estratégias ajudam os chips a trabalhar mais rápido e melhor. Diferentes métodos resolvem problemas como fios lotados e atrasos no tempo. Por exemplo, a ligação híbrida conecta camadas múltiplas da microplaqueta, precisando menos caminhos largos do fio. CIs 3D corrigem aglomerações 2D, mas adicionam desafios com conexões verticais. As ferramentas AI colocam os blocos de conexão perto das bordas para equilibrar as camadas do fio.

|

Estratégia Roteamento |

Como Ajuda |

|---|---|

|

Ligação híbrida |

Ligações múltiplas camadas, necessitando menos caminhos largos do fio. |

|

CIs 3D |

Corrige o apinhamento 2D do fio mas adiciona desafios verticais da conexão. |

|

Coloca a conexão perto das bordas para equilibrar as camadas do fio. |

Métodos avançados como o aprendizado por reforço (RL) tornam o roteamento mais rápido. O RL melhora a velocidade da conexão do fio em 45% em relação aos métodos mais antigos e é 32% mais rápido do que os métodos focados no tempo. No geral, os processos backend são 22% mais rápidos com métodos de roteabilidade e 15% mais rápidos com métodos de temporização.

-

Melhorias do roteamento avançado:

-

Ligações do fio 45% mais rápidasMétodos de roteabilidade.

-

32% mais rápido que os métodos focados no tempo.

-

Aceleração do processo backend: 22% (roteabilidade) e 15% (tempo).

-

Ferramentas para Roteamento

As ferramentas de roteamento tornam as peças do chip mais fáceis e precisas. Ferramentas populares incluem Cadence Innovus, Synopsys IC Compiler II, e Mentor Graphics Olympus-SoC. Essas ferramentas planejam caminhos de arame, reduzem a aglomeração e melhoram o tempo. Eles também seguem as regras do projeto para atender às necessidades do chip.

Ferramentas modernas geralmente usam IA para melhorar o roteamento. AI verifica projetos e encontra os melhores caminhos do fio, economizando energia e tempo. O uso dessas ferramentas torna o roteamento mais rápido e oferece melhores resultados.

Verificação física Controlos

Verificando Chip Design

A verificação física garante que seu chip siga as regras do design e funcione. Esta etapa verifica se o layout do chip corresponde ao plano original. Também garante que o chip funcione corretamente quando construído. Corrigir problemas cedo economiza dinheiro e melhora o desempenho do chip.

Duas verificações principais são necessárias aqui. Primeiro, confirme se o projeto segue as regras da fábrica. Em segundo lugar, verifique se o layout corresponde ao design lógico. Essas verificações encontram problemas como fios muito próximos, espaçamento errado ou links ausentes. Resolver esses problemas cedo torna o processo de fabricação de chips mais suave.

Formas de Verificar Designs

Existem diferentes maneiras de verificar o design do seu chip. O Design Rule Checking (DRC) garante que o layout siga as regras da fábrica. Layout Versus Schematic (LVS) compara o layout ao plano de design para garantir que eles correspondam. A extração parasitária (PEX) encontra efeitos elétricos indesejados causados pelo layout.

Por exemplo, a RDC pode detectar fios muito próximos, o que pode causar problemas. O LVS verifica se todas as conexões no layout existem no plano. PEX prevê como efeitos indesejados podem alterar o desempenho do chip. Usando todos esses métodos dá uma verificação completa do design do seu chip.

Ferramentas para verificação Chip

Ferramentas especiais tornam a verificação dos projetos mais rápida e fácil. Os populares incluem Cadence Pegasus, Synopsys IC Validator e Mentor Calibre. Essas ferramentas automatizam tarefas como DRC, LVS e PEX, economizando tempo e reduzindo erros. Eles também fornecem relatórios detalhados para corrigir problemas rapidamente.

Por exemplo, o Mentor Calibre é ótimo para verificações precisas RDC e LVS. Synopsys IC Validator lida bem com projetos complexos. Cadência Pegasus trabalha rápido para chips grandes. O uso dessas ferramentas garante que seu chip atenda a todas as regras e funcione confiavelmente.

Preparação do arquivo GDSII

Obtendo o projeto pronto para fabricação

O último passo para criar um ASIC é prepará-lo para a fabricação. Aqui, você verifica se o design do chip atende a todas as regras da fábrica. Você também garante que o chip funcionará corretamente assim que for feito. É importante corrigir quaisquer erros que possam prejudicar o desempenho ou a duração do chip.

Este passo é muito importante porque transforma o design digital em um chip real. Um design bem preparado ajuda a evitar problemas caros durante a produção. Também mantém o processo suave e eficiente.

Etapas para Criar um Arquivo GDSII

Para obter o design pronto, você precisa fazer um arquivo GDSII. Este arquivo é como um mapa do chip. Ele mostra onde todas as partes vão, como os fios se conectam e detalhes sobre as camadas.

Primeiro, você exporta o layout das ferramentas de design para o formato GDSII. Em seguida, você verifica o arquivo para garantir que ele corresponda perfeitamente ao design. Finalmente, você envia o arquivo para a fábrica para construir o chip. Cada passo precisa ser feito com cuidado para evitar erros que possam causar problemas.

Ferramentas para ajudar com arquivos GDSII

Existem ferramentas que facilitam a criação e verificação de arquivos GDSII. Alguns dos mais populares são Cadence Virtuoso, Synopsys IC Compiler II e Mentor Graphics Calibre. Essas ferramentas automatizam tarefas como extrair dados de layout, criar o arquivo e encontrar erros. Eles também garantem que o design siga as regras da fábrica, reduzindo a chance de problemas de produção.

O uso dessas ferramentas torna o processo ASIC mais rápido e confiável. Eles ajudam a garantir que seu chip funcione conforme o planejado.

O processo de design ASIC é fundamental para fazer chips especiais. Isso ajuda a criar chips que usam menos energia e funcionam bem. Um plano claro facilita o processo e reduz os custos. Isso o torna ótimo para fazer1.000 a 100.000 fichas-A. Usar métodos testados de fornecedores reduz riscos e acelera a produção.

O trabalho em equipe e as ferramentas inteligentes são muito importantes para o sucesso. Essas ferramentas tornam as tarefas mais simples e precisas. Eles também garantem que o chip funcione como planejado. Ao seguir etapas claras, você pode construir chips que economizam espaço e atendem às necessidades tecnológicas atuais.

FAQ

O que é um ASIC e por que isso importa?

Um ASIC é um chip especial feito para um trabalho. Funciona melhor e usa menos energia do que os chips comuns. Indústrias como carros e telefones usam ASICs para soluções personalizadas que atendem às suas necessidades.

Como um ASIC é projetado?

Projetar um ASIC tem muitas etapas, como planejamento, verificação e teste. Cada etapa garante que o chip funcione bem e possa ser construído. Esse processo ajuda a criar chips confiáveis e de alto desempenho.

Quais ferramentas ajudam a criar ASICs?

Ferramentas como Synopsys Design Compiler e Cadence Innovus são usadas. Eles ajudam na construção, organização e verificação do chip para atingir seus objetivos.

Por que verificar a função do chip é importante?

Verificar garante que o chip funcione como planejado. Encontra erros cedo, economizando tempo e dinheiro. Este passo é fundamental para fazer um chip bom e confiável.

Como é que o layout afeta o chip?

O layout mostra onde as peças vão e como elas se conectam. Um bom layout torna o chip mais rápido, economiza energia e melhora o funcionamento geral.