O que Determina SPI Speed Um Guia Completo

A Serial Peripheral Interface (SPI) é famosa pela transferência de dados em alta velocidade. Este protocolo comunicação síncrona habilitar

OInterface Periférica Serial(SPI) É famosa porTransferência de dados a alta velocidade-A. EsteProtocolo comunicação síncronaPermite dados eficientesTransferênciaEntreDispositivos, Com algunsDados transferir taxas Superior a 100 MHz-A. Então, por que o seu projeto nãoDesempenhoSempre bater estes topDados transferir taxas? Seu verdadeiroVelocidade SPIE geralRendimentoSão limitados por três áreas-chave.

💡A finalDesempenhoDe qualquerSPIDadosTransferênciaÉ um equilíbrio de suaDispositivos'Limites de hardware, qualidade física da conexão e configuração do software.

Principais Takeaways

- Sua velocidade SPI depende de três coisas principais: os limites de hardware dos seus dispositivos, a qualidade de suas conexões físicas e como você configurou seu software.

- Sempre verifique os limites de velocidade nas planilhas de dados dos dispositivos mestre e escravo. O dispositivo mais lento define a velocidade máxima para o seu barramento SPI.

- Um bom design PCB é importante. Mantenha os fios curtos, combine comprimentos de traço e use um plano de terra forte para evitar problemas de sinal em altas velocidades.

- Usar DiretoMemóriaAcesso (DMA) em seu software para o melhor desempenho. O DMA deixa o seuMicrocontroladorEnviar dados rapidamente sem abrandar o processador principal.

Papel do hardware na velocidade SPI

O primeiro passo para entender a velocidade SPI máxima do seu sistema é olhar para o próprio hardware. Antes mesmo de escrever uma linha de código ou projetar um PCB, as folhas de dados para seus dispositivos mestre e escravo definem um limite superior rígido. O seu desempenho final está fundamentalmente ligado às capacidades destesCircuitos integrados-A.

Limites do Relógio Mestre

O dispositivo mestre, normalmente um microcontrolador, gera o relógio SPI (SCK). Este dispositivo tem uma frequência máxima em que pode operar seuInterface periférica serial-A. Você pode encontrar esse limite emSeção características elétricas de sua ficha técnica-A. As tabelas geralmente especificam o máximoFSCK(SPI clock frequency) sob diferentes tensões operacionais.

Por exemplo, a folha de dados de um microcontrolador pode apresentar suas características SPI como esta:

| Símbolo | Parâmetro | Condições | Mín | Tipo | Máximo | Unidade |

|---|---|---|---|---|---|---|

| FSCK | SPI frequência do relógio | Modo do receptor do controlador 2.7 V <VDD< 3.6 V | - | - | 45 | MHz |

| Modo do transmissor do controlador 2.7 V <VDD< 3.6 V | - | - | 45 | MHz |

Nota:Os valores na tabela acima são baseados em

FPCLKx/3, OndeFPCLKxÉ o relógio periférico. O valor máximo real depende da arquitetura específica do microcontrolador.

O relógio do próprio sistema do mestre também desempenha um papel. O periférico SPI geralmente é executado em um relógio derivado do relógio principal do sistema.

- A arquitetura do relógio interno de um microcontrolador pode limitar o relógio de entrada do módulo SPI. Por exemplo, um módulo só pode aceitar uma entrada máxima de48 MHz-A.

- Este relógio de entrada é então dividido para gerar o sinal SCK final para a transferência SPI.

- Isso significa que mesmo que o periférico SPI possa teoricamente funcionar mais rápido, seu desempenho é limitado pelo relógio que você o alimenta.

Restrições do relógio escravo

Agora, considere o dispositivo escravo. Cada escravo SPI, se é umSensor, Chip de memória, ou outro microcontrolador, também tem uma frequência de clock máxima que pode manipular. Este é frequentemente o gargalo mais significativo em uma configuração mestre/escravo.Exceder esse limite fará com que o escravo interprete mal os dados, levando a corrupção de dados durante a transferência-A.

💡Seu barramento SPI é tão rápido quanto seu dispositivo mais lento. A velocidade de comunicação final deve ser definida para o menor dos dois máximos (mestre ou escravo).

Você deve verificar cuidadosamente o datasheet do escravo. Você pode encontrar diferentes taxas máximas de transferência dependendo da operação. Por exemplo, umO microcontrolador STM32 no modo escravo pôde apoiar 40 MHz para receber dados mas uma velocidade mais baixa como 24 MHz para uma comunicação full-duplex-A. Essas diferenças podem surgir da lógica interna necessária para amostrar e enviar dados simultaneamente. Para a maioria dos dispositivos SPI escravo, uma regra de ouro segura é manter a taxa de relógio SPI abaixoUm décimo da frequência do relógio do próprio sistema do escravoAssegurar uma transferência de dados fiável.

Processamento Escravo Atrasos

Uma frequência de clock alta nem sempre é igual a alta produtividade. A verdadeira medida de desempenho é a quantidade de dados que você pode transferir ao longo do tempo. Muitos dispositivos escravos precisam de uma pausa entre transações para processar informações. Isso é conhecido comoTempo processamento escravoOuAtraso entre transações-A.

Imagine que você envia um comando para um sensor. O sensor precisa de tempo para realizar uma medição antes de ter os dados prontos para a próxima transferência. Um relógio SPI rápido é inútil se o mestre tiver que esperar muito tempo para que o escravo esteja pronto. Esse atraso afeta drasticamente o throughput geral dos dados.

Alguns cenários comuns que exigem esse atraso incluem:

| Cenário | Por que um atraso é necessário |

|---|---|

| Escravo tem lenta lógica interna | O dispositivo precisa o tempo de processar o byte precedente dos dados. |

| Protocolos SPI multi-frame | O próprio protocolo requer um intervalo específico entre frames. |

| SPI Flash página escreve | O chip deve pausar para trancar um endereço antes de gravar dados. |

| Evitando erros cronometrando | Um pequeno atraso pode ajudar a evitar erros em velocidades de clock SPI muito altas. |

Então, como você sabe quando o escravo está pronto para a próxima transferência? Dispositivos usam vários métodos para sinalizar seu status:

- Pin ocupado:Alguns dispositivos têm um pino de saída dedicado que eles afirmam sinalizar que estão ocupados processando.

- Registro Status:Você pode pesquisar um registro de status no escravo. Este registro geralmente contém bits como

TRD(Transmitir pronto) ouRrdy(Receber pronto) para indicar seu estado. - Interrompe:O escravo pode usar esses bits de status para acionar uma interrupção no mestre, sinalizando ativamente que ele está pronto para a próxima transação SPI.

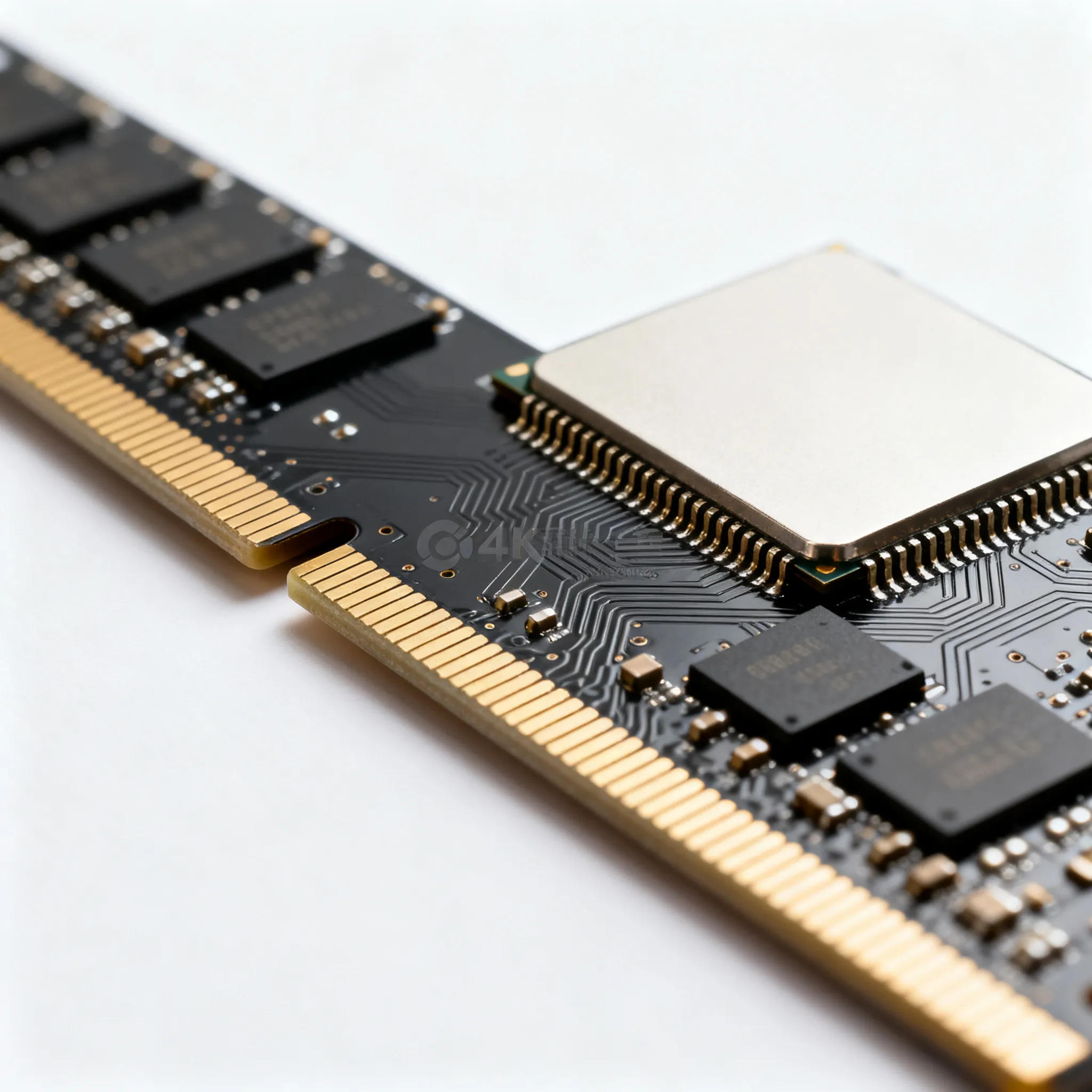

A Interface Periférica Serial Camada Física

Quando você entender os limites do seuCircuitos integrados, Você deve olhar para as conexões físicas entre eles. A placa de circuito impresso (PCB) traços e fios que formam o seu barramento SPI não são condutores perfeitos. Em altas frequências, esses caminhos físicos apresentam seu próprio conjunto de desafios que podem degradar a qualidade do sinal e limitar seu desempenho geral.

Caminho do sinal e layout

Fios longos e traços PCB podem agir como pequenas antenas. Esse comportamento introduz o atraso de propagação, que é o tempo necessário para que um sinal viaje do mestre para os dispositivos escravos. Em baixas velocidades, esse atraso é insignificante. Em altas taxas de transferência de dados, torna-se um grande problema.

Incompatibilidades no comprimento do traço entre as linhas do relógio (SCK) e dados (MOSI/MISO) causam erros de temporização. O sinal do relógio pode chegar ao receptor em um horário diferente dos dados. Isso pode fazer com que o dispositivo escravo trave o bit de dados errado, corrompendo toda a transferência. À medida que a frequência do sinal aumenta, o período do relógio fica mais curto, tornando seu design muito mais sensível a pequenas diferenças no atraso de propagação.

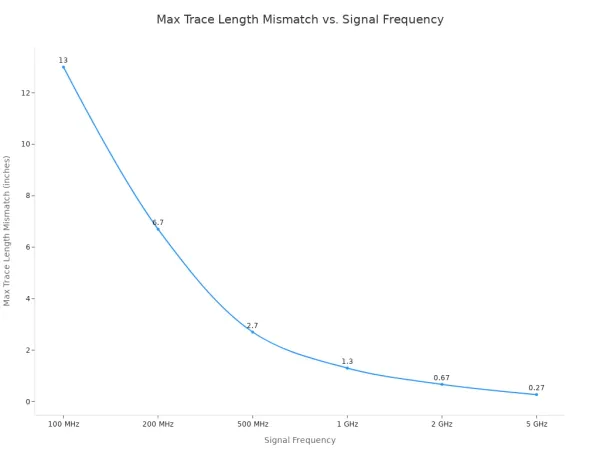

A tabela abaixo mostra a rapidez com que a tolerância à incompatibilidade do comprimento do traço diminui à medida que a frequência do relógio SPI aumenta.

| Frequência do sinal | Período do Relógio (T) | Tolerância máxima do enviesamento (20% T) | Propagação Atraso (FR4) | Max Trace Comprimento Incompatibilidade |

|---|---|---|---|---|

| 100 MHz | N 10 | 2 Ns | ~ 150 ps/dentro | ~ 13 em |

| 200 MHz | 5 n | 1 n | ~ 150 ps/dentro | ~ 6,7 dentro |

| 500 MHz | 2 Ns | 0,4 ns | ~ 150 ps/dentro | ~ 2,7 dentro |

| 1 GHz | 1 n | 0,2 ns | ~ 150 ps/dentro | ~ 1,3 dentro |

| 2 GHz | 0,5 ns | 0,1 ns | ~ 150 ps/dentro | ~ 0,67 dentro |

| 5 GHz | 0,2 ns | 0,04 ns | ~ 150 ps/dentro | ~ 0,27 dentro |

Dica Pro:Quando o barramento SPI opera na faixa de 50-100 MHz, você deve tratar os traços como linhas de transmissão. Para evitar reflexos do sinal e toque, você pode adicionar terminação pequena sérieResistências(Por exemplo, 22-33Ω) perto dos pinos do motorista. Coloque-os nas linhas SCK, MOSI e CS no mestre e na linha MISO em cada escravo.

Capacitância e Integridade do Bus

Cada elemento em seu PCB, a partir doPinos ICPara os próprios traços, adiciona uma pequena quantidade de capacitância indesejada. Isso é chamadoCapacitância parasitária-A. Existe entre o sinal traçado e seu plano de referência mais próximo, geralmente o plano do solo. Enquanto você não pode eliminá-lo, você deve gerenciá-lo.

Esta capacitância afeta diretamente o tempo de subida do sinal. O tempo de subida é a rapidez com que o sinal pode fazer a transição de uma baixa tensão para uma alta tensão.A capacitância alta do barramento atua como um obstáculo, resistindo à capacidade do sinal de subir-A. Isso retarda o tempo de subida e arredonda as bordas afiadas do sinal do relógio. Se a borda do relógio ficar muito lenta, o dispositivo escravo pode falhar em registrá-lo corretamente, limitando sua taxa de clock máxima. Curiosamente,Capacitância tem um efeito muito menor no tempo de queda do sinal-A.

Adicionar mais dispositivos escravos ao barramento SPI aumenta a capacitância de carga total, o que pode degradar ainda mais a integridade do sinal. Você pode controlar este efeito parasitário através do projeto cuidadoso do PWB.

- Use estratificações superficiais mais finasPara reduzir a distância ao plano de terra adjacente.

- Escolha materiais de baixa Dk (constante dielétrica)Para o seu PCB para diminuir a capacitância total.

- Selecione componentes com tamanhos menores do chumboPara minimizar sua contribuição.

Conversa cruzada e ruído

Conversa cruzada acontece quando a energia eletromagnética de um traço de sinal "vaza" em um traço vizinho-A. Em um PCB, isso geralmente ocorre entre dois traços SPI que funcionam lado a lado. Essa energia acoplada cria ruído no traço da "vítima". Se o ruído for grande o suficiente, ele pode causar transições de sinal falso e corromper sua transferência de dados.

Este fenômeno é principalmente devido ao acoplamento capacitivo. A melhor maneira de combater a interferência e outros ruídos externos é com um plano de solo bem projetado.

Um plano terra sólida fornece um caminho de retorno de baixa impedância para as correntes do sinal. Isso aperta os campos eletromagnéticos ao redor do traço do sinal, contendo-os e impedindo-os de interferir com outros sinais.Um plano de referência mais próximo produz acoplamento mais apertado e menos ruído-A.

Para melhorar seu design e alcançar maiores taxas de transferência, você deve:

- Maximize seu plano terrestre:Use tanto espaço livre no PCB quanto possível para o plano de terra.

- Use camadas terrestres dedicadas:Em placas multicamadas, um plano de terra dedicado oferece excelente separação e reduz o ruído.

- Adicione costura vias:Se você precisar dividir um plano de terra, use vias para "costurar" as áreas separadas, criando um caminho contínuo e de baixa impedância.

Ao gerenciar cuidadosamente seu layout de PCB, capacitância e aterramento, você pode preservar a integridade do sinal. Isso permite que você execute seu barramento SPI em uma velocidade spi mais alta e obtenha melhor rendimento geral.

O impacto do software no desempenho do SPI

Seu hardware eLayout PCBDefinir o potencial para comunicação de alta velocidade, mas seu software determina se você pode realmente alcançá-lo. As escolhas que você faz em seu código, desde as configurações básicas do protocolo até os métodos de manipulação de dados, controlam diretamente o desempenho e o rendimento do SPI final.

Modo SPI e Timing

OProtocolo SPIÉ síncrono, o que significa que os dispositivos mestre e escravo devem concordar com o tempo. Você configura esse tempo selecionando o modo SPI correto. Uma incompatibilidade aqui fará com que a transferência falhe completamente. O modo é definido por dois parâmetros na folha de dados do dispositivo escravo:

- Polaridade do relógio (CPOL):Isso define o estado ocioso do sinal do relógio (baixo ou alto).

- Fase do relógio (CPHA):Isso determina se os dados são amostrados na primeira borda do relógio (inicial) ou segunda (final).

Essas duas configurações se combinam para criar quatro modos SPI possíveis. Se o mestre estiver definido como Modo 0 (CPOL = 0, CPHA = 0), ele espera amostrar dados em uma borda de relógio crescente. Seu dispositivo escravo também deve ser configurado para este modo para garantir uma transferência de dados bem-sucedida. Começar isso errado é uma fonte comum de erros que impede a comunicação entre dispositivos.

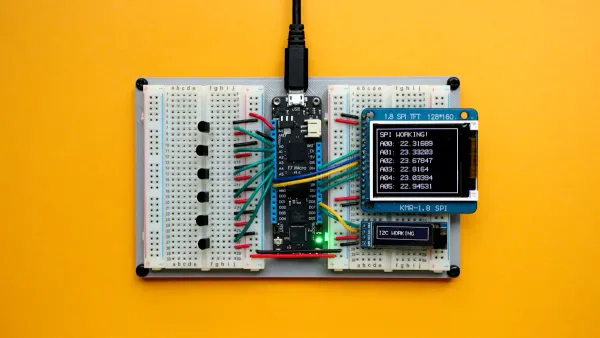

Driver e OS Overhead

Como seu microcontrolador move dados tem um enorme impacto no desempenho. Você geralmente tem duas opções para lidar com uma transferência SPI: interrupções ou acesso direto à memória (DMA). Usar interrupções é mais simples para uma transferência básica, mas cria sobrecarga significativa da CPU que limita suas taxas máximas de transferência de dados. Para alto desempenho, o DMA é o método superior.

💡O DMA permite que o periférico SPI transfira dados diretamente para ou da memória sem envolver a CPU. Isso libera a CPU para executar outras tarefas, aumentando drasticamente a eficiência do seu sistema e permitindo uma maior taxa de dados.

A tabela abaixo compara as duas abordagens:

| Característica | SPI orientado a interrupção | SPI DMA-Driven |

|---|---|---|

| Sobrecarga CPU | Alta; CPU gerencia cada byte transferência. | Baixo; CPU é livre após iniciar a transferência. |

| Rendimento | Menor; Limitado pela capacidade da CPU de atender interrupções. | Superior; Pode alcançar a velocidade SPI máxima. |

| Casos do uso | Bom para baixa taxaSensoresOu comandos simples. | Ideal para streaming de alta velocidade e grandes blocos de dados. |

Quando você precisar alcançar as taxas de transferência de dados mais altas de componentes como ADCs de alta resolução ou memória flash, use o DMA. Essa abordagem minimiza os atrasos do software e permite que o barramento SPI opere mais próximo dos limites de hardware.

Sua velocidade final do SPI depende de três fatores principais. Estes são os limites do seu hardware, suas conexões físicas e a eficiência do seu software. Você deve considerar todas as três áreas para alcançar as altas taxas de transferência de dados pelas quais o SPI é conhecido. Um sistema rápido requer uma abordagem completa.

💡Takeaway acionável:Para encontrar sua velocidade máxima verdadeira, primeiro verifique a planilha de dados do dispositivo escravo quanto ao limite de velocidade. Em seguida, teste essa velocidade com o layout e o software do PCB. Ajuste para baixo a partir daí para encontrar a taxa estável mais rápida para o seu projeto específico.