Упаковка интегральных схем: технологии, стандарты и будущие тенденции

Упаковка интегральных схем помогает решить, как полупроводники будут работать в будущем. Инженеры используют упаковку, чтобы полупроводники работали лучше. Это также помогает сделать устройства меньше и быстрее.

Упаковка интегральных схем помогает решить, как полупроводники будут работать в будущем. Инженеры используют упаковку, чтобы полупроводники работали лучше. Это также помогает сделать устройства меньше и быстрее. Индустрия началась с простой упаковки интегральных схем. Теперь он использует передовые решения для более сложных систем. Эти решения также помогают при смешивании различных типов деталей. Упаковка сейчас очень важна для улучшения полупроводников. Люди, которые наблюдают за изменениями упаковки, могут помочь создать новые идеи.

Ключевые выходы

-

Упаковка интегральной схемы обеспечивает безопасность чипов. Он соединяет разные части вместе. Это также помогает устройствам стать меньше и быстрее. Это заставляет их работать лучше и дольше.

-

Усовершенствованные методы упаковки, такие как трехмерная укладка, веерная упаковка на уровне пластины и дизайн чиплета, заставляют вещи работать лучше. Они используют меньше энергии. Они также помогают создавать более сложные системы.

-

Отраслевые стандарты JEDEC и IPC гарантируют, что упаковка и тестирование хороши. Они помогают сохранить вещи в безопасности и убедиться, что детали работают вместе.

-

Новые материалы и технологии охлаждения помогают контролировать тепло. Они также делают современные полупроводниковые пакеты дольше.

-

Компании работают вместе и продолжают изобретать новые вещи. Это помогает решить проблемы при создании чипов. Это также поможет улучшить упаковку в будущем.

Обзор упаковки интегральных схем

Цель и функции

Упаковка интегральных схемОчень важно для того, насколько хорошо работает электроника. Инженеры используютУпаковка ICСоединить чипы и другие детали. Это создает полноценную систему. Это помогает сделать вещи меньше и позволяет им работать быстрее. Меньшие детали, такие как 0201 и 01005 показать, какУпаковка ICСжимает устройства, но добавляет больше функций.

Некоторые основные работыУпаковка ICЭто:

-

Поддержка цепей и других деталей

-

Создание электрических путей для быстрых сигналов и данных

-

Обработка тепла с помощью охлаждающих инструментов, таких как микротепловые трубки

-

СохранениеICБезопасен от повреждений и окружающей среды

-

Помощь в укладке деталей в 3D с системой на упаковке и пакетом на упаковке

-

Обеспечение более длительного срока службы с помощью сильных испытаний и новых материалов

Инженеры ищут новые материалы, такие какУглеродные нанотрубки, СделатьУпаковка ICЛучше. Субстрат вУпаковка ICТакже является ключом к тому, чтобы сделать вещи меньше и работать лучше.

Эволюция упаковки IC

ИсторияУпаковка ICПоказывает, как быстро изменились полупроводники. В 1970-х годах мульти-чиповые модули начали смешивать разные части. СтарыеУпаковка ICПути изменились на новые, которые ставят логику,Память,Датчики, И антенны вместе. Закон Мура не мог идти в ногу только с 2D, поэтому индустрия перешла на трехмерную укладку и смешивание деталей.

Новые идеи, такие как сквозные кремниевые переменные, интерпозеры иУпаковка на уровне пластины с вентиляторомИзмененоУпаковка IC. Это позволяет устройствам работать лучше, уменьшаться и делать больше. Теперь дизайн устройств, пакетов и печатных плат работает вместе для пользовательских решений в области высокоскоростных вычислений и IoT. Это изменение показывает какУпаковка интегральной схемыОт простых коробок к сложным системам с множеством технологий.

Снимок отрасли:

Ключевая статистика

Детали

Размер рынка (2024)

Прогнозируемый размер рынка (2033)

90,18 млрд долларов США

КАГР (2025-2033)

9,35%

Крупнейший региональный рынок

Азиатско-Тихоокеанский регион

Самый быстрорастущий регион

Северная Америка

Доминирующий Тип Сегмента

Органические субстраты

Доминирующий сегмент конечного пользователя.

Бытовая электроника

Ключевые технологии упаковки

СОП, ДФН, ГА, ФОВЛП

Драйверы рынка

Спрос на бытовую электронику, 5G, инновации в упаковке

Основные игроки рынка

Amkor, ASE Group, Henkel, Hitachi Chemical, Sumitomo Bakelite, LG Chem, Powertech, Toray

Заметные тенденции

Принятие FOWLP для производительности и миниатюризации

Основные региональные

Промышленность Китая выросла на 18,5% в 2023 году; США лидирует в Северной Америке с долей 75%

Стратегические факторы

R & D, сотрудничество, правительственные инициативы

Технологии упаковки ИС

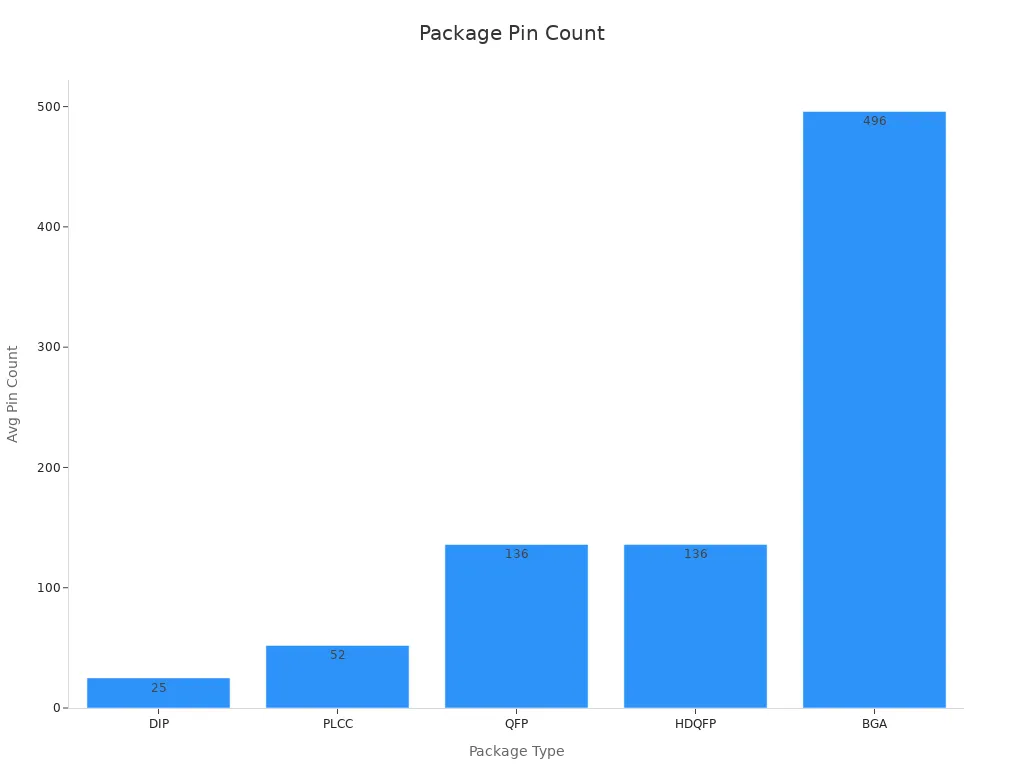

Традиционные пакеты

Инженеры стали использовать традиционныеУпаковка ICВ течение многих лет. Эти пакеты помогают защитить и подключить чипы. Некоторые общие типы двойной встроенный пакет (ПОГРУЖЕНИЕ), несущая (PLCC) обломока пластмассы этилированная, и пакет (QFP) квада плоский. Каждый тип лучше всего подходит для определенных устройств.

-

DIP имеет два ряда штифтов. Он может иметь от 8 до 42 контактов.Штифты расположены на расстоянии от 1778 до 2,54 мм друг от друга. DIP хорош для монтажа через отверстия. Керамические DIP очень надежны.

-

PLCC имеет J-образные выводы. Он может иметь от 20 до 84 контактов. PLCC экономит место и может быть установлен на поверхностях или в розетках.

-

У QFP есть зацепок в виде крыла чайки. Он может иметь от 32 до 240 контактов. Расстояние между выводами может быть всего 0,4 мм. QFP выставил колодки, чтобы помочь с нагревом.

Эти традиционныеУпаковка ICТипы зрелые и стоят дешевле. Они хорошо работают для многих применений. Но у них есть ограничения по количеству контактов, размеру и тому, насколько хорошо они работают. Поскольку устройства становятся все меньше и сложнее, инженерам нужны новые способы упаковки чипов.

Примечание:ТрадиционныеУпаковка ICИспользует более длинные соединения. Это может вызвать большую потерю сигнала и более низкую плотность.

|

Тип упаковки |

Диапазон подсчета контактов |

Диапазон шага (мм) |

Размеры корпуса (мм) |

Диапазон толщины (мм) |

Основные характеристики производительности |

|---|---|---|---|---|---|

|

ДИП |

8 - 42 |

1778-2,54 |

Ширина: 6,35-13,97 |

0,81-12,96 |

Зрелый, недорогой, монтаж через отверстие, керамические версии для высокой надежности |

|

PLCC |

20 - 84 |

1,27 |

Ширина/Длина: 9-29,28 |

3,56-4,57 |

J-образные выводы, поверхность или гнездо, компактная форма выводов |

|

КФП |

32 - 240 |

0,4-0,8 |

Ширина/Длина: 5-45,7 |

1-4,9 |

Выводы крыла чайки, поверхностный монтаж, керамические версии для высокой надежности, открытые площадки для теплоотвода |

Передовые решения

Усовершенствованная упаковка изменила то, как инженеры проектируютУпаковка IC. Эти новые способы включают Ball Grid Array (BGA), Chip Scale Package (CSP), Wafer-Level Package (WLP), Fan-Out Wafer-Level Package (FOWLP) и System-in-Package (SiP). Они помогают сделать соединения короче, добавить больше контактов и улучшить сигналы.

-

BGA использует шарики припоя вместо выводов. Он может иметь до 975 контактов. BGA обеспечивает лучшие тепловые и электрические характеристики.

-

CSP и WLP делают пакет почти таким же маленьким, как чип. Это позволяет сделать устройства еще меньше.

-

FOWLP позволяет помещать больше деталей в одну упаковку. Это также помогает с теплом.

-

SiP ставит разныеICТипы, как логика, память, и РФ, совместно. Это помогает создавать сложные устройства.

Инженеры используют эти передовые способы для быстрого сбора данных, небольшого размера и лучшего контроля тепла. Эти методы также сокращают помехи и делают устройства более надежными.Склеивание флип-чипа и сквозные кремниевые переходы (TSV)Сделать крошечные соединения. Эти функции помогают сигналам и уменьшают нежелательные эффекты.

-

В смартфонах, продвинутыеУпаковка ICОбъединяет процессоры, память и радиочастотные модули. Это делает телефоны мощными и маленькими.

-

В автомобилях прочные модули SiP помогают электронике работать в трудных местах.

-

В центрах обработки данных быстрые процессоры используют расширенную упаковку для лучшей скорости и меньшего энергопотребления.

Подсказка:ПродвинутыйУпаковка ICПозволяет складывать чипы и использовать более короткие соединения. Это означает более высокую скорость, меньшую задержку и лучшую производительность.

3D IC упаковка

3DУпаковка ICЭто большой шаг в технологии чипов. Этот метод стековICСлои друг на друга. Он использует такие вещи, как сквозные кремниевые сквозные и кремниевые интерпосеры. Инженеры используют 3DУпаковка ICДля более высокой плотности, лучших сигналов и меньшего энергопотребления.

-

В 2024 годуОтправлено более 42 миллиардов штабелей 3D-штабелей. Это показывает, что многие люди используют 3DУпаковка ICСейчас.

-

3D пакеты могут иметь до 2300 соединений на см².

-

FOWLP имеет тепловое сопротивление до 0,6 ° C/Вт. Это помогает с теплом.

-

3D-упаковка теперь составляет 28% дохода от логических чипов.

|

Метрика/тренд |

Значение/Статистика |

Описание |

|---|---|---|

|

3D-штабелированный умирают единиц отправлены (2024) |

Более 42 миллиардов |

Быстрое внедрение упаковки 3D IC |

|

Плотность межсоединений в 3D пакетах |

2300 входов/выходов на см² |

Повышенная плотность интеграции |

|

Тепловое сопротивление в FOWLP |

0,6 ° C/Вт |

Улучшенные тепловые характеристики |

|

Доля доходов от 3D-упаковочной упаковки |

28% от общего дохода от логических чипов |

Значительный вклад рынка |

|

AI ускорители с использованием усовершенствованной упаковки |

Более 72% (2024) |

Высокое внедрение в сегментах производительности |

|

Улучшение целостности сигнала (FO-PLP) |

30% лучше чем FO-WLP |

Улучшенное качество сигнала |

|

Снижение паразитной индуктивности |

24% снижение |

Прирост электрических характеристик |

|

Улучшение сопротивления TSV |

19% лучше |

Достижения в технологии вертикального соединения |

|

Экономия энергии благодаря упаковке чиплета |

18% средняя экономия |

Повышение энергоэффективности |

|

Умирают штабелируя уровни в коммерчески DRAM |

До 8 слоев |

Продвижение в вертикальной интеграции |

Инженеры используют чиплетные конструкции для создания сложных систем с небольшими многоразовыми блоками. Упаковка чипов позволяет им смешивать различные функции, такие как логика, память и аналоговые, в одном SiP. Это помогает сторонним дизайнам чипов и ускоряет разработку продуктов.

-

Упаковка чиплета делает соединения короче и лучше сигнализирует.

-

Технология встроенных штампов сокращает задержку на 22% и экономит до 18% энергии.

-

Шаг удара флип-чипа теперь составляет около 80 мкм в дизайнах sub-5nm. Это помогает сделать вещи меньше.

Примечание:Рынок передовой упаковки в 2024 году составил 70,3 миллиарда долларов. Он рос на 13,2% каждый год. К 2026 году более 40% прибыли от процессоров будет приходиться наУпаковка ICУлучшений.

Инженеры используют решения SiP и Chiplet для новых устройств. Эти способы помогают сделать устройства меньше, быстрее и дешевле. Поскольку отрасль растет,Упаковка ICБудет еще важнее для лучшей производительности и новых идей.

Отраслевые стандарты

ДЖЕДЕК и МПК

JEDEC и IPC составляют важные правила для упаковки интегральных схем. Эти группы пишут документы, чтобы помочь компаниям разрабатывать и тестировать продукты. JEDEC устанавливает правила для полупроводниковых устройств. IPC устанавливает правила для печатных плат и сборок. Они работают вместе, чтобы обеспечить безопасность и высокое качество продукции.

|

Стандарт/Название документа |

Стандартный номер |

Дата |

Цель |

Комитет (ы) |

|---|---|---|---|---|

|

Классификация чувствительности влаги/оплавки для Не-герметичных СМДс |

J-STD-020F |

Декабрь 2022 |

Определяет уровни чувствительности к влаге для безопасной упаковки и обращения |

JC-14, JC-14.1 |

|

Обработка, упаковка, доставка и использование чувствительных к влаге/оплавлению SMD |

J-STD-033D |

Апр 2018 |

Стандартизирует обработку и транспортировку для предотвращения повреждений |

JC-14, JC-14.1 |

|

Предварительное кондиционирование негерметичных устройств для поверхностного монтажа перед испытанием на надежность |

JESD22-A113I |

Апр 2020 |

Устанавливает поток предварительной подготовки для тестирования надежности |

JC-14.1 |

|

Измерение коробления пакета микросхем для поверхностного монтажа при повышенной температуре |

JESD22-B112C |

Ноя 2023 |

Измеряет коробление пакета во время пайки |

JC-14, JC-14.1 |

|

Тестовая плата адаптера Рекомендации по тестированию надежности |

JEP176A |

Июнь 2025 |

Проводит тесты надежности для микросхем с адаптерными платами |

JC-14, JC-14.3 |

Эти правила помогают компаниям делать меньше ошибок и лучше работать вместе. Они также помогают компаниям соблюдать законы для медицинской, автомобильной и домашней электроники.

Качество и совместимость

Качество и совместимость очень важны для упаковки интегральных схем.Правила IPC, такие как IPC-A-600 и IPC-6012Установите четкие шаги для хорошего внешнего вида и производительности. В таблице ниже показаны некоторые основные правила IPC и то, что они делают:

|

Стандарт IPC |

Область фокусировки |

Роль в проверке надежности технологии упаковки ИС |

|---|---|---|

|

IPC-A-600 |

Визуальная приемлемость печатных плат |

Обеспечивает только бездефектный осмотр пропуска ПКБс, поддерживая упаковывая надежность. |

|

IPC-6012 |

Квалификация и эксплуатационные характеристики жестких печатных плат |

Определяет требования к долговечности и долгосрочной надежности. |

|

IPC-A-610 |

Приемлемость электронных сборок |

ГидыСборкаКачество, пайка и размещение компонентов. |

|

IPC-2221 |

Общий стандарт на дизайн печатной платы |

Устанавливает лучшие практики для уменьшения ошибок и улучшения согласованности. |

|

IPC-7711/7721 |

Переработка, модификация и ремонт |

Предлагает безопасные процессы переделки и ремонта, сохраняя качество после модификаций. |

Тестирование важно для обеспечения того, чтобы продукты хорошо работали вместе:

-

Встроенные алгоритмы самотестирования.Найти проблемы в быстрых соединениях.

-

Мониторы целостности сигнала проверяют работность звеньев микросхемы.

-

Излишние и ремонт используют дополнительные полосы для поддержания сильных сигналов.

-

Функции высокоскоростного доступа и тестирования помогают тестировать чипы на каждом этапе.

-

Экологическое тестирование проверяет, как чипы работают с изменениями тепла, мощности и процесса.

Компании используют эти правила и тесты, чтобы убедиться, что их продукты сильны и хорошо работают на важных работах.

Тенденции в упаковке IC

3D интеграция

3D интеграция-большой тренд вУпаковка IC. Этот метод складывает многоICСлои друг на друга. Они соединяют слои специальными звеньями, называемыми сквозными кремниевыми переходами. Компании используют 3D-штабелирование, чтобы устройства работали лучше и потребляют меньше энергии. Это также помогает сделать устройства меньше. Индустрия проверяет прогресс с ключевыми цифрами, такими какУпаковка, производительность, мощность, профиль, стоимость и время цикла. Даг Ю из TSMC сделал эти цифры, чтобы помочь направлять новые идеи.

|

Аспект |

Детали |

|---|---|

|

Ключевые показатели эффективности (KPI) |

Упаковка, производительность, мощность, профиль, стоимость, время цикла (PPCC) |

|

Проблемы усыновления |

Технология TSV не получила широкого распространения в чувствительных к затратам мобильных приложениях из-за стоимости и технических проблем |

|

Закрытие Quimonda в 2008 году задержало принятие штабелирования DRAM |

|

|

Конкуренция со стороны веерной упаковки на уровне пластины (FOWLP) вытеснила некоторые 3D IC. |

|

|

Примеры усыновления |

Некоторые смартфоны используют 3D-микросхемы на основе TSV, что указывает на объем производства. |

|

Вехи |

SK Hynix представила стеки 3D TSV DRAM (HBM) в 2015 году |

|

Интеграция 3D-систем через штабелирование пластин (W2W) и матрицы (D2W) ожидается примерно в 2022 году. |

|

|

Будущие события |

Гибридное склеивание и масштабирование шага для повышения урожайности и производительности при штабелировании D2W |

|

Отраслевая дорожная карта и экспертный консенсус поддерживают текущие достижения в области 3D-интеграции |

Инженеры продолжают работать над устранением затрат и технических проблем в 3D-интеграции. Гибридное соединение и масштабирование шага могут помочь сделать больше чипов и повысить производительность. Многие смартфоны теперь используют 3DУпаковка IC, Так что эта тенденция сейчас распространена. Эксперты считают, что 3D-интеграция будет продолжать расти по мере появления новых чипов.

Вентилятор-выход и вафельный уровень

Веер-вне на уровне вафли упаковка и на уровне вафли упаковка масштаба обломока изменялиУпаковка ICМного. Эти новые типы помогают сделать устройства меньше и упаковать в большее количество деталей. Рынок упаковки для микросхем вафельных уровней былПочти 4,9 млрд долларов в 2023 году. Он может вырасти до более чем 37 миллиардов долларов к 2031 году. Этот быстрый рост показывает, что многие компании используют эти новые способы.

-

Вентилятор WLCSP позволяет устройствам быть меньше и дешевле с большим количеством деталей.

-

Веерная вафельная упаковка добавляет больше ввода-вывода за счет распределения проводов за пределы чипа. Это помогает с нагревом и позволяет подогреть больше деталей.

-

Лучшая технология шага и новые материалы помогают сделать более хорошие чипы и снизить затраты.

-

Более короткие соединения и лучший контроль нагрева позволяют устройствам работать лучше и прослужить дольше.

📈Отраслевой взгляд:

Упаковка на уровне пластины с разветвителем и упаковка для микросхем на уровне пластины помогают сделать устройства меньше и повысить выход микросхем. Эти способы позволяют компаниям создавать более мелкие и более мощные устройства за меньшие деньги.

Инженеры используют эти типы упаковки для телефонов, носимых устройств и автомобильной электроники. Толчок к меньшим и лучшим устройствам продолжает управлять новымиУпаковка ICИдеи.

Гетерогенная интеграция

В настоящее время гетерогенная интеграция является основной тенденцией вУпаковка IC. Этот способ ставит разныеICТипы, материалы и задания в одной упаковке. Инженеры используют сквозные кремниевые отверстия, чтобы связать множество микросхем на подложке. Это нарушает старые ограничения размера. Это также помогает сделать системы дешевле и позволяет работать системам на основе чипетов.

Новый3D гетерогенная интеграцияПозволяет микросхемам подключаться при очень малых размерах, даже до субмикрон. В настоящее время в отрасли используется 3D-штабелирование, смешивание многих рабочих мест и гибридная интеграция. Эти изменения обеспечивают высокую плотность, меньшее энергопотребление, меньший размер и лучшую надежность.

Дизайн чиплетов очень важен для этой тенденции. Дизайнеры могут выбирать чипы для логики, памяти или аналоговых заданий. Это делает решения системы-в-пакете гибкими и быстрыми в построении. Это также помогает новым продуктам выйти быстрее и поддерживает новые идеи в чипах.

💡Подсказка:

Гетерогенная интеграция и чиплетные конструкции помогают инженерам делать сложные системы быстрее и проще. Эта тенденция удовлетворяет потребность в небольшой, мощной электронике.

Передовые материалы

Передовые материалыЗа многими новыми тенденциями вУпаковка IC. Инженеры выбирают материалы, которые хорошо перемещают тепло, лучше работают с электричеством и служат дольше. Эти материалы помогают с высокой мощностьюICПотребности. Медные звенья, диэлектрики с низким содержанием k и новые подложки делают возможными новые типы упаковки, такие как 3D-упаковка и упаковка на уровне пластин.

-

Новые охлаждающие материалы, такие как микрофлюидное охлаждение и встроенные тепловые трубки, помогают сохранять стружку прохладной и прослужить дольше.

-

Лучшие материалы термоинтерфейса помогают микросхемам обрабатывать больше тепла.

-

Гетерогенная интеграция использует много полупроводниковых материалов в одном корпусе. Это повышает производительность и снижает энергопотребление.

-

Промышленность делает перерабатываемую и зеленую упаковку, чтобы помочь планете.

-

Упаковка должна обрабатывать тепло, мощность, изменения температуры и проблемы сигнала, такие как EMI и перекрестные помехи.

-

Небольшие устройства нуждаются в крошечных, сложных пакетах, которые все еще работают хорошо и стоят дешевле.

Инженеры продолжают искать новые материалы, чтобы помочь новым технологиям и конструкциям микросхем. Эти усилия обеспечиваютУпаковка ICИдет в ногу с тем, что нужно современным чипам.

🔍Примечание:

Переход к передовым материалам и новым способам упаковки будет определять будущееУпаковка IC. Компании, которые работают в этих областях, приведут к следующим большим изменениям в чипах.

Проблемы и соображения

Сложность производства

Упаковка интегральных схем имеет много проблем при изготовлении продуктов. Индустрия должна следовать многим шагам и строгим правилам. Исследования показывают некоторые большие проблемы в создании этих продуктов:

-

Не достаточно полупроводниковых заводовОзначает, что будет сделано меньше фишек. Это замедляет новые технологии.

-

Опора на детали из других стран может вызвать проблемы с цепочкой поставок.

-

Жесткие правительственные правила затруднят строительство новых заводов. Это замедляет рынок.

Эти вещи делают его труднее сделать больше упаковки. Компании должны покупать лучшие машины и нанимать квалифицированных рабочих. Для этой работы необходимы чистые помещения и специальные инструменты. Поскольку упаковка становится лучше, каждый шаг должен соответствовать более высоким стандартам.

Тестирование и надежность

Тестирование и надежность очень важны в упаковке. Компании используют новые системы контроля качества для получения лучших результатов. К примеру:

-

Компания на Тайване протестировалаНовая система контроля качества в реальном времени.

-

Система использует специальные методы для поиска лучших настроек.

-

Это помогает делать лучшие продукты и меньше ошибок.

-

Проверки качества смотрят на то, насколько хорошо работают тесты зонда цепи.

-

Система помогает умным фабрикам поддерживать высокие стандарты перед упаковкой.

Эти способы помогают компаниям найти проблемы на ранней стадии и убедиться, что продукты работают хорошо. Поскольку чипы становятся меньше, тестирование должно быть еще более тщательным.

Стоимость и масштабируемость

Стоимость и масштабируемость-большие проблемы в упаковке. Новая упаковка требует дорогостоящих материалов и машин. Компании должны пробовать новые вещи, но и поддерживать низкие цены. Создание большего количества продуктов может использовать деньги и ресурсы. Небольшие компании могут иметь проблемы с конкуренцией с более крупными. Промышленность ищет способы сэкономить деньги, но по-прежнему делать хорошие продукты и удовлетворять спрос.

Экосистемное сотрудничество

Экосистемное сотрудничество помогает упаковке двигаться вперед. Одна компания не может сделать все в одиночку. Сотрудничество с поставщиками и производителями оборудования помогает создавать новые идеи. Совместное использование правил и открытый разговор позволяют легче решать проблемы и работать быстрее. Командная работа также помогает с проблемами цепочки поставок и держит части приходят.

💡Хорошая командная работа в экосистеме обеспечивает более быстрый прогресс и лучшие упаковочные решения.

Упаковка интегральных схем по-прежнему очень важна для полупроводников. В таблице ниже показано, как упаковка помогает отрасли расти и меняться:

|

Метрика/тренд |

Детали |

|---|---|

|

~ $697 млрд |

|

|

Темпы роста рынка (2025-2030) |

7%-9% ежегодно |

|

Ключевые технологии |

Штабелирование 3D, система-в-пакет, упаковка уровня веера-вне вафли |

Люди, которые следят за тенденциями упаковки, могут идти в ногу с новыми потребностями. Они также могут помочь привести новые технологии. Упаковка будет оставаться важной для повышения производительности и новых применений в будущем.

Часто задаваемые вопросы

Что такое упаковка интегральных схем и почему это важно?

Упаковка интегральной схемы защищает чипы от повреждений. Он соединяет чипы с другими частями в устройстве. Это также помогает отвода тепла от чипа. Это заставляет устройства работать лучше и работать дольше. Инженеры используют упаковку, чтобы сделать электронику сильнее и быстрее.

Как передовые технологии упаковки улучшают производительность полупроводников?

Передовые упаковочные технологии делают соединения короче. Это помогает сигналам двигаться быстрее и лучше. Эти способы позволяют большему количеству деталей поместиться в небольшом пространстве. Устройства могут работать быстрее и потребить меньше энергии. Это позволяет электронике хорошо работать и экономить энергию.

Что такое конструкции на основе чиплета и почему они популярны?

В конструкциях на основе чиплетов используются небольшие блоки, называемые чиплетами. Инженеры могут смешивать разные чипы в одном пакете. Это помогает быстрее создавать новые устройства. Дизайн чиплета позволяет компаниям использовать детали от других. Универсальный чиплет Interconnect Express помогает связать чиплеты вместе.

Какие стандарты определяют процессы упаковки и производства IC?

JEDEC и IPC составляют правила для упаковки и тестирования IC. Эти правила помогают компаниям производить хорошие и безопасные продукты. Они также помогают различным компаниям работать вместе. Правила поддерживают новые способы изготовления и тестирования упаковки IC.

Какие тенденции формируют будущее IC-упаковки?

Тенденции включают 3d штабелирование, системы чиплет, и новые материалы. Инженеры используют их для создания небольших и быстрых устройств. Индустрия также работает над зеленой упаковкой, чтобы помочь планете. Новые идеи помогают электронике работать лучше и прослужить дольше.