Quy trình thiết kế asic: Hướng dẫn từng bước để tạo ra ứng dụng mạch tích hợp cụ thể

Quy trình thiết kế asic Giúp làm chip cho các mục đích sử dụng đặc biệt. Không giống như Bộ xử lý thông thường, Asics mang lại hiệu suất cao cho các tác vụ cụ thể.

The Quy trình thiết kế asicGiúp làm chip cho mục đích sử dụng đặc biệt. Không giống như Bộ xử lý thông thường, Asics mang lại hiệu suất cao cho các tác vụ cụ thể. Các chip tùy chỉnh này hoạt động tốt hơn, chi phí thấp hơn, và làm nhiều hơn nữa.AsicCác bước Thiết kế cần lập kế hoạch và làm việc cẩn thận. Chúng rất quan trọng đối với các ngành công nghiệp như ô tô, điện thoại và đồ dùng. Ví dụ, xe điện sử dụng Asics để quản lý năng lượng và nói chuyện với các bộ phận. Các bước rõ ràng trong thiết kế asic giúp tạo ra các chip đáng tin cậy và tiết kiệm năng lượng cho các nhu cầu ngày nay.

Mang theo chìa khóa

-

Mục tiêu rõ ràng là rất quan trọng. Họ hướng dẫn thiết kế asic và ngăn ngừa những sai lầm lớn.

-

Kiểm tra chức năng của chip đảm bảo nó hoạt động đúng. Bước này tìm ra vấn đề sớm, tiết kiệm thời gian và tiền bạc.

-

Sử dụng các công cụ thông minh để mã hóa và bố trí giúp ích rất nhiều. Những công cụ này tạo ra chip mạnh mẽ và nhanh chóng.

-

Thiết kế thân thiện với thử nghiệm giúp việc thử nghiệm dễ dàng hơn. Họ giúp tìm và khắc phục vấn đề sớm để con chip hoạt động tốt sau này.

-

Cần có một tệp gdsii tốt để làm chip. Nó đảm bảo thiết kế tuân thủ các quy tắc của nhà máy và hoạt động tốt.

Đặc điểm kỹ thuật và Tạo mã RTL

Thông số kỹ thuật cài đặt

Bước đầu tiên trong việc thực hiện asic là cài đặt thông số kỹ thuật. Điều này có nghĩa là quyết định những gì chip Nên Làm, nó nên hoạt động nhanh như thế nào, và bất kỳ giới hạn nào nó có. Bước này giúp quá trình thiết kế được tổ chức và đi đúng hướng. MộtThông số kỹ thuật rõ ràng hoạt động như một kế hoạchHướng dẫn toàn bộ dự án. Nó giúp tránh những sai lầm có thể làm chậm công việc hoặc tăng chi phí. Bước này thường mất từ 2 đến 6 tuần vì cần chú ý cẩn thận.

Thông số kỹ thuật cũng giúp bạn tìm ra các tính năng chính của chip. Ví dụ: Nếu bạn đang làm một con chip cho điện thoại thông minh, bạn có thể tập trung vào việc tiết kiệm năng lượng và làm việc nhanh hơn. Thông số kỹ thuật rõ ràng, đảm bảo chip hoạt động đúng chức năng của nó.

Viết mã RTL

Sau khi cài đặt thông số kỹ thuật, bạn có thể bắt đầu viết mã RTL (đăng ký mức chuyển). Mã này Hiển thị cách chip hoạt động và được xây dựng. Nó sử dụng các ngôn ngữ đặc biệt như verilog hoặc vhdl. Mã RTL biến các thông số kỹ thuật thành mô hình hoạt động của chip.

Ở giai đoạn này, bạn cần kiểm tra xem mã RTL có khớp với thông số kỹ thuật không. Kiểm tra thường giúp tìm lỗi sớm và tiết kiệm thời gian sau. Ví dụ, sử dụng các điểm kiểm tra trong quá trình gỡ lỗi có thể giúp tìm thấy các bộ phận bị thiếu hoặc lỗi nhanh hơn, làm cho quá trình mượt mà hơn.

Công cụ cho thông số kỹ thuật và mã RTL

Có những công cụ để giúp thiết lập thông số kỹ thuật và viết mã RTL. Những công cụ này giúp quá trình dễ dàng hơn và cải thiện thiết kế. Ví dụ: Công cụ mô phỏng cho phép bạn kiểm tra mã RTL để đảm bảo nó hoạt động như kế hoạch.

Một Nghiên Cứu trường hợp cho thấy các công cụ RTL hữu ích như thế nào. Gỡ lỗi với các điểm kiểm tra giúp tìm ra vấn đề nhanh hơn chỉ sử dụng Nhật ký. Cái nàyCải thiện tốc độ truyền từ 72.4% đến 93.6%. Nó cho thấy các công cụ tiên tiến có thể làm cho thiết kế asic tốt hơn như thế nào.

|

Cấu hình |

Tỷ lệ vượt qua (%) |

Cải thiện (%) |

|---|---|---|

|

Llm Vanilla |

72.4 |

Không có |

|

Chất Đơn |

83.9 |

11.5 |

|

Đa tác nhân |

93.6 |

21.2 |

Sử dụng những công cụ này có thể làm cho asic của bạn đáng tin cậy hơn và hoạt động tốt hơn.

Xác minh chức năng

Kiểm tra xác minh Chức năng nếu chip hoạt động như kế hoạch.Nó đảm bảo chip đáp ứng được mục tiêu của mình và tránh những sai lầm. Bỏ qua bước này có thể gây thất bại, Lãng Phí tiền bạc và làm khách hàng khó chịu. Xác minh sớm giúp bắt lỗi và làm cho chip đáng tin cậy hơn.

Đảm bảo thiết kế đúng

Bước này đảm bảo chip phù hợp với kế hoạch của nó và hoạt động tốt. Nó làm giảm Rủi Ro như chip vỡ hoặc hiệu suất kém. Đối với các công ty không có nhà máy, nó xây dựng lòng tin của khách hàng bằng cách cung cấp chip tốt. Các nhà máy cũng mất ít vật liệu hơn khi xác minh thiết kế.

-

Tại sao việc xác minh chức năng lại quan trọng:

-

Đảm bảo chip tuân theo kế hoạch của nó.

-

Giảm nguy cơ gặp sự cố về chip.

-

Xây dựng lòng tin của khách hàng.

-

Tiết kiệm vật liệu trong quá trình sản xuất.

-

Sử dụng mô phỏng

Mô phỏng kiểm tra chip trong các tình huống khác nhau. Họ tìm thấy vấn đề trước khi chế tạo chip. Các thử nghiệm này kiểm tra cách chip hoạt động và hoạt động. Các phương pháp như kiểm tra logic và kiểm tra chính thức là phổ biến cho bước này.

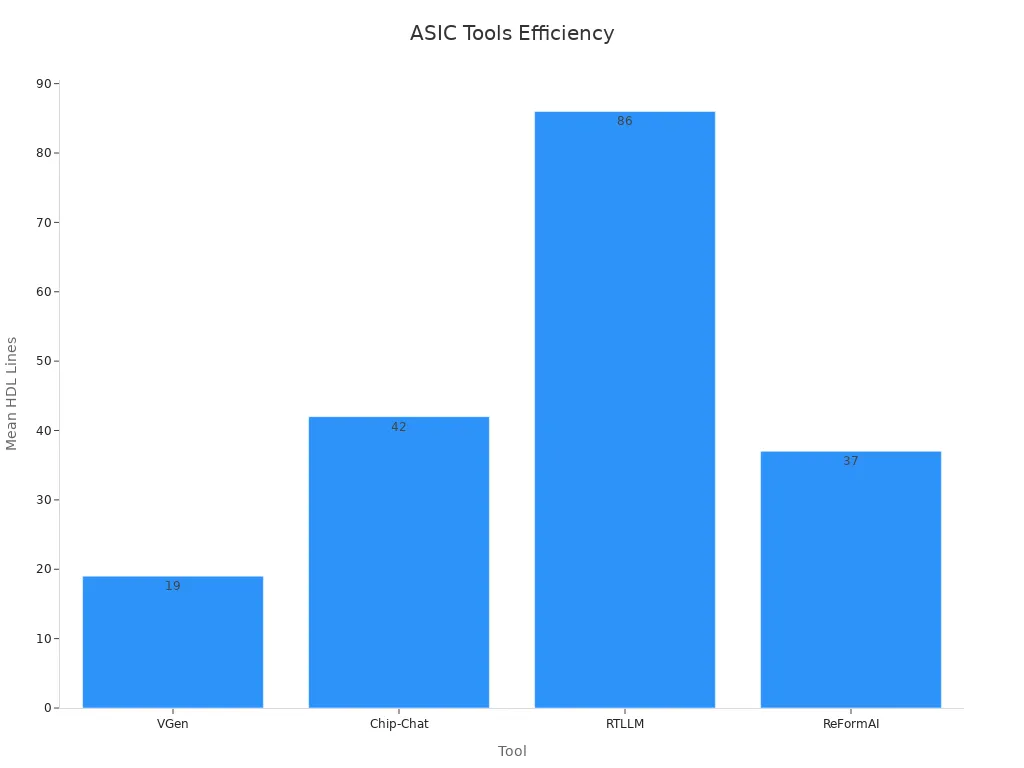

Ví dụ, các công cụ như vgen và rtllm giúp kiểm tra chip có kích cỡ khác nhau.Bảng dưới đây cho thấy các công cụ này xử lý các lượng mã khác nhau như thế nào:

|

Dụng cụ |

Thiết kế đã được thử nghiệm |

Tổng số dòng mã |

Đường trung bình |

Max Lines |

Tổng số dòng mã |

|---|---|---|---|---|---|

|

Vgen |

17 |

0.3k |

19 |

48 |

0.3k |

|

Trò chuyện chip |

8 |

0.3k |

42 |

72 |

0.3k |

|

Rtllm |

30 |

2.5K |

86 |

518 |

2.5K |

|

Reformai |

30 |

2227k |

37 |

773 |

2227k |

Dụng cụ kiểm tra thiết kế

Công cụ đặc biệt giúp việc kiểm tra thiết kế dễ dàng và tốt hơn. Những công cụ này tìm và khắc phục sự cố một cách nhanh chóng. Chúng cũng giúp con chip đạt được mục tiêu và hoạt động tốt.

Biểu đồ dưới đây cho biết các công cụ khác nhau có thể xử lý bao nhiêu mã:

Sử dụng các công cụ này giúp quá trình kiểm tra nhanh hơn và cải thiện thành công của chip.

Danh sách Mạng RTL sang cổng cấp

Tổng Hợp là gì?

Tổng Hợp là một bước quan trọng trong việc tạo ra Asics. Nó thay đổi mã RTL (đăng ký mức chuyển) thành danh sách Mạng cấp cổng. Danh sách mạng này hiển thị cổng logic vật lý của chip. Tổng hợp kết nối Ý tưởng thiết kế với chip thật. Nó đảm bảo chip có thể được chế tạo và vẫn hoạt động như kế hoạch.

Trong tổng hợp, thiết kế được cải thiện về tốc độ, kích thước và sức mạnh. Những cải tiến này giúp con chip đạt được mục tiêu mà không làm mất hiệu suất. Ví dụ, các công cụ tổng hợp biến mã RTL thành các tế bào tiêu chuẩn từ thư viện. Điều này tạo ra một thiết kế vừa tốt vừa dễ thực hiện.

RTL trở thành một netlist cấp cổng Như Thế Nào

Thay đổi RTL sang danh sách Mạng cấp cổng có các bước. Đầu tiên, công cụ tổng hợp biến mã RTL thành thiết kế cấp cổng cơ bản. Sau đó, thiết kế được cải thiện để làm cho nó nhanh hơn, sử dụng ít năng lượng hơn và hoạt động tốt hơn. Cuối cùng, danh sách mạng được kiểm tra để phù hợp với kế hoạch ban đầu.

Quá trình này cũng tuân thủ các quy tắc như giới hạn thời gian và kích thước. Những quy tắc này đảm bảo chip hoạt động tốt trong cuộc sống thực. Ví dụ, khi chế tạo CPU hoặc chip mật mã, các công cụ tổng hợp phục hồi các thanh ghi rất tốt.Bảng dưới đây cho thấy các công cụ tổng hợp hoạt động tốt như thế nào cho các thiết kế khác nhau:

|

Loại thiết kế kim loại |

Tỷ lệ phục hồi |

Ghi chú |

|---|---|---|

|

Đồng xử lý mật mã |

Gần như hoàn hảo |

Phục hồi đăng ký mức cao hiệu quả |

|

CPU |

Gần như hoàn hảo |

Hoạt động tốt trên nhiều thiết kế |

|

Opentitan (SoC) |

Gần như hoàn hảo |

Được hỗ trợ bởi các chuyên gia trong ngành |

Công cụ tạo danh sách mạng cổng

Nhiều công cụ giúp tạo danh sách Mạng cấp cổng cho Asics. Những sản phẩm phổ biến là Trình biên dịch thiết kế synopsys, cadence Genus và mentor Graphics Precision. Những công cụ này giúp tổng hợp dễ dàng và chính xác hơn. Họ cũng kiểm tra thời gian và cải thiện việc sử dụng năng lượng, đó là chìa khóa cho chip tốt.

Sử dụng những công cụ này giúp tổng hợp nhanh hơn và giảm sai sót. Ví dụ, Trình biên dịch thiết kế synopsys kiểm tra thời gian và tăng hiệu suất. Cadence Genus giúp sử dụng năng lượng thấp hơn, làm cho nó trở thành một công cụ tuyệt vời cho thiết kế asic.

Bố trí thiết kế asic

Thiết kế bố cục cơ bản

Cách bố trí của một asic giống như một bản đồ cho cấu trúc của nó. Nó cho thấy các bộ phận đi đâu và cách chúng kết nối. Bố trí tốt giúp chip hoạt động tốt, sử dụng ít năng lượng hơn và đạt được mục tiêu của nó. Bước này rất quan trọng vì nó ảnh hưởng đến độ tin cậy và hữu ích của chip.

Trong bước này, bạn phải suy nghĩ về nhiều thứ. Chúng bao gồm vị trí đặt cổng, cách kết nối chúng và tuân theo các quy tắc thiết kế. Mọi lựa chọn đều thay đổi cách con chip hoạt động và cách dễ dàng thực hiện. Ví dụ, một bố cục nhỏ hơn có thể làm cho tín hiệu nhanh hơn và tiết kiệm điện.

Các bước thực hiện bố trí

Tạo bố cục có nhiều bước để biến thiết kế thành một con chip thật. Đầu tiên, quy hoạch sàn tổ chức các bộ phận chính của chip. Sau đó, vị trí sẽ quyết định chính xác vị trí của từng bộ phận. Sau đó, định tuyến kết nối các bộ phận với dây trong khi tránh các vấn đề như chậm trễ.

Kiểm tra bố cục là rất quan trọng trong bước này. Bạn cần phải chắc chắn rằng nó tuân thủ các quy tắc và đáp ứng kế hoạch. Công cụ kiểm tra các vấn đề như tín hiệu xấu hoặc các vấn đề về thời gian. Những kiểm tra này ngăn chặn những sai lầm đắt tiền trước khi làm chip.

Hôm nay,Học máy giúp nhiều công việc này. Nó cải thiện vị trí và định tuyến để làm cho chip tốt hơn và sử dụng ít năng lượng hơn. Điều này làm cho quá trình nhanh hơn và tạo ra bố cục chất lượng cao hơn.

Công cụ để bố trí tốt hơn

Công cụ đặc biệt giúp thiết kế bố cục dễ dàng và nhanh hơn. Công cụ hỗ trợ ai kiểm tra nhiều thiết kế để tìm bố cục tốt nhất. Chúng tiết kiệm thời gian, cải thiện hiệu suất và làm cho Chip sử dụng ít năng lượng hơn. Bằng việc sử dụng dữ liệu trong quá khứ, những công cụ này tạo ra bố cục tốt hơn nhanh hơn các phương pháp cũ.

Ví dụ, máy công cụ học tập xử lý các nhiệm vụ thiết kế tốt hơn con người. Sản phẩm làm chip chất lượng cao hơn và sẵn sàng nhanh hơn. Sử dụng các công cụ này làm cho quá trình thiết kế asic mượt mà và thành công hơn.

Thiết kế cho kỹ thuật kiểm tra

Giúp kiểm tra dễ dàng hơn

Giúp việc kiểm tra dễ dàng hơn đảm bảo cho bạnAsicHoạt động tốt sau khi sản xuất. Thiết kế với tâm trí thử nghiệm giúp tìm và khắc phục vấn đề sớm. Điều này làm cho chip của bạn đáng tin cậy hơn và tránh Những Sai Lầm tốn kém trong quá trình sản xuất.

Kiểm tra tốt hơn cũng cải thiện kết quả sau khi chip được xây dựng. Ví dụ:

-

Đầu dò đặc biệt giúp đo vật liệu còn sót lại như chất thông lượng.

-

Kiểm tra cải tiến mang lại kết quả kiểm tra điện chính xác hơn.

-

Mặc dù khó khăn,Đầu dò mũi đụcLà chìa khóa cho kết quả tốt nhất.

Tập trung vào kiểm tra đảm bảoAsicHoạt động tốt và đáp ứng mục tiêu của nó trong sử dụng thực tế.

Các cách thiết kế phổ biến để thử nghiệm

Thiết kế để thử nghiệm (Dft) Các Phương Pháp Giúp chip dễ kiểm tra và sửa chữa hơn. Các phương pháp này bao gồm:

-

Chuỗi quét: Liên kết đăng ký Nội Bộ Trong một chuỗi để tìm lỗi.

-

Tự kiểm tra tích hợp (bist): Cho phép chip tự kiểm tra, cần ít thiết bị hơn.

-

Quét ranh giới: Kiểm tra các kết nối giữa các chip để đảm bảo chúng giao tiếp.

Sử dụng các phương pháp này giúp việc kiểm tra đơn giản hơn và cải thiện chất lượng chip của bạn.

Dụng cụ cho thiết kế thử nghiệm

Nhiều công cụ hỗ trợDftKỹ thuật. Những sản phẩm phổ biến là synopsys dftmax, cadence modus, và mentor tessent. Những công cụ này tự động hóa các tác vụ như thêm chuỗi quét và tạo ra các mẫu thử nghiệm.

Ví dụ, synopsys dftmax tăng khả năng kiểm tra mà không làm tổn thương hiệu suất. Cadence modus cắt giảm thời gian thử nghiệm và tìm thấy nhiều lỗi hơn. Mentor tessent bổ sung các tính năng tiên tiến cho quét bist và boundary.

Sử dụng các công cụ này giúp kiểm tra nhanh hơn và đảm bảo cho bạnAsicĐáng tin cậy và hoạt động tốt.

Quy hoạch sàn

Bộ phận chip sắp xếp

Quy hoạch sàn nhà là một bước quan trọng trong việc tạo ra Asics. Điều đó có nghĩa là sắp xếp các bộ phận của chip hoạt động tốt và hoạt động tốt hơn. Trong bước này, Bạn quyết định từng phần của chip sẽ đi đâu. Bạn Nghĩ Về Những thứ như cách các bộ phận kết nối, dòng điện và cường độ tín hiệu. Một kế hoạch sàn tốt giúp chip chạy nhanh hơn, sử dụng ít năng lượng hơn và đáp ứng các mục tiêu của nó.

Một phần quan trọng của quy hoạch sàn là xử lý lưới. Lưới là các liên kết giữa các bộ phận chip. Ví dụ,60-70%Của lưới kết nối với chỉ một phần khác. Các lưới này thường liên kết các bộ phận gần đó và có hoa văn dễ nhận ra. Lưới Kết nối với nhiều bộ phận có sự trải đều hơn. Biết các mẫu này giúp bạn lập kế hoạch dây và tránh các vấn đề về năng lượng hoặc tốc độ.

|

Mô tả Thống Kê |

Giá Trị/Chi tiết |

|---|---|

|

Tỷ lệ phần trăm của lưới với FO = 1 |

60-70% |

|

Đặc điểm của FO = 1 |

Đuôi dài, đỉnh cho hàng xóm gần và định tuyến nhóm con |

|

Đặc điểm của FO > 1 |

Phân bố đối xứng và phẳng hơn |

|

Cách tiếp cận bàn TảI Dây |

80-90% phần trăm cho Dự Toán điện dung trường hợp tệ nhất |

|

Thay đổi chiều dài lưới |

Phụ thuộc vào kích thước khối (ví dụ: cổng 25 k so với cổng 5 K) |

|

Phụ thuộc vào hình khối |

Thống kê tính toán cho khối vuông |

|

Phụ thuộc vào loại netlist |

Thay đổi dựa trên các hạn chế tổng hợp (ví dụ, độ trễ tối thiểu so với diện tích tối thiểu) |

Yếu tố lập kế hoạch sàn quan trọng

Khi lập kế hoạch bố trí chip, bạn cần suy nghĩ về nhiều thứ. Sản phẩm bao gồm Kích thước và hình dạng của các bộ phận, kiểm soát nhiệt và lưu lượng điện. Ví dụ, lập kế hoạch cho nhiệt có thể giúp chip giữ mát và hoạt động tốt hơn. Ngoài ra, đặt các bộ phận vào đúng điểm có thể làm cho tín hiệu nhanh hơn và dây ngắn hơn.

Ai TOOLS bây giờ giúp lên kế hoạch sànBằng cách thực hiện nhiệm vụ tự động. Ai nhìn vào thiết kế một cách nhanh chóng và tìm thấy bố cục tốt nhất. Sản phẩm giúp tiết kiệm thời gian và làm Chip tốt hơn là làm bằng tay.

Dụng cụ lập kế hoạch sàn

Công cụ hiện đại giúp việc lên kế hoạch sàn dễ dàng và tốt hơn. Những công cụ này cho phép bạn thử bố trí khác nhau và khắc phục các vấn đề về thời gian hoặc sức mạnh. Công cụ hỗ trợ ai có thể tạo bố trí cân bằng tốc độ và sử dụng năng lượng. Họ cũng tìm thấy các khu vực nóng và đề nghị sửa chữa để giữ cho chip đáng tin cậy.

Sử dụng những công cụ này giúp việc lên kế hoạch sàn nhanh hơn và chính xác hơn. Bước này rất quan trọng để làm cho Asics hoạt động tốt trong cuộc sống thực.

Vị trí

Sắp xếp linh kiện để có hiệu suất tốt nhất

Đặt linh kiện lên chip là rất quan trọng. Nó ảnh hưởng đến việc chip hoạt động nhanh và hiệu quả như thế nào. Sắp xếp có nghĩa là sắp xếp các bộ phận để giảm sự chậm trễ và tiết kiệm điện. Vị trí tốt cũng giúp kết nối dây dễ dàng hơn sau này.

Để kiểm tra chất lượng vị trí đặt hàng, các nhà thiết kế sử dụng các biện pháp nhất định. Hai cái thông thường làChiều dài dây nửa chu vi (hpwl)VàLời bài hát có nghĩa là: slack âm tính tồi tệ nhất (WNS). Những sản phẩm này giúp hiển thị vị trí ảnh hưởng đến tốc độ và sử dụng năng lượng như thế nào. Bảng dưới đây giải thích các biện pháp sau:

|

Hệ mét |

Nó có nghĩa là gì |

Tại Sao Nó quan trọng? |

|---|---|---|

|

Hpwl |

Đường dây ngắn hơn |

Tiết kiệm năng lượng và tăng tốc lưu lượng dữ liệu |

|

WNS |

Vấn đề về thời gian |

Sửa chữa chúng cải thiện hiệu suất |

|

FREQ |

Tốc độ chip |

Tần số cao hơn có nghĩa là hoạt động nhanh hơn |

Bằng cách tập trung vào những điều này, các nhà thiết kế có thể đảm bảo con chip đáp ứng được mục tiêu của nó.

Cách đặt linh kiện

Có nhiều cách khác nhau để sắp xếp các bộ phận trên chip. Một phương pháp là "vị trí tế bào tiêu chuẩn", nơi các bộ phận nhỏ được xếp thành hàng. Sản phẩm tiết kiệm không gian và rút ngắn dây. Một Cách Khác là "vị trí Macro", đặt các phần lớn trước. Các bộ phận nhỏ hơn được thêm vào sau để cải thiện hiệu suất.

Các phương pháp tiên tiến như ủ mô phỏng và phân vùng cũng được sử dụng. Những Kỹ thuật này kiểm tra nhiều bố cục để tìm ra sản phẩm tốt nhất. Ví dụ, quá trình ủ mô phỏng di chuyển các bộ phận xung quanh để giảm chiều dài dây và tránh các khu vực đông đúc.

Dụng cụ để đặt dễ dàng hơn

Các công cụ đặc biệt giúp tự động hóa các nhiệm vụ sắp xếp và cải thiện kết quả. Các công cụ như cadence innovaus, synopsys IC compiler II và mentor Graphics Olympus-SOC rất phổ biến. Họ kiểm tra các vấn đề như dây điện đông đúc, vấn đề về thời gian và sử dụng điện.

Bảng dưới đây cho thấy những gì các công cụ đo lường:

|

Hệ mét |

Nó kiểm tra những gì |

|---|---|

|

Lời bài hát có nghĩa là: slack âm tính tồi tệ nhất (WNS) |

Tìm ra vấn đề về thời gian lớn nhất trong thiết kế. |

|

Total negative slack (TNS) |

Thêm tất cả các vấn đề về thời gian để xem hiệu suất tổng thể. |

|

Số đường vi phạm (nvp) |

Đếm đường dẫn không đúng quy tắc thời gian. |

|

Tắc nghẽn |

Kiểm tra xem dây có quá đông ở một số khu vực không. |

|

Chiều dài dây (WL) |

Đo tổng chiều dài của dây trên chip. |

|

Chiều dài dây nửa chu vi (hpwl) |

Ước tính Chiều dài dây bằng cách tổng hợp lên nửa chu vi của các hộp làm tròn. |

|

Hpwl Macro (mhpwl) |

Chỉ tập trung vào chiều dài dây cho các bộ phận lớn. |

Sử dụng các công cụ này giúp tạo ra các chip nhanh, hiệu quả và đáng tin cậy.

Tổng Hợp cây đồng hồ

Giữ các bộ phận chip đồng bộ

Cây đồng hồ là một phần quan trọng của một con chip. Nó đảm bảo tất cả các bộ phận của chip hoạt động cùng một lúc. Nếu thời gian tắt, chip có thể không hoạt động tốt. Cây đồng hồ gửi tín hiệu đồng hồ đến mọi bộ phận của con chip. Điều này giúp thời gian ổn định và giúp chip chạy trơn tru. Điều rất quan trọng là tạo ra một asic đáng tin cậy và hiệu quả.

Tổng Hợp cây đồng hồ hoạt động để cân bằng thời gian tín hiệu đồng hồ. Cân bằng này được gọi là đồng hồ lệch, và nó phải ở nhỏ để tránh các vấn đề. Thiết kế cây đồng hồ tốt giúp giảm sự chậm trễ và giúp chip hoạt động tốt hơn.

Các bước thiết kế cây đồng hồ

Làm cây đồng hồ có vài bước để cải thiện thời gian và sức mạnh. Trước tiên, Hãy quyết định tín hiệu đồng hồ đến từ đâu và cách chúng sẽ lan ra. Sau đó, đảm bảo tín hiệu đồng hồ đạt đến tất cả các bộ phận cùng một lúc. Một cách để tiết kiệm điện là tắt các bộ phận không sử dụng của cây đồng hồ. Đồng hồ bấm giờ có thể tiết kiệm tới 20% năng lượng nhưng có thể làm cho chip lớn hơn một chút.

Một phương pháp khác là vị trí nhận biết cây đồng hồ. Điều này làm giảm năng lượng chuyển đổi mạng bằng25.3% và Tổng công suất 11.4%. Nó thực hiện điều này với ít ảnh hưởng đến thời gian (2.0%) và kích thước chip (1.2%). Thiết kế đa chế độ đa góc (mcmm) cũng giúp cải thiện thời gian, năng lượng và quy tắc sản xuất trong các tình huống khác nhau.

Dụng cụ làm cây đồng hồ

Công cụ đặc biệt giúp việc tổng hợp cây đồng hồ dễ dàng hơn. Những sản phẩm phổ biến là synopsys primetime, cadence innovaus và mentor Graphics Olympus-SoC. Những công cụ này giúp thiết kế và kiểm tra cây đồng hồ để đáp ứng nhu cầu về thời gian và năng lượng. Chúng cũng bao gồm các tính năng để điều chỉnh đồng hồ và mcmm, giúp quá trình nhanh hơn.

Sử dụng các công cụ này giúp thiết kế asic của bạn hoạt động tốt hơn và bền hơn. Họ giải quyết các vấn đề về thời gian và cắt điện năng sử dụng, tạo ra một con chip có thời gian và hiệu quả.

Định tuyến

Linh kiện kết nối

Định tuyến liên kết các bộ phận của một con chip với dây. Nó đảm bảo tín hiệu di chuyển nhanh chóng và chính xác giữa các phần chip. Bước này rất quan trọng vì định tuyến xấu có thể làm chậm chip, lãng phí năng lượng và làm tổn thương hiệu suất. Lập kế hoạch đường dây cẩn thận tránh các khu vực đông đúc và giữ cho chip hoạt động tốt.

Định tuyến tạo ra các đường dẫn cho tín hiệu trong khi làm theo quy tắc thiết kế. Các Quy Tắc này bao gồm việc tách dây ra, tránh chồng chéo và giảm các vấn đề về tín hiệu. Định tuyến tốt làm cho con chip đáng tin cậy hơn và tốt hơn cho công việc của nó.

Chiến Lược Định tuyến

Chiến Lược Định tuyến tốt giúp chip hoạt động nhanh hơn và tốt hơn. Các phương pháp khác nhau giải quyết các vấn đề như dây điện đông đúc và trì hoãn thời gian. Ví dụ, liên kết lai kết nối nhiều lớp chip, cần ít đường dẫn dây rộng hơn. IC 3D sửa dây 2D nhưng Thêm thách thức với kết nối dọc. Ai TOOLS đặt các khối kết nối thông minh gần các cạnh để cân bằng các lớp dây.

|

Chiến Lược Định tuyến |

Nó giúp Như Thế Nào |

|---|---|

|

Liên kết lai |

Liên kết nhiều lớp, cần ít đường dây rộng hơn. |

|

IC 3D |

Sửa chữa dây 2D nhưng thêm các thử thách kết nối dọc. |

|

Đặt các khối kết nối gần các cạnh để cân bằng các lớp dây. |

Các phương pháp tiên tiến như tăng cường học tập (RL) giúp định tuyến nhanh hơn. RL cải thiện tốc độ kết nối dây bằng 45% so với các phương pháp cũ và nhanh hơn 32% so với các phương pháp tập trung vào thời gian. Nhìn chung, các quy trình phụ trợ nhanh hơn 22% với các phương pháp định tuyến và nhanh hơn 15% với các phương pháp định thời.

-

Cải tiến từ định tuyến nâng cao:

-

Kết nối dây nhanh hơn 45%Hơn là phương pháp thường xuyên.

-

Nhanh hơn 32% so với các phương pháp tập trung vào thời gian.

-

Quá trình phụ trợ tăng tốc: 22% (khả năng định tuyến) và 15% (thời gian).

-

Dụng cụ định tuyến

Công cụ định tuyến giúp kết nối các bộ phận chip dễ dàng và chính xác hơn. Các công cụ phổ biến bao gồm cadence innovaus, synopsys IC compiler II và mentor Graphics Olympus-SoC. Những công cụ này lên kế hoạch đường dẫn dây, giảm đông đúc và cải thiện thời gian. Họ cũng tuân thủ các quy tắc thiết kế để đáp ứng nhu cầu của chip.

Các công cụ hiện đại thường sử dụng ai để cải thiện định tuyến. Ai kiểm tra thiết kế và tìm đường dây tốt nhất, tiết kiệm điện và thời gian. Sử dụng các công cụ này giúp định tuyến nhanh hơn và mang lại kết quả tốt hơn.

Kiểm tra xác minh vật lý

Thiết kế chip kiểm tra

Xác minh vật lý đảm bảo chip của bạn tuân thủ các quy tắc thiết kế và hoạt động. Bước này kiểm tra xem bố cục chip có phù hợp với kế hoạch ban đầu không. Nó cũng đảm bảo chip sẽ hoạt động chính xác khi xây dựng. Khắc phục sự cố sớm giúp tiết kiệm tiền và cải thiện hiệu suất chip.

Cần có hai kiểm tra chính ở đây. Trước tiên, xác nhận thiết kế theo quy định của nhà máy. Thứ hai, đảm bảo bố cục phù hợp với thiết kế logic. Những kiểm tra này tìm thấy các vấn đề như dây quá gần, sai khoảng cách hoặc thiếu liên kết. Giải quyết những vấn đề này sớm làm cho quá trình làm chip mượt mà hơn.

Cách xác minh thiết kế

Có nhiều cách khác nhau để kiểm tra thiết kế chip của bạn. Kiểm tra quy tắc thiết kế (drc) đảm bảo bố trí theo quy định của nhà máy. Bố cục so với sơ đồ (LVS) so sánh bố cục với kế hoạch thiết kế để đảm bảo chúng phù hợp. Chiết xuất ký sinh (pex) tìm thấy các hiệu ứng điện không mong muốn gây ra bởi bố cục.

Ví dụ, DRC có thể phát hiện các dây quá gần với nhau, điều này có thể gây ra vấn đề. LVS kiểm tra rằng mọi kết nối trong bố cục đều tồn tại trong kế hoạch. Pex Dự Đoán hiệu ứng không mong muốn có thể thay đổi hiệu suất của chip như thế nào. Sử dụng tất cả các phương pháp này cho phép kiểm tra đầy đủ thiết kế chip của bạn.

Công cụ để xác minh chip

Công cụ đặc biệt giúp kiểm tra thiết kế nhanh hơn và dễ dàng hơn. Những sản phẩm phổ biến bao gồm cadence Pegasus, synopsys IC validator, và mentor Calibre. Những công cụ này tự động hóa các tác vụ như DRC, LVS, và pex, tiết kiệm thời gian và giảm sai lầm. Họ cũng đưa ra báo cáo chi tiết để khắc phục sự cố một cách nhanh chóng.

Ví dụ, mentor Calibre rất phù hợp để kiểm tra DRC và LVS chính xác. Synopsys IC validator xử lý các thiết kế phức tạp tốt. Cadence Pegasus hoạt động nhanh với chip lớn. Sử dụng các công cụ này đảm bảo chip của bạn đáp ứng tất cả các quy tắc và hoạt động đáng tin cậy.

Chuẩn bị tập tin gdsii

Chuẩn bị thiết kế sẵn sàng cho sản xuất

Bước cuối cùng trong việc tạo ra asic là chuẩn bị sẵn sàng cho sản xuất. Ở đây, bạn kiểm tra xem thiết kế chip có đáp ứng được tất cả các quy định của nhà máy không. Bạn cũng đảm bảo chip sẽ hoạt động tốt sau khi được chế tạo. Điều quan trọng là phải khắc phục bất kỳ sai lầm nào có thể làm tổn thương cách chip hoạt động hoặc kéo dài.

Bước này rất quan trọng vì nó biến thiết kế kỹ thuật số thành một con chip thực sự. Thiết kế được chuẩn bị kỹ càng giúp tránh các vấn đề đắt tiền trong quá trình sản xuất. Nó cũng giữ cho quá trình trơn tru và hiệu quả.

Các bước để tạo tệp gdsii

Để chuẩn bị sẵn sàng cho thiết kế, bạn cần tạo tệp gdsii. Tập tin này giống như một bản đồ của chip. Nó cho thấy tất cả các bộ phận đi đâu, Cách dây kết nối và chi tiết về các lớp.

Đầu tiên, bạn xuất bố cục từ các công cụ thiết kế sang định dạng gdsii. Sau đó, bạn kiểm tra tập tin để đảm bảo nó phù hợp với thiết kế một cách hoàn hảo. Cuối cùng, bạn gửi tập tin đến nhà máy để xây dựng chip. Mỗi bước cần phải được thực hiện cẩn thận để tránh những sai lầm có thể gây ra vấn đề.

Công cụ hỗ trợ tập tin gdsii

Có những công cụ giúp việc tạo và kiểm tra các tệp gdsii dễ dàng hơn. Một số sản phẩm phổ biến là cadence Virtuoso, synopsys IC compiler II, và mentor Graphics Calibre. Những công cụ này tự động hóa các tác vụ như kéo dữ liệu bố trí, tạo tệp và tìm lỗi. Họ cũng đảm bảo thiết kế tuân thủ các quy tắc của nhà máy, giảm nguy cơ các vấn đề sản xuất.

Sử dụng các công cụ này làm cho quá trình thiết kế asic nhanh hơn và đáng tin cậy hơn. Chúng giúp đảm bảo chip của bạn hoạt động như kế hoạch.

Quy trình thiết kế asic là chìa khóa để tạo ra các chip chuyên dụng. Nó giúp tạo ra các Chip sử dụng ít năng lượng hơn và hoạt động tốt. Một kế hoạch rõ ràng giúp quá trình dễ dàng hơn và giảm chi phí. Điều này làm cho nó tuyệt vời để làmChip 1,000 đến 100,000. Sử dụng các phương pháp được thử nghiệm từ các nhà cung cấp làm giảm Rủi Ro và tăng tốc sản xuất.

Làm việc nhóm và các công cụ thiết kế thông minh là rất quan trọng cho thành công. Những công cụ này giúp công việc đơn giản và chính xác hơn. Họ cũng đảm bảo chip hoạt động như kế hoạch. Bằng cách làm theo các bước rõ ràng, bạn có thể xây dựng các chip tiết kiệm không gian và đáp ứng nhu cầu công nghệ ngày nay.

Câu hỏi thường gặp

Asic là gì, và tại sao nó quan trọng?

Asic là một con chip đặc biệt được sản xuất cho một công việc. Nó hoạt động tốt hơn và sử dụng ít năng lượng hơn so với chip thông thường. Các ngành công nghiệp như xe hơi và điện thoại sử dụng Asics cho các giải pháp tùy chỉnh phù hợp với nhu cầu của họ.

Thiết kế asic Như Thế Nào?

Thiết kế asic có nhiều bước như lập kế hoạch, kiểm tra và thử nghiệm. Mỗi bước đảm bảo chip hoạt động tốt và có thể được xây dựng. Quá trình này giúp tạo ra các chip đáng tin cậy và hiệu suất cao.

Công cụ nào giúp tạo ra Asics?

Các công cụ như trình biên dịch thiết kế synopsys và cadence innovaus được sử dụng. Chúng giúp xây dựng, sắp xếp và kiểm tra chip để đáp ứng mục tiêu của nó.

Tại sao kiểm tra chức năng của chip lại quan trọng?

Kiểm tra đảm bảo chip hoạt động như kế hoạch. Nó tìm thấy những sai lầm sớm, tiết kiệm thời gian và tiền bạc. Bước này là chìa khóa để tạo ra một con chip tốt và đáng tin cậy.

Bố cục ảnh hưởng đến chip như thế nào?

Bố trí cho thấy các bộ phận đi đâu và cách chúng kết nối. Bố trí tốt giúp chip nhanh hơn, tiết kiệm năng lượng và cải thiện cách thức hoạt động tổng thể.