Điều Gì xác định tốc độ SPI là một hướng dẫn hoàn chỉnh

Giao diện ngoại vi nối tiếp (SPI) nổi tiếng với truyền dữ liệu tốc độ cao. Giao thức truyền thông đồng bộ này cho phép

The Giao diện ngoại vi nối tiếp(SPI) Nổi tiếng vớiTruyền dữ liệu tốc độ cao. Cái nàyGiao thức truyền thông đồng bộCho phép dữ liệu hiệu quảChuyển khoảnGiữaThiết bị, Với một sốTốc độ truyền dữ liệu Vượt quá 100 MHz. Vậy tại sao dự án của bạn khôngHiệu suấtLuôn Thắng những chiếc áo nàyTốc độ truyền dữ liệu? Sự thật của bạnTốc độ SPIVà nhìn chungThông lượngBị giới hạn bởi ba khu vực chính.

💡Cuối cùngHiệu suấtCủa bất kỳSPIDữ liệuChuyển khoảnLà sự cân bằng của bạnThiết bị'Giới hạn phần cứng, chất lượng kết nối vật lý và Cấu hình phần mềm của bạn.

Mang theo chìa khóa

- Tốc độ SPI của bạn phụ thuộc vào ba điều chính: Giới hạn phần cứng của thiết bị, chất lượng kết nối vật lý và cách bạn thiết lập phần mềm.

- Luôn kiểm tra các giới hạn tốc độ trong các chi tiết cho cả thiết bị chủ và nô lệ của bạn. Thiết bị chậm nhất đặt tốc độ tối đa cho xe buýt SPI của bạn.

- Thiết kế PCB tốt rất quan trọng. Giữ dây ngắn, phù hợp với độ dài theo dõi và sử dụng mặt phẳng mặt đất mạnh để tránh sự cố tín hiệu ở tốc độ cao.

- Sử dụng trực tiếpBộ nhớTruy cập (DMA) trong phần mềm của bạn để có hiệu suất tốt nhất. DMA cho phép bạnVi điều khiểnGửi dữ liệu nhanh chóng mà không làm chậm Bộ xử lý chính.

Vai trò của phần cứng trong Tốc độ SPI

Bước đầu tiên để hiểu được tốc độ SPI tối đa của hệ thống là tự nhìn vào phần cứng. Trước khi bạn THẬM CHÍ Viết Một dòng mã hoặc thiết kế một PCB, các chi tiết cho các thiết bị chủ và Nô lệ của bạn đặt một giới hạn trên cứng. Hiệu suất cuối cùng của bạn gắn liền với khả năng của những sản phẩm nàyMạch tích hợp.

Giới hạn đồng hồ chính

Thiết bị chính của bạn, thường là vi điều khiển, tạo ra đồng hồ SPI (sck). Dạ máy có tần số tối đa để vận hành ạGiao diện ngoại vi nối tiếp. Bạn có thể tìm thấy giới hạn này trongPhần đặc tính điện của bảng điều khiển của nó. Các bảng thường chỉ định mức tối đaFsck(Tần số xung nhịp SPI) dưới các Điện áp hoạt động khác nhau.

Ví dụ, bảng dữ liệu của vi điều khiển có thể trình bày các đặc điểm SPI của nó như sau:

| Biểu tượng | Thông số | Điều kiện | Min | Typ | Tối đa | Đơn vị |

|---|---|---|---|---|---|---|

| Fsck | Tần số xung nhịp SPI | Chế độ Bộ thu Bộ điều khiển 2.7 V <VDD< 3.6 V | - | - | 45 | MHz |

| Chế độ máy Phát điều khiển 2.7 V <VDD< 3.6 V | - | - | 45 | MHz |

Lưu ý:Các giá trị trong bảng trên dựa trên

Fpclkx/3, Ở đâuFpclkxLà đồng hồ ngoại vi. Giá trị tối đa thực tế phụ thuộc vào kiến trúc cụ thể của vi điều khiển.

Đồng hồ hệ thống riêng của Master cũng đóng vai trò quan trọng. Thiết bị ngoại vi SPI thường chạy trên đồng hồ có nguồn gốc từ đồng hồ hệ thống chính.

- Kiến trúc đồng hồ bên trong của vi điều khiển có thể hạn chế đồng hồ đầu vào của mô-đun SPI. Ví dụ, một mô-đun chỉ có thể chấp nhận đầu vào tối đa của48 Mhz.

- Đồng hồ đầu vào này sau đó được chia xuống để tạo ra tín hiệu sck cuối cùng cho truyền SPI.

- Điều này có nghĩa là ngay cả khi thiết bị ngoại vi SPI về mặt lý thuyết có thể chạy nhanh hơn, hiệu suất của nó bị giới hạn bởi đồng hồ bạn cho nó ăn.

Dây buộc Đồng hồ nô lệ

Bây Giờ, hãy xem thiết bị nô lệ. Mỗi nô lệ SPI, cho dù đó là mộtCảm biến, Chip nhớ, hoặc một vi điều khiển khác, cũng có tần số xung nhịp tối đa mà nó có thể xử lý. Đây thường là nút cổ chai quan trọng nhất trong cấu hình Master/Slave.Vượt quá giới hạn này sẽ khiến nô lệ hiểu sai dữ liệu, dẫn đến sự Tham Nhũng dữ liệu trong quá trình chuyển.

💡BUS SPI của bạn chỉ nhanh như thiết bị chậm nhất. Tốc độ truyền thông cuối cùng phải được đặt ở mức thấp hơn của hai tối đa (chủ hoặc Nô Lệ).

Bạn phải kiểm tra cẩn thận bảng dữ liệu của nô lệ. Bạn có thể tìm thấy tốc độ truyền dữ liệu tối đa khác nhau tùy thuộc vào hoạt động. Ví dụ, mộtVi điều khiển STM32 ở chế độ Nô Lệ Có thể hỗ trợ 40 MHz để nhận dữ liệu nhưng tốc độ thấp hơn như 24 MHz cho giao tiếp song công hoàn toàn. Những khác biệt này có thể phát sinh từ logic bên trong cần thiết để lấy mẫu và gửi dữ liệu đồng thời. Đối với hầu hết các thiết bị nô lệ SPI, một quy tắc ngón tay cái an toàn là để giữ tốc độ đồng hồ SPI bên dướiMột phần mười tần số xung nhịp của hệ thống Nô LệĐể đảm bảo truyền dữ liệu đáng tin cậy.

Chậm xử lý Nô Lệ

Tần số đồng hồ cao không phải lúc nào cũng bằng thông lượng cao. THƯỚC ĐO THỰC sự về hiệu suất là số lượng dữ liệu bạn có thể chuyển theo thời gian. Nhiều thiết bị Nô Lệ Cần tạm dừng giữa các giao dịch để xử lý thông tin. Cái này được gọi làThời gian xử lý Nô LệHoặcTrì hoãn liên giao dịch.

Hãy tưởng tượng bạn gửi một lệnh đến một cảm biến. Cảm biến cần thời gian để thực hiện một phép đo trước khi nó có dữ liệu sẵn sàng cho lần chuyển tiếp. Đồng hồ SPI nhanh vô dụng nếu chủ nhân phải chờ lâu để nô lệ sẵn sàng. Độ trễ này ảnh hưởng đáng kể đến thông lượng dữ liệu tổng thể của bạn.

Một số tình huống phổ biến đòi hỏi sự chậm trễ này bao gồm:

| Kịch bản | Tại Sao Cần Phải trì hoãn |

|---|---|

| Slave có logic bên trong chậm | Thiết bị cần thời gian để xử lý byte dữ liệu trước đó. |

| Giao thức SPI nhiều khung | Bản thân giao thức đòi hỏi một khoảng cách thời gian cụ thể giữa các khung hình. |

| Viết trang Flash SPI | Chip nhớ phải tạm dừng để chốt địa chỉ trước khi ghi dữ liệu. |

| Tránh lỗi thời gian | Độ trễ nhỏ có thể giúp ngăn ngừa lỗi ở tốc độ xung nhịp SPI rất cao. |

Vậy, Làm thế nào để bạn biết khi nào nô lệ đã sẵn sàng cho lần chuyển tiếp? Thiết bị sử dụng nhiều phương pháp để báo hiệu trạng thái của chúng:

- Chốt cài:Một số thiết bị có một pin đầu ra chuyên dụng mà họ khẳng định để báo hiệu họ đang bận xử lý.

- Đăng ký Trạng thái:Bạn có thể thăm dò tình trạng đăng ký trên nô lệ. Đăng ký này thường chứa các bit như

Trdy(Sẵn sàng phát) hoặcRrdy(Nhận sẵn sàng) để chỉ trạng thái của nó. - NGẮT:Nô Lệ Có thể sử dụng các bit trạng thái này để kích hoạt một sự gián đoạn trên chủ, chủ động báo hiệu rằng nó đã sẵn sàng cho giao dịch SPI tiếp theo.

Lớp vật Lý Giao diện ngoại vi nối tiếp

Một khi bạn hiểu giới hạn của bạnMạch tích hợp, Bạn phải nhìn vào các kết nối Vật Lý Giữa chúng. Các dấu vết và dây điện của bảng mạch in (PCB) tạo thành bus SPI của bạn không phải là dây dẫn hoàn hảo. Ở tần số cao, những đường dẫn vật lý này giới thiệu Bộ Thử Thách của riêng họ có thể làm suy giảm chất lượng tín hiệu và hạn chế hiệu suất tổng thể của bạn.

Đường dẫn và bố trí tín hiệu

Dây dài và dấu vết PCB có thể hoạt động như ăng ten nhỏ. Hành vi này giới thiệu sự chậm trễ lan truyền, đó là thời gian cần thiết để một tín hiệu di chuyển từ chủ đến các thiết bị nô lệ. Ở tốc độ thấp, độ trễ này không đáng kể. Với tốc độ truyền dữ liệu cao, nó trở thành một vấn đề lớn.

Không khớp với độ dài theo dõi giữa các dòng đồng hồ (sck) và dữ liệu (mosi/Miso) gây ra lỗi thời gian. Tín hiệu đồng hồ có thể đến máy thu vào một thời điểm khác với dữ liệu. Điều này có thể khiến thiết bị nô lệ chốt sai bit dữ liệu, làm hỏng toàn bộ quá trình chuyển. Khi Tần số tín hiệu của bạn tăng lên, thời gian đồng hồ trở nên ngắn hơn, làm cho thiết kế của bạn nhạy hơn nhiều so với sự khác biệt nhỏ về độ trễ lan truyền.

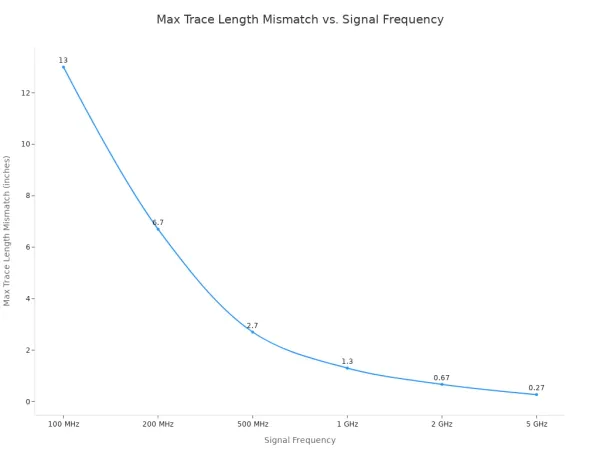

Bảng dưới đây cho thấy độ bền của độ dài dấu vết co lại nhanh như thế nào khi tần số xung nhịp SPI tăng lên.

| Tần số tín hiệu | Khoảng thời gian đồng hồ (T) | Dung sai xiên tối đa (20% t) | Độ trễ lan truyền (fr4) | Độ dài dấu vết tối đa không khớp |

|---|---|---|---|---|

| 100 MHz | 10 NS | 2 NS | ~ 150 PS/in | ~ 13 in |

| 200 MHz | 5 NS | 1 NS | ~ 150 PS/in | ~ 6.7 in |

| 500 MHz | 2 NS | 0.4 NS | ~ 150 PS/in | ~ 2.7 in |

| 1 GHz | 1 NS | 0.2 NS | ~ 150 PS/in | ~ 1.3 in |

| 2 GHz | 0.5 NS | 0.1 NS | ~ 150 PS/in | ~ 0.67 in |

| 5 GHz | 0.2 NS | 0.04 NS | ~ 150 PS/in | ~ 0.27 in |

Mẹo chuyên nghiệp:Khi bus SPI của bạn hoạt động trong phạm vi 50-100 MHz, bạn nên xem các dấu vết như đường truyền. Để tránh phản xạ tín hiệu và đổ chuông, bạn có thể kết thúc loạt nhỏĐiện trở(Ví dụ, 22-33Ω) gần các chốt điều khiển. Đặt chúng trên các đường sck, mosi, và CS ở bậc thầy và trên đường Miso ở mỗi nô lệ.

Điện dung xe buýt và tính toàn vẹn

Mọi yếu tố trên PCB của bạn, từChân ICVới các dấu vết, thêm một lượng nhỏ điện dung không mong muốn. Cái này được gọi làĐiện dung ký sinh. Nó tồn tại giữa dấu vết tín hiệu và mặt phẳng tham chiếu gần nhất, thường là mặt phẳng mặt đất. Trong khi bạn không thể loại bỏ nó, bạn phải quản lý nó.

Điện dung này tác động trực tiếp đến thời gian tăng tín hiệu của bạn. Thời gian tăng là tín hiệu có thể chuyển từ điện áp thấp sang điện áp cao nhanh như thế nào.Điện dung xe buýt cao hoạt động như một rào cản, chống lại khả năng tăng tín hiệu. Điều này làm chậm thời gian tăng và làm tròn các cạnh sắc nét của tín hiệu đồng hồ của bạn. Nếu cạnh đồng hồ trở nên quá chậm, thiết bị nô lệ có thể không đăng ký chính xác, hạn chế tốc độ đồng hồ tối đa của bạn. Thật thú vị,Điện dung có tác dụng nhỏ hơn nhiều đối với thời gian rơi tín hiệu.

Thêm nhiều thiết bị phụ trợ vào bus SPI làm tăng tổng điện dung tải, có thể làm suy giảm tính toàn vẹn tín hiệu. Bạn có thể kiểm soát hiệu ứng ký sinh này thông qua thiết kế PCB cẩn thận.

- Sử dụng lớp mỏng bề mặt mỏng hơnĐể giảm khoảng cách tới mặt phẳng mặt đất liền kề.

- Chọn vật liệu Low-DK (Hằng số điện môi)Để PCB của bạn giảm tổng điện dung.

- Chọn các thành phần có kích thước chì nhỏ hơnĐể giảm thiểu đóng góp của họ.

Nhiễu xuyên âm và nhiễu

Nhiễu xuyên âm xảy ra khi năng lượng điện từ từ một dấu vết tín hiệu "rò rỉ" vào một dấu vết lân cận. Trên PCB, điều này thường Xảy Ra Giữa Hai Dấu vết SPI chạy cạnh nhau. Năng lượng kết hợp này tạo ra tiếng ồn trên dấu vết "nạn nhân". Nếu nhiễu đủ lớn, nó có thể gây ra sự chuyển đổi tín hiệu sai và làm hỏng việc truyền dữ liệu của bạn.

Hiện tượng này chủ yếu là do khớp nối điện dung. Cách tốt nhất để chống nhiễu xuyên âm và tiếng ồn bên ngoài khác là có mặt phẳng mặt đất được thiết kế tốt.

Một mặt phẳng vững chắc cung cấp đường quay trở lại trở kháng thấp cho các dòng tín hiệu. Điều này thắt chặt các trường điện từ xung quanh dấu vết tín hiệu, chứa chúng và ngăn chúng can thiệp vào các tín hiệu khác.Mặt phẳng tham chiếu gần hơn dẫn đến khớp nối chặt hơn và ít tiếng ồn hơn.

Để cải thiện thiết kế của bạn và đạt được tốc độ truyền dữ liệu cao hơn, bạn nên:

- Tối đa hóa mặt phẳng của bạn:Sử dụng càng nhiều không gian trống trên PCB càng tốt cho mặt phẳng mặt đất.

- Sử dụng lớp phủ chuyên dụng:Trong các tấm ván nhiều lớp, mặt phẳng chuyên dụng giúp tách biệt tuyệt vời và giảm tiếng ồn.

- Thêm khâu vias:Nếu bạn phải chia một mặt phẳng mặt đất, sử dụng vias để "khâu" các khu vực riêng biệt với nhau, tạo ra một đường dẫn liên tục, trở kháng thấp.

Bằng cách quản lý cẩn thận bố trí PCB, điện dung và nối đất, bạn có thể duy trì tính toàn vẹn tín hiệu. Điều này cho phép bạn chạy bus SPI ở tốc độ SPI cao hơn và đạt được thông lượng tổng thể tốt hơn.

Tác động của phần mềm lên hiệu suất SPI

Phần cứng và thiết bị của bạnBố trí PCBThiết lập tiềm năng cho giao tiếp tốc độ cao, nhưng phần mềm của bạn xác định xem bạn có thể thực sự đạt được nó hay không. Các lựa chọn bạn thực hiện trong mã, từ cài đặt giao thức cơ bản đến Phương pháp xử lý dữ liệu, trực tiếp kiểm soát hiệu suất và thông lượng SPI cuối cùng của bạn.

Chế độ SPI và thời gian

The Giao thức SPILà đồng bộ, có nghĩa là các thiết bị chủ và nô lệ phải đồng ý về thời gian. Bạn Định cấu hình thời gian này bằng cách chọn chế độ SPI chính xác. Một sự không phù hợp ở đây sẽ khiến việc chuyển giao Thất Bại hoàn toàn. Chế độ được xác định bởi hai thông số trong bảng dữ liệu của thiết bị nô lệ:

- Cực đồng hồ (cpol):Điều này đặt trạng thái nhàn rỗi của tín hiệu đồng hồ (thấp hoặc cao).

- Pha đồng hồ (cpha):Điều này xác định xem dữ liệu được lấy mẫu trên cạnh đồng hồ đầu tiên (hàng đầu) hoặc Thứ Hai (sau).

Hai thiết lập này kết hợp để tạo ra bốn chế độ SPI có thể. Nếu chủ của bạn được đặt thành chế độ 0 (cpol = 0, cpha = 0), nó dự kiến sẽ lấy mẫu dữ liệu trên cạnh Đồng hồ tăng. Thiết bị nô lệ của bạn cũng phải được cấu hình cho chế độ này để đảm bảo truyền dữ liệu thành công. Nhận sai lầm này là một nguồn thông thường của các lỗi ngăn chặn giao tiếp giữa các thiết bị.

Lái xe và hệ điều hành trên cao

Vi điều khiển của bạn di chuyển dữ liệu có tác động rất lớn đến hiệu suất. Bạn thường có hai lựa chọn để xử lý chuyển SPI: ngắt hoặc truy cập bộ nhớ trực tiếp (DMA). Việc sử dụng ngắt đơn giản hơn cho việc truyền tải cơ bản, nhưng nó tạo ra chi phí CPU đáng kể giới hạn tốc độ truyền dữ liệu tối đa của bạn. Đối với hiệu suất cao, DMA là phương pháp vượt trội.

💡DMA cho phép thiết bị ngoại vi SPI truyền dữ liệu trực tiếp đến hoặc từ bộ nhớ mà không liên quan đến CPU. Điều này giải phóng CPU để thực hiện các tác vụ khác, tăng đáng kể hiệu quả hệ thống của bạn và cho phép tốc độ dữ liệu cao hơn.

Bảng dưới đây so sánh hai cách tiếp cận:

| Tính năng | SPI điều khiển gián đoạn | DMA Driven SPI |

|---|---|---|

| Đầu CPU | Cao; CPU quản lý mỗi byte chuyển. | Thấp; CPU miễn phí sau khi bắt đầu chuyển. |

| Thông lượng | Thấp hơn; bị giới hạn bởi khả năng ngắt dịch vụ của CPU. | Cao hơn; có thể đạt tốc độ SPI tối đa. |

| Ốp sử dụng | Tốt cho tỷ lệ thấpCảm biếnHoặc lệnh đơn giản. | Lý tưởng để phát trực tuyến tốc độ cao và khối dữ liệu lớn. |

Khi bạn cần đạt được tốc độ truyền dữ liệu cao nhất từ các thành phần như ADC Độ phân giải cao hoặc Bộ nhớ flash, bạn nên sử dụng DMA. Cách tiếp cận này giảm thiểu sự chậm trễ của phần mềm và cho phép bus SPI của bạn hoạt động gần hơn với giới hạn phần cứng của nó.

Tốc độ SPI cuối cùng của bạn phụ thuộc vào ba yếu tố chính. Đây là giới hạn phần cứng, kết nối vật lý và hiệu quả phần mềm của bạn. Bạn phải cân nhắc cả ba lĩnh vực để đạt được tốc độ truyền dữ liệu cao SPI được biết đến. Một hệ thống nhanh yêu cầu một cách tiếp cận hoàn chỉnh.

💡Takeaway có thể hành động:Để tìm tốc độ tối đa thực sự của bạn, trước tiên hãy kiểm tra bảng dữ liệu của thiết bị nô lệ để biết giới hạn tốc độ của nó. Tiếp theo, kiểm tra tốc độ này với bố cục và phần mềm PCB của bạn. Điều chỉnh hướng xuống từ đó để tìm tỷ lệ ổn định nhanh nhất cho dự án cụ thể của bạn.