ASIC-Design prozess: Eine schrittweise Anleitung zum Erstellen anwendungs spezifischer integrierter Schaltkreise

Der ASIC-Design prozess hilft bei der Herstellung von Chips für spezielle Zwecke. Im Gegensatz zu regulären Prozessoren bieten ASICs eine hohe Leistung für bestimmte Aufgaben.

DieASIC-Design prozessHilft, Chips für besondere Zwecke herzustellen. Im Gegensatz zu regulären Prozessoren bieten ASICs eine hohe Leistung für bestimmte Aufgaben. Diese benutzer definierten Chips funktionieren besser, kosten weniger und machen mehr. DieASICEntwurfs schritte erfordern sorgfältige Planung und Arbeit. Sie sind wichtig für Branchen wie Autos, Telefone und Gadgets. Zum Beispiel verwenden Elektroautos ASICs, um Strom zu verwalten und mit Teilen zu sprechen. Die klaren Schritte im ASIC-Design helfen dabei, zuverlässige und energie sparende Chips für die heutigen Bedürfnisse zu erstellen.

Wichtige Imbiss buden

-

Klare Ziele sind sehr wichtig. Sie leiten das ASIC-Design und verhindern große Fehler.

-

Die Überprüfung der Funktion des Chips stellt sicher, dass es richtig funktioniert. Dieser Schritt findet Probleme früh und spart Zeit und Geld.

-

Die Verwendung von intelligenten Werkzeugen für Codierung und Layout hilft sehr. Diese Werkzeuge machen starke und schnelle Chips.

-

Test freundliche Designs erleichtern das Testen. Sie helfen, Probleme frühzeitig zu finden und zu beheben, damit der Chip später gut funktioniert.

-

Für die Herstellung von Chips wird eine gute GDSII-Datei benötigt. Es stellt sicher, dass das Design den Fabrik regeln folgt und ordnungs gemäß funktioniert.

Spezifikation und RTL-Code-Generation

Einstellungs spezifikationen

Der erste Schritt bei der Erstellung eines ASIC besteht darin, Spezifikationen festzulegen. Dies bedeutet, zu entscheiden, was der Chip tun soll, wie schnell er funktionieren soll und welche Grenzen er hat. Dieser Schritt hält den Design prozess organisiert und auf Kurs. AKlare Spezifikation funktioniert wie ein PlanUnd das ganze Projekt leiten. Es hilft, Fehler zu vermeiden, die die Arbeit verzögern oder die Kosten erhöhen könnten. Dieser Schritt dauert normaler weise 2 bis 6 Wochen, da er sorgfältige Aufmerksamkeit erfordert.

Die Spezifikationen helfen Ihnen auch dabei, die Hauptmerkmale des Chips heraus zu finden. Wenn Sie beispiels weise einen Chip für ein Smartphone herstellen, können Sie sich darauf konzentrieren, Strom zu sparen und schneller zu arbeiten. Klare Spezifikationen stellen sicher, dass der Chip das tut, was er tun soll.

RTL-Code schreiben

Nachdem Sie die Spezifikationen festgelegt haben, können Sie mit dem Schreiben von RTL-Code (Register Transfer Level) beginnen. Dieser Code zeigt, wie der Chip funktioniert und gebaut wird. Es werden spezielle Sprachen wie Verilog oder VHDL verwendet. RTL-Code macht die Spezifikationen zu einem funktionieren den Modell des Chips.

In diesem Stadium müssen Sie überprüfen, ob der RTL-Code den Spezifikationen entspricht. Das Überprüfen hilft oft, Fehler frühzeitig zu finden und spart später Zeit. Die Verwendung von Kontroll punkten während des Debuggens kann beispiels weise dazu beitragen, fehlende Teile oder Fehler schneller zu finden, wodurch der Prozess reibungsloser wird.

Werkzeuge für Spezifikationen und RTL-Code

Es gibt Tools, die beim Einstellen von Spezifikationen und beim Schreiben von RTL-Code helfen. Diese Werkzeuge erleichtern den Prozess und verbessern das Design. Mit Simulations werkzeugen können Sie beispiels weise den RTL-Code testen, um sicher zustellen, dass er wie geplant funktioniert.

Eine Fallstudie zeigt, wie hilfreich RTL-Tools sein können. Das Debuggen mit Kontroll punkten half dabei, Probleme schneller zu finden als nur die Verwendung von Protokollen. DieseVerbesserte die Pass quote von 72,4% auf 93,6%. Es zeigt, wie fortschritt liche Tools das ASIC-Design verbessern können.

|

Konfiguration |

Pass Rate (%) |

Verbesserung (%) |

|---|---|---|

|

Vanille LLM |

72.4 |

N/A |

|

Ein-Agent |

83.9 |

11.5 |

|

Multi-Agent |

93.6 |

21.2 |

Die Verwendung dieser Tools kann Ihren ASIC zuverlässiger machen und besser arbeiten.

Funktions überprüfung

Die funktionale Überprüfung prüft, ob der Chip wie geplant funktioniert.Es stellt sicher, dass der Chip seine Ziele erreicht und Fehler vermeidet. Das Überspringen dieses Schritts kann zu Ausfällen führen, Geld verschwenden und Kunden verärgern. Eine frühzeitige Überprüfung hilft, Fehler zu erkennen und den Chip zuverlässiger zu machen.

Stellen Sie sicher, dass das Design korrekt ist

Dieser Schritt stellt sicher, dass der Chip seinem Plan entspricht und gut funktioniert. Es senkt Risiken wie kaputte Chips oder schlechte Leistung. Für Unternehmen ohne Fabriken baut es das Vertrauen der Kunden auf, indem es gute Chips liefert. Fabriken verlieren auch weniger Material, wenn Designs verifiziert werden.

-

Warum die funktionale Überprüfung wichtig ist:

-

Stellen Sie sicher, dass der Chip seinem Plan folgt.

-

Senkt die Wahrscheinlichkeit von Chip problemen.

-

Baut Kunden vertrauen auf.

-

Spart Materialien während der Produktion.

-

Simulationen verwenden

Simulationen testen den Chip in verschiedenen Situationen. Sie finden Probleme, bevor sie den Chip herstellen. Diese Tests überprüfen, wie sich der Chip verhält und funktioniert. Methoden wie Logik tests und formale Überprüfungen sind für diesen Schritt üblich.

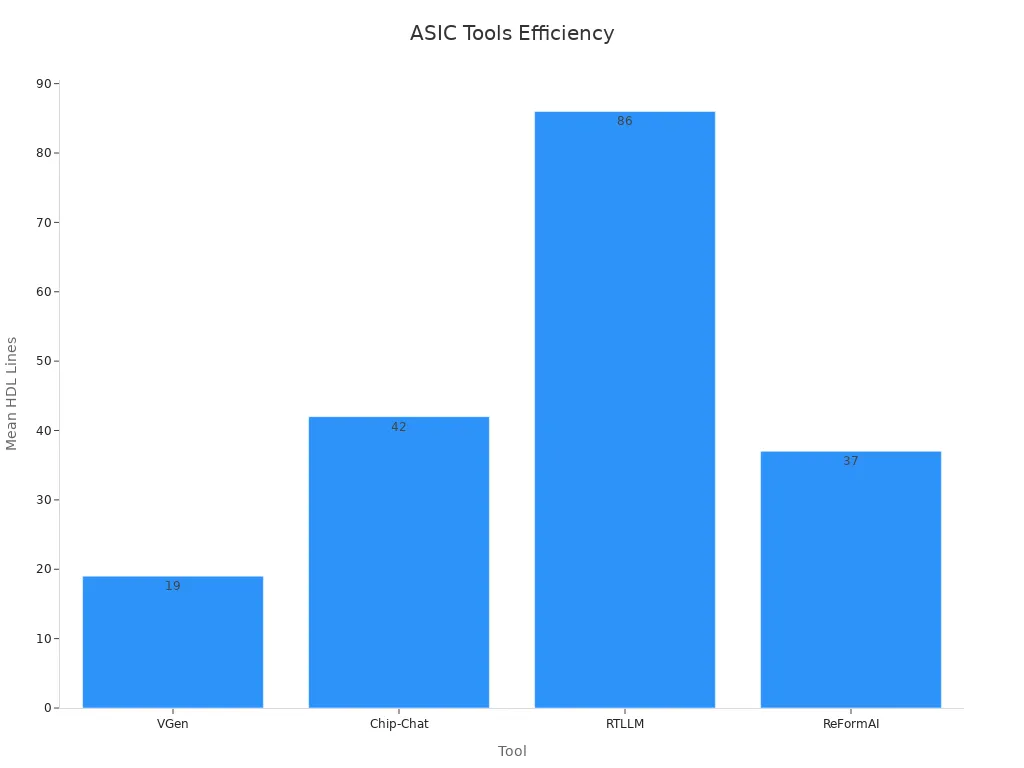

Zum Beispiel helfen Tools wie VGen und RTLLM beim Testen von Chips unterschied licher Größe.Die folgende Tabelle zeigt, wie gut diese Tools mit unterschied lichen Code mengen umgehen:

|

Werkzeug |

Entwürfe getestet |

Code zeilen insgesamt |

Durchschnitt liche Linien |

Max Linien |

Code zeilen insgesamt |

|---|---|---|---|---|---|

|

VGen |

17 |

0,3 K |

19 |

48 |

0,3 K |

|

Chip-Chat |

8 |

0,3 K |

42 |

72 |

0,3 K |

|

RTLLM |

30 |

2.5K |

86 |

518 |

2.5K |

|

ReFormAI |

30 |

2227K |

37 |

773 |

2227K |

Werkzeuge zum Überprüfen von Designs

Spezielle Werkzeuge machen die Überprüfung von Designs einfacher und besser. Diese Tools finden und beheben Probleme schnell. Sie helfen dem Chip auch dabei, seine Ziele zu erreichen und gut zu arbeiten.

Die folgende Tabelle zeigt, wie viel Code verschiedene Tools verarbeiten können:

Die Verwendung dieser Tools beschleunigt den Überprüfung prozess und verbessert den Erfolg des Chips.

RTL auf Gate-Ebene Netlist

Was ist Synthese?

Die Synthese ist ein wichtiger Schritt bei der Herstellung von ASICs. Der RTL-Code (Register Transfer Level) wird in eine Netz liste auf Gate-Ebene geändert. Diese Netz liste zeigt die physischen Logikgatter des Chips. Die Synthese verbindet die Design idee mit dem echten Chip. Es stellt sicher, dass der Chip gebaut werden kann und trotzdem wie geplant funktioniert.

In der Synthese wird das Design für Geschwindigkeit, Größe und Leistung verbessert. Diese Verbesserungen helfen dem Chip, seine Ziele zu erreichen, ohne die Leistung zu verlieren. Zum Beispiel verwandeln Synthese werkzeuge RTL-Code in Standard zellen aus einer Bibliothek. Dadurch entsteht ein Design, das sowohl gut als auch einfach zu machen ist.

Wie RTL zu einer Netlist auf Gate-Ebene wird

Das Ändern von RTL in eine Netz liste auf Gate-Ebene hat Schritte. Erstens verwandeln Synthese werkzeuge RTL-Code in ein grundlegendes Design auf Gate-Ebene. Dann wird das Design verbessert, um es schneller zu machen, weniger Strom zu verbrauchen und besser zu arbeiten. Schließlich wird die Netz liste überprüft, um dem ursprünglichen Plan zu entsprechen.

Dieser Prozess folgt auch Regeln wie Timing-und Größen beschränkungen. Diese Regeln stellen sicher, dass der Chip im wirklichen Leben gut funktioniert. Wenn beispiels weise CPUs oder krypto grafische Chips hergestellt werden, stellen Synthese werkzeuge die Register sehr gut wieder her.Die folgende Tabelle zeigt, wie gut Synthese werkzeuge für verschiedene Designs funktionieren:

|

Hardware-Design-Typ |

Erholungs rate |

Hinweise |

|---|---|---|

|

Krypto grafische Co-Prozessoren |

Fast perfekt |

Stellt hoch rangige Register effektiv wieder her |

|

CPUs |

Fast perfekt |

Funktioniert gut in vielen Designs |

|

Open Titan (SoC) |

Fast perfekt |

Unterstützt von Branchen experten |

Werkzeuge zur Herstellung von Netz listen auf Gate-Ebene

Viele Tools helfen beim Erstellen von Gate-Level-Netz listen für ASICs. Beliebte sind Synopsys Design Compiler, Cadence Genus und Mentor Graphics Precision. Diese Werkzeuge machen die Synthese einfacher und genauer. Sie überprüfen auch das Timing und verbessern den Strom verbrauch, was für gute Chips von entscheidender Bedeutung ist.

Die Verwendung dieser Werkzeuge beschleunigt die Synthese und reduziert Fehler. Beispiels weise überprüft der Synopsys Design Compiler das Timing und steigert die Leistung. Cadence-Gattung hilft, den Strom verbrauch zu senken, und ist damit ein großartiges Werkzeug für das ASIC-Design.

ASIC Design Layout

Grundlagen des Layout-Designs

Das Layout eines ASIC ist wie eine Karte für seine Struktur. Es zeigt, wohin Teile gehen und wie sie sich verbinden. Ein gutes Layout hilft dem Chip, gut zu arbeiten, weniger Strom zu verbrauchen und seine Ziele zu erreichen. Dieser Schritt ist sehr wichtig, da er beeinflusst, wie zuverlässig und nützlich der Chip sein wird.

Während dieses Schritts müssen Sie über viele Dinge nachdenken. Dazu gehören, wo Tore platziert werden müssen, wie sie miteinander verbunden werden und welche Entwurfs regeln eingehalten werden. Jede Wahl ändert, wie der Chip funktioniert und wie einfach er zu machen ist. Beispiels weise kann ein kleineres Layout Signale schneller machen und Strom sparen.

Schritte bei der Erstellung eines Layouts

Das Erstellen eines Layouts hat viele Schritte, um das Design in einen echten Chip zu verwandeln. Zunächst organisiert die Boden planung die Hauptteile des Chips. Dann entscheidet die Platzierung genau, wohin jeder Teil geht. Danach verbindet das Routing die Teile mit Drähten, während Probleme wie Verzögerungen vermieden werden.

Die Überprüfung des Layouts ist in diesem Schritt sehr wichtig. Sie müssen sicherstellen, dass es den Regeln folgt und den Plan erfüllt. Tools suchen nach Problemen wie schlechten Signalen oder Timing-Problemen. Diese Überprüfungen stoppen teure Fehler, bevor der Chip gemacht wird.

Heute,Maschinelles Lernen hilft bei vielen dieser Aufgaben. Es verbessert die Platzierung und das Routing, um Chips besser zu machen und weniger Strom zu verbrauchen. Dies macht den Prozess schneller und schafft qualitativ hochwertigere Layouts.

Werkzeuge für bessere Layouts

Spezielle Werkzeuge machen das Layout-Design einfacher und schneller. KI-betriebene Werkzeuge testen viele Designs, um das beste Layout zu finden. Sie sparen Zeit, verbessern die Leistung und sorgen dafür, dass Chips weniger Strom verbrauchen. Durch die Verwendung früherer Daten erstellen diese Tools bessere Layouts schneller als ältere Methoden.

Zum Beispiel behandeln Werkzeuge des maschinellen Lernens Design aufgaben besser als Menschen. Sie stellen höherwertige Chips her und machen sie schneller fertig. Die Verwendung dieser Tools macht den ASIC-Design prozess reibungsloser und erfolgreicher.

Design für Testtechniken

Das Testen einfacher machen

Wenn Sie das Testen erleichtern, stellen Sie sicherASICFunktioniert gut, nachdem es gemacht ist. Das Entwerfen unter Berücksichtigung von Tests hilft dabei, Probleme frühzeitig zu finden und zu beheben. Dies macht Ihren Chip zuverlässiger und vermeidet kostspielige Fehler während der Produktion.

Bessere Tests verbessern auch die Ergebnisse, nachdem der Chip gebaut wurde. Zum Beispiel:

-

Spezielle Sonden helfen, übrig gebliebene Materialien wie Flussmittel zu messen.

-

Verbesserte Tests liefern genauere elektrische Testergebnisse.

-

Obwohl kniff lig,Meißel-Spitze-SondenSind der Schlüssel für die besten Ergebnisse.

Die Konzentration auf Tests stellt sicher, dass SieASICFunktioniert gut und erfüllt seine Ziele im realen Gebrauch.

Gemeinsame Gestaltungs möglichkeiten für Tests

Design für Test (DFT) Methoden erleichtern das Überprüfen und Reparieren von Chips. Diese Methoden umfassen:

-

Scan-Ketten: Interne Register in einer Kette verknüpfen, um Fehler zu finden.

-

Eingebauter Selbst test (BIST): Lassen Sie den Chip selbst testen und benötigen Sie weniger Ausrüstung.

-

Grenz scan: Überprüft Verbindungen zwischen Chips, um sicher zustellen, dass sie kommunizieren.

Die Verwendung dieser Methoden erleichtert das Testen und verbessert die Qualität Ihres Chips.

Werkzeuge zum Testen des Designs

Viele Werkzeuge helfen beiDFTTechniken. Beliebte sind Synopsys DFTMAX, Cadence Modus und Mentor Tessent. Diese Tools automatisieren Aufgaben wie das Hinzufügen von Scan ketten und das Erstellen von Test mustern.

Zum Beispiel erhöht Synopsys DFTMAX die Testbarkeit, ohne die Leistung zu beeinträchtigen. Cadence Modus verkürzt die Testzeit und findet mehr Fehler. Mentor Tessent fügt erweiterte Funktionen für BIST-und Boundary-Scans hinzu.

Die Verwendung dieser Tools beschleunigt das Testen und stellt sicher, dass IhreASICIst zuverlässig und führt gut.

Boden planung

Anordnen von Chip-Teilen

Die Boden planung ist ein wichtiger Schritt bei der Herstellung von ASICs. Es bedeutet, die Teile des Chips so anzuordnen, dass sie gut funktionieren und eine bessere Leistung erbringen. In diesem Schritt entscheiden Sie, wohin jeder Teil des Chips geht. Sie denken über Dinge wie die Verbindung von Teilen, den Stromfluss und die Signalstärke nach. Ein guter Grundriss hilft dem Chip, schneller zu laufen, weniger Strom zu verbrauchen und seine Ziele zu erreichen.

Ein wichtiger Teil der Boden planung ist der Umgang mit Netzen. Netze sind die Verbindungen zwischen Chip teilen. Zum Beispiel,60-70%Von Netzen verbinden sich nur mit einem anderen Teil. Diese Netze verbinden häufig Teile in der Nähe und haben Muster, die leicht zu erkennen sind. Netze, die mit mehr als einem Teil verbunden sind, haben eine gleichmäßigere Verbreitung. Wenn Sie diese Muster kennen, können Sie Drähte planen und Probleme mit Leistung oder Geschwindigkeit vermeiden.

|

Statistische Beschreibung |

Wert/Details |

|---|---|

|

Prozentsatz der Netze mit FO = 1 |

60-70% |

|

Eigenschaften von FO = 1 |

Langer Schwanz, Spitzen für enge Nachbarn und Untergruppen-Routing |

|

Eigenschaften von FO > 1 |

Symmetrische und flachere Verteilung |

|

Ansatz der Drahtlast-Tabelle |

80-90% Perzentil für Worst-Case-Kapazitäts schätzung |

|

Variation in der Netto länge |

Hängt von der Blockgröße ab (z. B. 25 k-Gate vs. 5 k-Gate) |

|

Abhängigkeit von der Blockform |

Statistik für quadratische Blöcke berechnet |

|

Abhängigkeit vom Netlist-Typ |

Variiert basierend auf Synthese beschränkungen (z. B. Mindest verzögerung gegenüber Mindest fläche) |

Wichtige Faktoren für die Boden planung

Wenn Sie ein Chip-Layout planen, müssen Sie über viele Dinge nachdenken. Dazu gehören die Größe und Form der Teile, die Wärme kontrolle und der Stromfluss. Beispiels weise kann die Planung von Wärme dazu beitragen, dass der Chip kühl bleibt und besser funktioniert. Durch das Platzieren von Teilen an den richtigen Stellen können Signale schneller und Kabel kürzer werden.

KI-Tools helfen jetzt bei der Boden planungIndem Sie Aufgaben automatisch erledigen. AI schaut sich Designs schnell an und findet die besten Layouts. Das spart Zeit und macht bessere Chips als per Hand.

Werkzeuge für die Boden planung

Moderne Werkzeuge machen die Boden planung einfacher und besser. Mit diesen Tools können Sie verschiedene Layouts ausprobieren und Probleme mit dem Timing oder der Strom versorgung beheben. KI-gestützte Tools können Layouts erstellen, die Geschwindigkeit und Energie verbrauch in Einklang bringen. Sie finden auch heiße Bereiche und schlagen Korrekturen vor, um den Chip zuverlässig zu halten.

Die Verwendung dieser Werkzeuge macht die Boden planung schneller und genauer. Dieser Schritt ist sehr wichtig, um ASICs herzustellen, die im wirklichen Leben gut funktionieren.

Platzierung

Anordnen von Komponenten für beste Leistung

Das Platzieren von Komponenten auf einem Chip ist sehr wichtig. Es beeinflusst, wie schnell und effizient der Chip funktioniert. Platzierung bedeutet, Teile so zu organisieren, dass sie Verzögerungen reduzieren und Strom sparen. Eine gute Platzierung erleichtert auch das Verbinden von Drähten später.

Um die Platzierung qualität zu überprüfen, verwenden Designer bestimmte Maßnahmen. Zwei gemeinsame sindHalber Perimeter Draht länge (HPWL)UndSchlimmste negative Slack (WNS). Diese helfen zu zeigen, wie sich die Platzierung auf Geschwindigkeit und Energie verbrauch auswirkt. In der folgenden Tabelle werden diese Maßnahmen erläutert:

|

Metrik |

Was es bedeutet |

Warum es wichtig ist |

|---|---|---|

|

HPWL |

Kürzere Draht wege |

Spart Strom und beschleunigt den Datenfluss |

|

WNS |

Timing-Probleme |

Das Reparieren verbessert die Leistung |

|

FREQ |

Chip geschwindigkeit |

Höhere Frequenz bedeutet schnelleren Betrieb |

Indem Sie sich auf diese konzentrieren, können Designer sicherstellen, dass der Chip seine Ziele erreicht.

Möglichkeiten, Komponenten zu platzieren

Es gibt verschiedene Möglichkeiten, Teile auf einem Chip anzuordnen. Eine Methode ist die "Standard zellen platzierung", bei der kleine Teile in Reihen aufgereiht sind. Das spart Platz und verkürzt Drähte. Ein anderer Weg ist die "Makro platzierung", bei der große Teile an erster Stelle stehen. Kleinere Teile werden später hinzugefügt, um die Leistung zu verbessern.

Fort geschrittene Methoden wie simuliertes Glühen und Partition ieren werden ebenfalls verwendet. Diese Techniken testen viele Layouts, um das beste zu finden. Beispiels weise bewegt das simulierte Glühen Teile, um die Draht länge zu verringern und überfüllte Bereiche zu vermeiden.

Werkzeuge für eine einfachere Platzierung

Spezielle Tools helfen dabei, Platzierung aufgaben zu automatisieren und die Ergebnisse zu verbessern. Tools wie Cadence Innovus, Synopsys IC Compiler II und Mentor Graphics Olympus-SoC sind beliebt. Sie suchen nach Problemen wie überfüllten Kabeln, Zeit problemen und Strom verbrauch.

Die folgende Tabelle zeigt, was diese Werkzeuge messen:

|

Metrik |

Was es prüft |

|---|---|

|

Schlimmste negative Slack (WNS) |

Findet das größte Timing-Problem im Design. |

|

Gesamt negative Slack (TNS) |

Add alle Timing-Probleme, um die Gesamt leistung zu sehen. |

|

Anzahl der Verstöße (NVP) |

Zählt Pfade, bei denen die Timing-Regeln nicht bestehen. |

|

Überlastung |

Prüft, ob die Drähte in einigen Bereichen zu voll sind. |

|

Draht länge (WL) |

Misst die Gesamtlänge der Drähte auf dem Chip. |

|

Halber Perimeter Draht länge (HPWL) |

Schätzt die Draht länge durch Summieren des halben Umfangs der Begrenzung boxen. |

|

Makro-HPWL (mHPWL) |

Konzentriert sich auf die Draht länge nur für große Teile. |

Die Verwendung dieser Tools hilft, Chips zu erstellen, die schnell, effizient und zuverlässig sind.

Uhr Baum Synthese

Chip-Teile synchron halten

Der Uhrbaum ist ein Schlüssel teil eines Chips. Es stellt sicher, dass alle Teile des Chips gleichzeitig zusammenarbeiten. Wenn das Timing aus ist, funktioniert der Chip möglicher weise nicht gut. Der Uhrbaum sendet das Taktsignal an jeden Teil des Chips. Dies hält das Timing stabil und hilft dem Chip, reibungslos zu laufen. Es ist sehr wichtig für die Herstellung eines zuverlässigen und effizienten ASIC.

Die Clock-Tree-Synthese balanciert das Timing des Taktsignals. Dieses Gleichgewicht wird als Taktgeber bezeichnet und muss klein bleiben, um Probleme zu vermeiden. Ein gutes Uhrbaum design reduziert Verzögerungen und hilft dem Chip, eine bessere Leistung zu erbringen.

Schritte zum Entwerfen eines Uhrbaums

Die Herstellung eines Uhrbaums hat mehrere Schritte, um das Timing und die Leistung zu verbessern. Entscheiden Sie zunächst, woher die Taktsignale kommen und wie sie sich ausbreiten. Stellen Sie dann sicher, dass das Taktsignal alle Teile gleichzeitig erreicht. Eine Möglichkeit, Strom zu sparen, ist das Uhr-Gating, bei dem nicht verwendete Teile des Uhrbaums aus geschaltet werden. Clock Gating kann bis zu 20% Strom sparen, kann den Chip jedoch etwas größer machen.

Eine andere Methode ist die Uhrbaum-bewusste Platzierung. Dies senkt die Netto schalt leistung um25,3% und Gesamt leistung um 11,4%. Dies wirkt sich nur wenig auf das Timing (2,0%) und die Chip größe (1,2%) aus. Das Multi-Corner Multi-Mode-Design (MCMM) hilft auch dabei, die Timing-, Leistungs-und Fertigungs regeln in verschiedenen Situationen zu verbessern.

Werkzeuge für die Herstellung von Uhren bäumen

Spezielle Werkzeuge erleichtern die Uhrbaum synthese. Beliebte sind Synopsys PrimeTime, Cadence Innovus und Mentor Graphics Olympus-SoC. Diese Tools helfen bei der Entwicklung und Überprüfung von Uhr bäumen, um den Timing-und Strombedarf zu decken. Sie enthalten auch Funktionen für Clock Gating und MCMM, die den Prozess beschleunigen.

Die Verwendung dieser Tools hilft Ihrem ASIC-Design, besser zu arbeiten und länger zu halten. Sie lösen Timing-Probleme und reduzieren den Strom verbrauch, wodurch ein zeitlich gut abgestimmter und effizienter Chip entsteht.

Routing

Verbindungs komponenten

Routing verbindet Teile eines Chips mit Drähten. Es stellt sicher, dass sich Signale schnell und korrekt zwischen Chip abschnitten bewegen. Dieser Schritt ist sehr wichtig, da schlechtes Routing den Chip verlangsamen, Strom verschwenden und die Leistung beeinträchtigen kann. Die sorgfältige Planung von Draht wegen vermeidet überfüllte Bereiche und sorgt dafür, dass der Chip gut funktioniert.

Durch das Routing werden Pfade für Signale erstellt, während die Entwurfs regeln eingehalten werden. Diese Regeln umfassen das Auseinander halten von Kabeln, das Vermeiden von Überlappungen und das Reduzieren von Signal problemen. Gutes Routing macht den Chip zuverlässiger und besser für seine Arbeit.

Routing-Strategien

Gute Routing-Strategien helfen Chips, schneller und besser zu arbeiten. Verschiedene Methoden lösen Probleme wie überfüllte Drähte und Zeit verzögerungen. Beispiels weise verbindet die Hybrid bindung mehrere Chips ch ichten und benötigt weniger breite Draht wege. 3D-ICs beheben die Überfüllung von 2D-Kabeln, stellen jedoch Herausforderungen bei vertikalen Verbindungen dar. KI-Werkzeuge platzieren Verbindungs blöcke intelligent in der Nähe von Kanten, um Drahts ch ichten auszug leichen.

|

Routing-Strategie |

Wie es hilft |

|---|---|

|

Hybrid bindung |

Verknüpft mehrere Ebenen und benötigt weniger breite Draht pfade. |

|

3D-ICs |

Behebt die Überfüllung von 2D-Kabeln, fügt jedoch vertikale Verbindungs probleme hinzu. |

|

Platziert Verbindungs blöcke in der Nähe von Kanten, um Drahts ch ichten auszug leichen. |

Fort geschrittene Methoden wie Verstärkungs lernen (RL) machen das Routing schneller. RL verbessert die Draht verbindungs geschwindigkeit gegenüber älteren Methoden um 45% und ist 32% schneller als zeit orientierte Methoden. Insgesamt sind Backend-Prozesse mit Routinier barke its methoden 22% schneller und mit Timing-Methoden um 15% schneller.

-

Verbesserungen durch fort geschrittenes Routing:

-

45% schnellere Draht verbindungenAls Routinier barke its methoden.

-

32% schneller als timing fokussierte Methoden.

-

Backend-Prozess beschleunigung: 22% (Routinier barkeit) und 15% (Timing).

-

Werkzeuge für Routing

Routing-Werkzeuge machen das Verbinden von Chip-Teilen einfacher und genauer. Beliebte Tools sind Cadence Innovus, Synopsys IC Compiler II und Mentor Graphics Olympus-SoC. Diese Tools planen Draht wege, reduzieren das Gedränge und verbessern das Timing. Sie befolgen auch die Design regeln, um die Chip anforderungen zu erfüllen.

Moderne Tools verwenden häufig KI, um das Routing zu verbessern. KI überprüft Designs und findet die besten Draht wege, wodurch Strom und Zeit gespart werden. Die Verwendung dieser Tools beschleunigt das Routing und führt zu besseren Ergebnissen.

Physische Überprüfung prüfungen

Chip-Design überprüfen

Die physische Verifizierung stellt sicher, dass Ihr Chip den Design regeln folgt und funktioniert. In diesem Schritt wird überprüft, ob das Chip-Layout mit dem ursprünglichen Plan überein stimmt. Es stellt auch sicher, dass der Chip beim Bau korrekt funktioniert. Das frühzeitige Beheben von Problemen spart Geld und verbessert die Chip leistung.

Hier sind zwei Haupt kontrollen erforderlich. Bestätigen Sie zunächst, dass das Design den Regeln der Fabrik folgt. Zweitens, stellen Sie sicher, dass das Layout dem logischen Design entspricht. Diese Überprüfungen stellen Probleme wie zu enge Drähte, falsche Abstände oder fehlende Links fest. Durch frühzeitige Lösung dieser Probleme wird der Chip herstellungs prozess reibungsloser.

Möglichkeiten, Entwürfe zu überprüfen

Es gibt verschiedene Möglichkeiten, Ihr Chip-Design zu überprüfen. Design Rule Checking (DRC) stellt sicher, dass das Layout den Werks regeln entspricht. Layout Versus Schema tic (LVS) vergleicht das Layout mit dem Entwurfs plan, um sicher zustellen, dass sie übereinstimmen. Parasitäre Extraktion (PEX) findet unerwünschte elektrische Effekte, die durch das Layout verursacht werden.

Beispiels weise kann die Demokrat ische Republik Kongo Drähte zu nahe beieinander erkennen, was zu Problemen führen kann. LVS prüft, ob jede Verbindung im Layout im Plan vorhanden ist. PEX sagt voraus, wie unerwünschte Effekte die Leistung des Chips verändern könnten. Die Verwendung all dieser Methoden gibt eine vollständige Überprüfung Ihres Chip-Designs.

Werkzeuge für die Chip-Verifizierung

Spezielle Werkzeuge machen die Überprüfung von Designs schneller und einfacher. Beliebte sind Cadence Pegasus, Synopsys IC Valid ator und Mentor Calibre. Diese Tools automatisieren Aufgaben wie DRC, LVS und PEX, sparen Zeit und reduzieren Fehler. Sie geben auch detaillierte Berichte, um Probleme schnell zu beheben.

Zum Beispiel eignet sich Mentor Calibre hervorragend für genaue DRC-und LVS-Prüfungen. Synopsys IC Valid ator handhabt komplexe Designs gut. Cadence Pegasus arbeitet schnell für große Chips. Die Verwendung dieser Werkzeuge stellt sicher, dass Ihr Chip alle Regeln erfüllt und zuverlässig funktioniert.

Vorbereitung der GDSII-Datei

Das Design für die Fertigung vor zubereiten

Der letzte Schritt bei der Herstellung eines ASIC besteht darin, ihn für die Herstellung vor zubereiten. Hier überprüfen Sie, ob das Chip-Design alle Werks regeln erfüllt. Sie stellen auch sicher, dass der Chip richtig funktioniert, sobald er hergestellt ist. Es ist wichtig, Fehler zu beheben, die die Leistung oder Lebensdauer des Chips beeinträchtigen könnten.

Dieser Schritt ist sehr wichtig, da er das digitale Design in einen echten Chip verwandelt. Ein gut vorbereitetes Design hilft, teure Probleme während der Produktion zu vermeiden. Es hält auch den Prozess reibungslos und effizient.

Schritte zum Erstellen einer GDSII-Datei

Um das Design fertig zu machen, müssen Sie eine GDSII-Datei erstellen. Diese Datei ist wie eine Karte des Chips. Es zeigt, wohin alle Teile gehen, wie sich Drähte verbinden und Details zu den Schichten.

Zuerst exportieren Sie das Layout aus Ihren Entwurfs tools in das GDSII-Format. Dann überprüfen Sie die Datei, um sicher zustellen, dass sie perfekt zum Design passt. Schließlich senden Sie die Datei an die Fabrik, um den Chip zu bauen. Jeder Schritt muss sorgfältig durchgeführt werden, um Fehler zu vermeiden, die Probleme verursachen könnten.

Werkzeuge, um mit GDSII-Dateien zu helfen

Es gibt Tools, die das Erstellen und Überprüfen von GDSII-Dateien erleichtern. Einige beliebte sind Cadence Virtuoso, Synopsys IC Compiler II und Mentor Graphics Calibre. Diese Tools automatisieren Aufgaben wie das Ziehen von Layout daten, das Erstellen der Datei und das Auffinden von Fehlern. Sie stellen auch sicher, dass das Design den Fabrik regeln folgt, wodurch die Wahrscheinlichkeit von Produktions problemen verringert wird.

Die Verwendung dieser Tools macht den ASIC-Design prozess schneller und zuverlässiger. Sie helfen, sicher zustellen, dass Ihr Chip wie geplant funktioniert.

Der ASIC-Design prozess ist der Schlüssel zur Herstellung von Spezial chips. Es hilft, Chips zu erstellen, die weniger Strom verbrauchen und gut funktionieren. Ein klarer Plan erleichtert das Verfahren und senkt die Kosten. Das macht es großartig für die Herstellung1.000 bis 100.000 Chips. Die Verwendung getesteter Methoden von Anbietern reduziert Risiken und beschleunigt die Produktion.

Teamwork und smarte Design-Tools sind sehr wichtig für den Erfolg. Diese Werkzeuge machen Aufgaben einfacher und genauer. Sie stellen auch sicher, dass der Chip wie geplant funktioniert. Indem Sie klare Schritte ausführen, können Sie Chips bauen, die Platz sparen und die heutigen technischen Anforderungen erfüllen.

FAQ

Was ist ein ASIC und warum ist es wichtig?

Ein ASIC ist ein spezieller Chip für einen Job. Es funktioniert besser und verbraucht weniger Strom als normale Chips. Branchen wie Autos und Telefone verwenden ASICs für benutzer definierte Lösungen, die ihren Anforderungen entsprechen.

Wie ist ein ASIC gestaltet?

Das Entwerfen eines ASIC hat viele Schritte wie Planen, Überprüfen und Testen. Jeder Schritt stellt sicher, dass der Chip gut funktioniert und gebaut werden kann. Dieser Prozess hilft dabei, zuverlässige und leistungs starke Chips zu erstellen.

Welche Tools helfen bei der Herstellung von ASICs?

Es werden Werkzeuge wie Synopsys Design Compiler und Cadence Innovus verwendet. Sie helfen beim Bauen, Arrangieren und Überprüfen des Chips, um seine Ziele zu erreichen.

Warum ist die Überprüfung der Funktion des Chips wichtig?

Die Überprüfung stellt sicher, dass der Chip wie geplant funktioniert. Es findet Fehler früh und spart Zeit und Geld. Dieser Schritt ist der Schlüssel zur Herstellung eines guten und zuverlässigen Chips.

Wie wirkt sich das Layout auf den Chip aus?

Das Layout zeigt, wohin Teile gehen und wie sie sich verbinden. Ein gutes Layout macht den Chip schneller, spart Strom und verbessert die Funktions weise insgesamt.