Процесс проектирования ASIC: пошаговое руководство по созданию интегральных схем для конкретных приложений

Процесс проектирования ASIC помогает создавать чипы для специального использования. В отличие от обычных процессоров, ASIC дают высокую производительность для конкретных задач.

The Процесс проектирования ASICПомогает делать чипы для специального использования. В отличие от обычных процессоров, ASIC дают высокую производительность для конкретных задач. Эти пользовательские чипы работают лучше, стоят дешевле и делают больше.ASICЭтапы проектирования требуют тщательного планирования и работы. Они важны для таких отраслей, как автомобили, телефоны и гаджеты. Например, электромобили используют ASIC для управления мощностью и общения с деталями. Четкие этапы проектирования ASIC помогают создавать надежные и энергосберегающие чипы для современных нужд.

Ключевые выходы

-

Четкие цели имеют очень важное значение. Они направляют дизайн ASIC и предотвращают большие ошибки.

-

Проверка работы чипа позволяет убедиться, что он работает правильно. Этот шаг находит проблемы рано, экономя время и деньги.

-

Использование интеллектуальных инструментов для кодирования и верстки очень помогает. Эти инструменты делают прочные и быстрые чипы.

-

Удобный для тестирования дизайн упрощает тестирование. Они помогают находить и устранять проблемы на ранней стадии, поэтому чип хорошо работает позже.

-

Для изготовления чипов необходим хороший файл GDSII. Это гарантирует, что дизайн соответствует заводским правилам и работает должным образом.

Спецификация и генерация кода RTL

Характеристики настройки

Первым шагом в создании ASIC является установка спецификаций. Это означает принятие решения о том, что чип должен делать, как быстро он должен работать и какие ограничения он имеет. Этот шаг держит процесс проектирования организованным и на правильном пути. АЧеткая спецификация работает как план, Направляя весь проект. Это помогает избежать ошибок, которые могут задержать работу или увеличить расходы. Этот шаг обычно занимает от 2 до 6 недель, потому что он требует тщательного внимания.

Технические характеристики также помогут вам выяснить основные характеристики чипа. Например, если вы делаете чип для смартфона, вы можете сосредоточиться на экономии энергии и работе быстрее. Четкие спецификации гарантируют, что чип делает то, что он должен делать.

Написание кода RTL

После настройки спецификаций вы можете начать писать код RTL (Register Transfer Level). Этот код показывает, как чип работает и построен. Он использует специальные языки, такие как Verilog или VHDL. Код RTL превращает спецификации в рабочую модель чипа.

На этом этапе вам нужно проверить, что код RTL соответствует спецификациям. Проверка часто помогает найти ошибки раньше и экономит время позже. Например, использование контрольных точек во время отладки может помочь быстрее находить недостающие части или ошибки, делая процесс более плавным.

Инструменты для спецификаций и кода RTL

Есть инструменты, которые помогут с настройкой спецификаций и написанием RTL-кода. Эти инструменты облегчают процесс и улучшают дизайн. Например, инструменты моделирования позволяют протестировать код RTL, чтобы убедиться, что он работает по плану.

Тезическое исследование показывает, насколько полезными могут быть инструменты RTL. Отладка с контрольными точками помогла найти проблемы быстрее, чем просто использование журналов. ЭтотУлучшен показатель прохождения с 72,4% до 93,6%. Он показывает, как передовые инструменты могут улучшить дизайн ASIC.

|

Конфигурация |

Пройдите тариф (%) |

Улучшение (%) |

|---|---|---|

|

Ваниль LLM |

72,4 |

Н/А |

|

Single-Агент |

83,9 |

11,5 |

|

Мульти-Агент |

93,6 |

21,2 |

Использование этих инструментов может сделать ваш ASIC более надежным и работать лучше.

Функциональная проверка

Функциональная проверка проверяет, работает ли чип, как планировалось.Это гарантирует, что чип соответствует своим целям и избегает ошибок. Пропуск этого шага может привести к сбоям, потере денег и расстроению клиентов. Ранняя проверка помогает выявить ошибки и делает чип более надежным.

Убедится, что дизайн правильный

Этот шаг гарантирует, что чип соответствует своему плану и работает хорошо. Это снижает риски, такие как сломанные чипы или низкая производительность. Для компаний без фабрик он укрепляет доверие клиентов, поставляя хорошие чипы. Фабрики также теряют меньше материала, когда проекты проверяются.

-

Почему функциональная проверка имеет значение:

-

Убедитесь, что чип следует своему плану.

-

Снижает вероятность проблем с чипом.

-

Создает доверие клиентов.

-

Сохраняет материалы во время производства.

-

Использование симуляций

Моделирование тестирует чип в разных ситуациях. Они находят проблемы перед изготовлением чипа. Эти тесты проверяют, как чип ведет себя и работает. Методы, такие как логические тесты и формальные проверки, являются общими для этого шага.

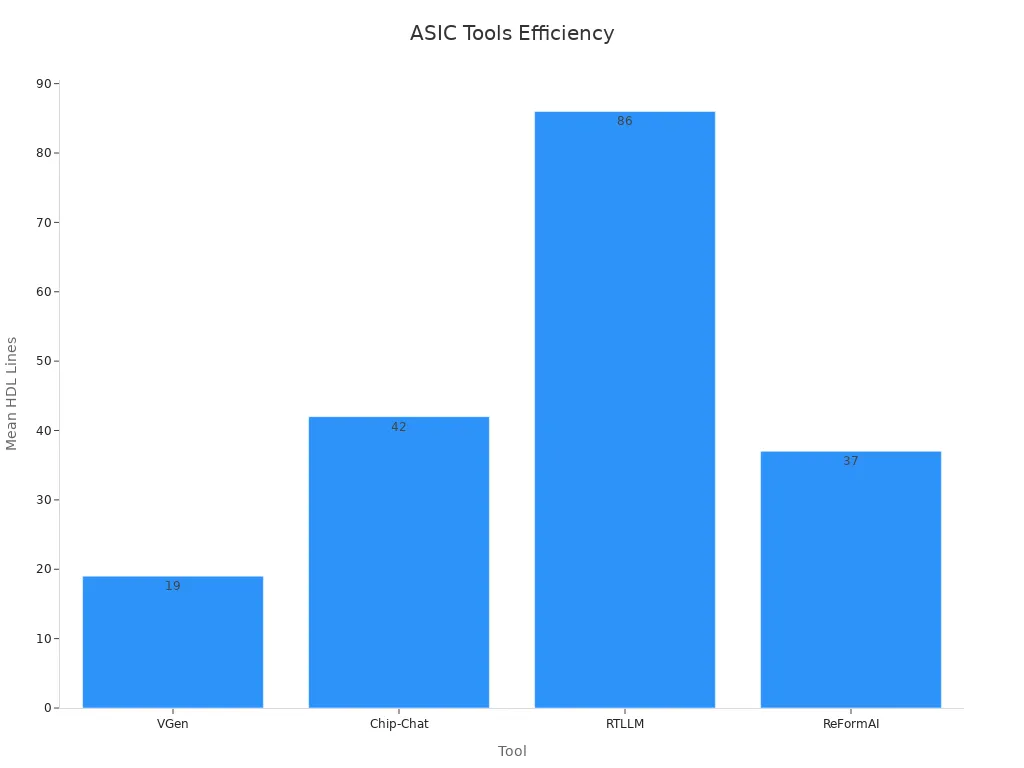

Например, такие инструменты, как VGen и RTLLM, помогают тестировать чипы разных размеров.В таблице ниже показано, насколько хорошо эти инструменты обрабатывают различные объемы кода.:

|

Инструмент |

Протестированные дизайны |

Всего строк кода |

Средние линии |

Максимальные линии |

Всего строк кода |

|---|---|---|---|---|---|

|

Вген |

17 |

0,3 К |

19 |

48 |

0,3 К |

|

Чип-Чат |

8 |

0,3 К |

42 |

72 |

0,3 К |

|

РТЛМ |

30 |

2,5 К |

86 |

518 |

2,5 К |

|

РеформАИ |

30 |

2227 К |

37 |

773 |

2227 К |

Инструменты для проверки дизайнов

Специальные инструменты делают проверку дизайнов проще и лучше. Эти инструменты быстро находят и устраняют проблемы. Они также помогают чипу достичь своих целей и хорошо работать.

На приведенной ниже диаграмме показано, сколько кода могут обрабатывать различные инструменты:

Использование этих инструментов ускоряет процесс проверки и повышает успех чипа.

RTL в список сетей на уровне ворот

Что такое синтез?

Синтез является важным шагом в создании ASIC. Он изменяет код RTL (Register Transfer Level) в список подключений на уровне ворот. В этом списке соединений показаны физические логические вентили чипа. Синтез соединяет дизайнерскую идею с реальным чипом. Это гарантирует, что чип может быть построен и по-прежнему работает, как планировалось.

В синтезе дизайн улучшен для скорости, размера и мощности. Эти улучшения помогают чипу достичь своих целей без потери производительности. Например, инструменты синтеза превращают RTL-код в стандартные ячейки из библиотеки. Это создает дизайн, который одновременно хорош и прост в создании.

Как RTL становится списком сетей на уровне ворот

Изменение RTL на список подключений уровня ворот имеет шаги. Во-первых, инструменты синтеза превращают RTL-код в базовый дизайн на уровне ворот. Затем дизайн улучшается, чтобы сделать его быстрее, потреблять меньше энергии и работать лучше. Наконец, список подключений проверяется на соответствие исходному плану.

Этот процесс также следует правилам, таким как сроки и ограничения размера. Эти правила гарантируют, что чип хорошо работает в реальной жизни. Например, при изготовлении процессоров или криптографических чипов средства синтеза очень хорошо восстанавливают регистры.В таблице ниже показано, насколько хорошо инструменты синтеза работают для различных конструкций.:

|

Тип конструкции оборудования |

Скорость восстановления |

Примечания |

|---|---|---|

|

Криптографические Co-процессоры |

Почти идеально |

Эффективно восстанавливает регистры высокого уровня |

|

ЦП |

Почти идеально |

Хорошо работает со многими дизайнами |

|

OpenTitan (SoC) |

Почти идеально |

При поддержке отраслевых экспертов |

Инструменты для создания сетей на уровне ворот

Многие инструменты помогают создавать списки соединений на уровне ворот для ASIC. Популярные из них-компилятор дизайна Synopsys, ген каденции и точность графики Mentor. Эти инструменты делают синтез проще и точнее. Они также проверяют время и улучшают энергопотребление, что является ключом к хорошим чипам.

Использование этих инструментов ускоряет синтез и уменьшает количество ошибок. Например, компилятор Synopsys Design проверяет время и повышает производительность. Cadence Genus помогает снизить энергопотребление, что делает его отличным инструментом для проектирования ASIC.

Макет дизайна ASIC

Основы дизайна макета

Макет ASIC похож на карту для его структуры. Он показывает, куда идут части и как они соединяются. Хорошая компоновка помогает чипу хорошо работать, потребляет меньше энергии и соответствует своим целям. Этот шаг очень важен, поскольку от него зависит, насколько надежным и полезным будет чип.

На этом этапе вы должны подумать о многих вещах. К ним относятся, где разместить ворота, как их соединить и следующие правила проектирования. Каждый выбор меняет то, как работает чип и насколько легко его сделать. Например, меньшая компоновка может ускорить сигналы и сэкономить электроэнергию.

Шаги по выполнению макета

Создание макета имеет много шагов, чтобы превратить дизайн в настоящую фишку. Во-первых, планирование этажа организует основные части чипа. Затем размещение решает точно, куда идет каждая часть. После этого маршрутизация соединяет детали с проводами, избегая проблем, таких как задержки.

Проверка макета очень важна на этом этапе. Вы должны убедиться, что он соответствует правилам и соответствует плану. Инструменты проверяют наличие проблем, таких как плохие сигналы или проблемы с синхронизацией. Эти проверки останавливают дорогостоящие ошибки перед изготовлением чипа.

Сегодня,Машинное обучение помогает со многими из этих задач. Это улучшает размещение и маршрутизацию, чтобы сделать чипы лучше и потребить меньше энергии. Это делает процесс быстрее и создает более качественные макеты.

Инструменты для лучших макетов

Специальные инструменты делают дизайн макета проще и быстрее. Инструменты на базе ИИ тестируют множество дизайнов, чтобы найти лучший макет. Они экономят время, повышают производительность и заставляют чипы потребляют меньше энергии. Используя прошлые данные, эти инструменты создают лучшие макеты быстрее, чем старые методы.

Например, инструменты машинного обучения справляются с задачами проектирования лучше, чем люди. Они делают чипы более высокого качества и быстрее подготавливают их. Использование этих инструментов делает процесс проектирования ASIC более плавным и успешным.

Дизайн для методов тестирования

Сделать тестирование проще

Упрощение тестирования гарантирует вашASICХорошо работает после того, как сделан. Проектирование с учетом тестирования помогает найти и исправить проблемы на ранней стадии. Это делает ваш чип более надежным и позволяет избежать дорогостоящих ошибок во время производства.

Лучшее тестирование также улучшает результаты после того, как чип построен. К примеру:

-

Специальные зонды помогают измерять остатки материалов, таких как флюс.

-

Улучшенное тестирование дает более точные результаты электрических испытаний.

-

Хотя сложно,Зонды с долотом и наконечникомЯвляются ключом к лучшим результатам.

Сосредоточение внимания на тестировании гарантирует вашASICРаботает хорошо и отвечает своим целям в реальном использовании.

Общие способы проектирования для тестирования

Дизайн для тестирования (ДПФ) Методы облегчают проверку и исправление чипов. Эти методы включают:

-

Цепи сканирования: Свяжите внутренние регистры в цепочку, чтобы найти неисправности.

-

Встроенный сам-тест (BIST): Дает возможность самому проверить чип, требуя меньше оборудования.

-

Граничное сканирование: Проверяет соединения между микросхемами, чтобы убедиться, что они обмениваются данными.

Использование этих методов упрощает тестирование и улучшает качество вашего чипа.

Инструменты для тестирования дизайна

Многие инструменты помогают сДПФТехники. Популярные из них-Synopsys DFTMAX, Cadence Modus и Mentor Tessent. Эти инструменты автоматизируют такие задачи, как добавление цепочек сканирования и создание тестовых шаблонов.

Например, Synopsys DFTMAX повышает тестируемость без ущерба для производительности. Cadence Modus сокращает время тестирования и находит больше неисправностей. Mentor Tessent добавляет расширенные возможности для сканирования BIST и границ.

Использование этих инструментов ускоряет тестирование и гарантирует вашASICНадежен и работает хорошо.

Планирование этажа

Организация частей чипа

Планирование этажей является ключевым шагом в создании ASIC. Это означает, что части чипа работают хорошо и работают лучше. На этом этапе вы решаете, куда идет каждая часть чипа. Вы думаете о таких вещах, как соединение частей, поток мощности и сила сигнала. Хороший план этажа помогает чипу работать быстрее, потреблять меньше энергии и достигать своих целей.

Одной из важных частей планирования этажей является обработка сетей. Сетки-это звенья между частями чипа. К примеру,60-70%Сетей соединяются только с одной другой частью. Эти сети часто связывают близлежащие части и имеют узоры, которые легко обнаружить. Сетки, которые соединяются с более чем одной частью, имеют более равномерное распространение. Знание этих шаблонов поможет вам спланировать провода и избежать проблем с мощностью или скоростью.

|

Статистическое описание |

Значение/Детали |

|---|---|

|

Процентная доля сетей с FO = 1 |

60-70% |

|

Характеристики FO = 1 |

Длинный хвост, пики для близких соседей и маршрутизация подгрупп |

|

Характеристики FO > 1 |

Симметричное и плоско распределение |

|

Подход к таблице проволочной нагрузки |

80-90% процентиль для оценки емкости в худшем случае |

|

Различия в чистой длине |

Зависит от размера блока (например, 25 k-gate против 5 k-gate) |

|

Зависимость от формы блока |

Статистика рассчитана для квадратных блоков |

|

Зависимость от типа списка подключений |

Вариируются на основе ограничений синтеза (например, минимальная задержка против минимальной площади) |

Важные факторы планирования этажа

Планируя макет чипа, вы должны думать о многих вещах. К ним относятся размер и форма деталей, контроль нагрева и поток мощности. Например, планирование тепла может помочь чипу оставаться прохладным и работать лучше. Кроме того, размещение деталей в нужных местах может сделать сигналы быстрее и провода короче.

Инструменты ИИ теперь помогают в планировании этажейПутем автоматического выполнения задач. ИИ быстро просматривает дизайн и находит лучшие макеты. Это экономит время и делает чипы лучше, чем делать это вручную.

Инструменты для планирования этажей

Современные инструменты делают планирование этажей проще и лучше. Эти инструменты позволяют попробовать различные макеты и устранить проблемы со временем или мощностью. Инструменты на основе ИИ могут создавать макеты, которые балансируют скорость и потребление энергии. Они также находят горячие области и предлагают исправления, чтобы чип оставался надежным.

Использование этих инструментов делает планирование этажей более быстрым и точным. Этот шаг очень важен для создания ASIC, которые хорошо работают в реальной жизни.

Размещение

Организация компонентов для лучшей производительности

Размещение компонентов на чипе очень важно. Это влияет на то, насколько быстро и эффективно работает чип. Размещение означает организацию частей, чтобы они сокращали задержки и экономили электроэнергию. Хорошее размещение также облегчает подключение проводов позже.

Чтобы проверить качество размещения, дизайнеры используют определенные меры. Двумя распространенными являютсяДлина провода Полу-периметра (ХПВЛ)ИХудший отрицательный провал (WNS). Они помогают показать, как размещение влияет на скорость и использование энергии. В таблице ниже разъясняются эти меры:

|

Метрика |

Что это значит |

Почему это важно |

|---|---|---|

|

ПВЛ |

Более короткие пути проводов |

Экономит электроэнергию и ускоряет поток данных |

|

WNS |

Проблемы синхронизации |

Их фиксация повышает производительность |

|

ФРЕК |

Скорость чипа |

Более высокая частота означает более быструю работу |

Сосредоточившись на них, дизайнеры могут убедиться, что чип соответствует своим целям.

Способы размещения компонентов

Есть разные способы расположить детали на чипе. Одним из методов является «стандартное размещение ячеек», когда мелкие детали выстраиваются в ряды. Это экономит место и укорачивает провода. Другим способом является «макро размещение», которое ставит большие части на первое место. Меньшие детали добавляются позже для повышения производительности.

Также используются передовые методы, такие как имитация отжига и разделения. Эти методы проверяют множество макетов, чтобы найти лучший. Например, сымитированный отжиг двигает части вокруг для уменьшения длины провода и для избежания переполненных областей.

Инструменты для более легкого размещения

Специальные инструменты помогают автоматизировать задачи размещения и улучшить результаты. Такие инструменты, как Cadence Innovus, Synopsys IC Compiler II и Mentor Graphics Olympus-SoC, популярны. Они проверяют такие проблемы, как переполненные провода, проблемы с синхронизацией и использование энергии.

В таблице ниже показано, что измеряют эти инструменты:

|

Метрика |

Что это проверяет |

|---|---|

|

Худший отрицательный провал (WNS) |

Находит самую большую проблему времени в дизайне. |

|

Общее отрицательное слабину (TNS) |

Добавляет все проблемы со сроками, чтобы увидеть общую производительность. |

|

Количество нарушающих путей (NVP) |

Подсчитывает пути, которые не выполняют правила синхронизации. |

|

Заторы |

Проверяет, не слишком ли тесно провода в некоторых местах. |

|

Длина провода (WL) |

Измеряет общую длину проводов на чипе. |

|

Половинная длина провода периметра (HPWL) |

Оценивает длину провода, суммируя половину периметра ограничительной коробки. |

|

Макро HPWL (mHPWL) |

Ориентирован на длину провода только для больших деталей. |

Использование этих инструментов помогает создавать чипы, которые являются быстрыми, эффективными и надежными.

Синтез дерева часов

Сохранение деталей чипа в синхронизации

Дерево часов является ключевой частью чипа. Это гарантирует, что все части чипа работают вместе одновременно. Если время отключено, чип может работать не очень хорошо. Дерево часов отправляет тактовый сигнал в каждую часть чипа. Это обеспечивает стабильную синхронизацию и помогает чипу работать плавно. Это очень важно для создания надежной и эффективной ASIC.

Синтез часового дерева работает, чтобы сбалансировать время тактового сигнала. Этот баланс называется перекосом часов, и он должен оставаться небольшим, чтобы избежать проблем. Хороший дизайн дерева часов снижает задержки и помогает чипу работать лучше.

Шаги по дизайну дерева часов

Создание дерева часов имеет несколько шагов для улучшения времени и мощности. Сначала решите, откуда приходят сигналы часов и как они будут распространяться. Затем убедитесь, что тактовый сигнал достигает всех частей одновременно. Одним из способов экономии энергии является стробосс часов, который отключает неиспользуемые части дерева часов. Стробоскопические часы могут сэкономить до 20% энергии, но могут сделать чип немного больше.

Другой метод-размещение часов в соответствии с деревом. Это снижает чистую мощность переключения на25,3% и общая мощность на 11,4%. Он делает это с небольшим влиянием на время (2,0%) и размер чипа (1,2%). Multi-Corner Multi-Mode (MCMM) дизайн также помогает, улучшая сроки, мощность и производственные правила в различных ситуациях.

Инструменты для изготовления часов Деревья

Специальные инструменты упрощают синтез дерева часов. Популярными из них являются Synopsys PrimeTime, Cadence Innovus и Mentor Graphics Olympus-SoC. Эти инструменты помогают проектировать и проверять деревья часов на соответствие времени и потребностям в электроэнергии. Они также включают функции для стробирования часов и MCMM, что делает процесс быстрее.

Использование этих инструментов помогает вашему дизайну ASIC работать лучше и дольше. Они решают проблемы с синхронизацией и сокращают потребление энергии, создавая своевременный и эффективный чип.

Маршрутизация

Подключение компонентов

Маршрутизация связывает части чипа с проводами. Это обеспечивает быстрое и правильное перемещение сигналов между секциями микросхемы. Этот шаг очень важен, потому что плохая маршрутизация может замедлить работу чипа, тратить энергию и снизить производительность. Планирование проволочных дорожек тщательно избегает переполненных мест и обеспечивает хорошую работу чипа.

Маршрутизация создает пути для сигналов, следуя правилам проектирования. Эти правила включают в себя разрозненные провода, предотвращение перекрытий и уменьшение проблем с сигналом. Хорошая маршрутизация делает чип более надежным и лучшим для своей работы.

Стратегии маршрутизации

Хорошие стратегии маршрутизации помогают чипам работать быстрее и лучше. Различные методы решают такие проблемы, как переполненные провода и задержки времени. Например, гибридное соединение соединяет несколько слоев чипа, требуя меньшего количества широких проводных путей. 3D ICs исправить 2D скученность проводов, но добавить проблемы с вертикальными соединениями. Инструменты AI аккуратно размещает соединительные блоки возле краев, чтобы сбалансировать слои проводов.

|

Стратегия маршрутизации |

Как это помогает |

|---|---|

|

Гибридное склеивание |

Связи несколько слоев, требующих меньшего количества широких проводных путей. |

|

3D ИС |

Исправляет скученность 2D проводов, но добавляет проблемы вертикального подключения. |

|

Размещает соединительные блоки вблизи краев для балансировки слоев проводов. |

Продвинутые методы, такие как обучение с подкреплением (RL), ускоряют маршрутизацию. RL улучшает скорость проводного соединения на 45% по сравнению со старыми методами и на 32% быстрее, чем методы, ориентированные на время. В целом, бэкенд-процессы на 22% быстрее с методами маршрутности и на 15% быстрее с методами синхронизации.

-

Улучшения от расширенной маршрутизации:

-

45% быстрее проводные соединенияЧем методы маршрутности.

-

32% быстрее, чем методы, ориентированные на время.

-

Ускорение бэкенд-процесса: 22% (маршрутизируемость) и 15% (синхронизация).

-

Инструменты для маршрутизации

Инструменты маршрутизации делают соединение деталей микросхемы проще и точнее. Популярные инструменты включают Cadence Innovus, компилятор микросхем Synopsys II и Mentor Graphics Olympus-SoC. Эти инструменты планируют пути проводов, уменьшают скученность и улучшают время. Они также следуют правилам проектирования для удовлетворения потребностей чипов.

Современные инструменты часто используют ИИ для улучшения маршрутизации. ИИ проверяет проекты и находит лучшие проводные пути, экономя электроэнергию и время. Использование этих инструментов ускоряет маршрутизацию и дает лучшие результаты.

Проверки физической проверки

Проверка дизайна чипа

Физическая проверка гарантирует, что ваш чип соответствует правилам проектирования и работает. Этот шаг проверяет, соответствует ли компоновка микросхемы исходному плану. Это также гарантирует, что чип будет работать правильно при построении. Раннее решение проблем экономит деньги и повышает производительность чипа.

Здесь необходимы две основные проверки. Во-первых, подтвердите, что дизайн соответствует заводским правилам. Во-вторых, убедитесь, что макет соответствует логическому дизайну. Эти проверки обнаруживают такие проблемы, как слишком близкие провода, неправильное расстояние или недостающие звенья. Решение этих проблем на ранней стадии делает процесс изготовления чипов более плавным.

Способы проверки дизайна

Есть разные способы проверить дизайн вашего чипа. Проверка правил проектирования (DRC) гарантирует, что компоновка соответствует заводским правилам. Компоновка против схемы (LVS) сравнивает компоновку с планом проектирования, чтобы убедиться, что они соответствуют. Паразитическая экстракция (PEX) обнаруживает нежелательные электрические эффекты, вызванные макетом.

Например, DRC может обнаружить провода слишком близко друг к другу, что может вызвать проблемы. LVS проверяет, что каждое соединение в макете существует в плане. PEX предсказывает, как нежелательные эффекты могут изменить производительность чипа. Использование всех этих методов дает полную проверку конструкции вашего чипа.

Инструменты для проверки чипа

Специальные инструменты делают проверку дизайнов быстрее и проще. Популярные из них включают Cadence Pegasus, Synopsys IC Validator и Mentor Calibre. Эти инструменты автоматизируют такие задачи, как DRC, LVS и PEX, экономя время и уменьшая количество ошибок. Они также предоставляют подробные отчеты для быстрого устранения проблем.

Например, калибр Mentor отлично подходит для точных проверок DRC и LVS. Валидатор Synopsys IC хорошо справляется со сложными конструкциями. Cadence Pegasus работает быстро для больших чипов. Использование этих инструментов гарантирует, что ваш чип соответствует всем правилам и работает надежно.

Подготовка файла GDSII

Получение дизайна готовым к производству

Последний шаг в создании ASIC-это подготовка к производству. Здесь вы проверяете, соответствует ли конструкция чипа всем заводским правилам. Вы также убедитесь, что чип будет работать правильно, как только он будет сделан. Важно исправить любые ошибки, которые могут повредить работе чипа или его работе.

Этот шаг очень важен, потому что он превращает цифровой дизайн в настоящий чип. Хорошо подготовленный дизайн помогает избежать дорогостоящих проблем во время производства. Это также делает процесс гладким и эффективным.

Шаги по созданию файла GDSII

Чтобы получить готовый дизайн, вам нужно создать файл GDSII. Этот файл-как карта чипа. Он показывает, куда идут все части, как соединяются провода, и детали о слоях.

Во-первых, вы экспортируете макет из ваших инструментов проектирования в формат GDSII. Затем вы проверяете файл, чтобы убедиться, что он идеально соответствует дизайну. Наконец, вы отправляете файл на завод для сборки чипа. Каждый шаг нужно делать осторожно, чтобы избежать ошибок, которые могут вызвать проблемы.

Инструменты для помощи с файлами GDSII

Существуют инструменты, которые упрощают создание и проверку файлов GDSII. Некоторые популярные из них-Cadence Virtuoso, Synopsys IC Compiler II и Mentor Graphics Calibre. Эти инструменты автоматизируют такие задачи, как вытягивание данных макета, создание файла и поиск ошибок. Они также гарантируют, что дизайн соответствует заводским правилам, снижая вероятность производственных проблем.

Использование этих инструментов делает процесс проектирования ASIC более быстрым и надежным. Они помогают гарантировать, что ваш чип работает как запланировано.

Процесс проектирования ASIC является ключом к созданию микросхем специального назначения. Это помогает создавать чипы, которые потребляет меньше энергии и работают хорошо. Четкий план облегчает процесс и снижает затраты. Это делает его отличным для изготовленияОт 1000 до 100 000 чипов. Использование проверенных методов от поставщиков снижает риски и ускоряет производство.

Командная работа и умные инструменты проектирования очень важны для успеха. Эти инструменты делают задачи более простыми и точными. Они также гарантируют, что чип работает по плану. Следуя четким шагам, вы можете создавать чипы, которые экономят место и отвечают современным техническим потребностям.

Часто задаваемые вопросы

Что такое ASIC, и почему это имеет значение?

ASIC-это специальный чип, сделанный для одной работы. Он работает лучше и потребляет меньше энергии, чем обычные чипы. Такие отрасли, как автомобили и телефоны, используют ASIC для пользовательских решений, соответствующих их потребностям.

Как же разрабатывается ASIC?

Проектирование ASIC имеет много шагов, таких как планирование, проверка и тестирование. Каждый шаг гарантирует, что чип работает хорошо и может быть построен. Этот процесс помогает создавать надежные и высокопроизводительные чипы.

Какие инструменты помогают сделать ASIC?

Используются такие инструменты, как компилятор дизайна Synopsys и Cadence Innovus. Они помогают в создании, организации и проверке чипа для достижения его целей.

Почему важна проверка работы чипа?

Проверка гарантирует, что чип работает как запланировано. Он находит ошибки рано, экономя время и деньги. Этот шаг является ключом к созданию хорошего и надежного чипа.

Как макет влияет на чип?

Макет показывает, куда идут части и как они соединяются. Хорошая компоновка делает чип быстрее, экономит энергию и улучшает его работу в целом.