Lo que determina la velocidad de SPI Una guía completa

La interfaz periférica serial (SPI) es famosa por la transferencia de datos de alta velocidad. Este protocolo de comunicación síncrona permite

ElInterfaz periférica serial()SPIEs famoso porTransferencia de datos de alta velocidad. EstoProtocolo de comunicación síncronoPermite datos eficientesTransferenciaEntreDispositivos, Con algunosTasas de transferencia de datos Superior a 100 MHz. ¿Por qué tu proyecto noRendimientoSiempre golpeó estos topTasas de transferencia de datos¿? Tu verdaderoVelocidad SPIY en generalRendimientoEstán limitados por tres áreas clave.

💡El finalRendimientoDe cualquierSPIDatosTransferenciaEs un equilibrio de tuDispositivos', Los límites de hardware, la calidad de la conexión física y la configuración del software.

Puntos clave

- La velocidad de su SPI depende de tres cosas principales: los límites de hardware de sus dispositivos, la calidad de sus conexiones físicas y cómo configura su software.

- Compruebe siempre los límites de velocidad en las hojas de datos para los dispositivos maestro y esclavo. El dispositivo más lento establece la velocidad máxima para su bus SPI.

- Un buen diseño de PCB es importante. Mantenga los cables cortos, coincida con las longitudes de las trazas y use un plano de tierra fuerte para evitar problemas de señal a altas velocidades.

- Uso directoMemoriaAcceso (DMA) en su software para el mejor rendimiento. DMA le permite a suMicrocontroladorEnviar datos rápidamente sin ralentizar el procesador principal.

El papel del hardware en la velocidad SPI

El primer paso para comprender la velocidad máxima de SPI de su sistema es observar el hardware en sí. Antes de escribir una línea de código o diseñar una PCB, las hojas de datos para sus dispositivos maestros y esclavos establecen un límite superior duro. Su rendimiento final está fundamentalmente ligado a las capacidades de estosCircuitos integrados.

Límites del reloj maestro

Su dispositivo maestro, normalmente un microcontrolador, genera el reloj SPI (SCK). Este dispositivo tiene una frecuencia máxima a la que puede operar suInterfaz periférico serial. Puede encontrar este límite en elSección de características eléctricas de su hoja de datos. Las tablas a menudo especifican el maximoFSCK(Frecuencia de reloj SPI) bajo diferentes voltajes de funcionamiento.

Por ejemplo, la hoja de datos de un microcontrolador podría presentar sus características SPI de esta manera:

| Símbolo | Parámetro | Condiciones | Min. | Typ (en inglés) | Máx. | Unidad |

|---|---|---|---|---|---|---|

| FSCK | Frecuencia de reloj SPI | Controlador modo de receptor 2,7 V <VDD <3,6 V | -- | -- | 45 | MHz |

| Controlador modo transmisor 2,7 V <VDD <3,6 V | -- | -- | 45 | MHz |

Nota:Los valores de la tabla anterior se basan en

FPCLKx/3, DondeFPCLKxEs el reloj periférico. El valor máximo real depende de la arquitectura específica del microcontrolador.

El propio reloj del sistema del maestro también juega un papel. El periférico SPI a menudo se ejecuta en un reloj derivado del reloj principal del sistema.

- La arquitectura de reloj interno de un microcontrolador puede limitar el reloj de entrada del módulo SPI. Por ejemplo, un módulo sólo puede aceptar una entrada máxima de48 MHz.

- Este reloj de entrada se divide entonces para generar la señal SCK final para la transferencia SPI.

- Esto significa que incluso si el periférico SPI puede funcionar teóricamente más rápido, su rendimiento está límite por el reloj que lo alimenta.

Restricciones del reloj esclavo

Ahora, considere el dispositivo esclavo. Cada esclavo SPI, ya sea unSensorEl chip de memoria, u otro microcontrolador, también tiene una frecuencia de reloj máxima que puede manejar. Este es a menudo el cuello de botella más significativo en una configuración maestro/esclavo.Exceder este límite hará que el esclavo malinterprete los datos, lo que lleva a la corrupción de datos durante la transferencia..

💡Su bus SPI es tan rápido como su dispositivo más lento. La velocidad de comunicación final debe ajustarse al menor de los dos máximos (maestro o esclavo).

Debe comprobar cuidadosamente la hoja de datos del esclavo. Puede encontrar diferentes tasas máximas de transferencia de datos dependiendo de la operación. Por ejemplo, unEl microcontrolador STM32 en modo esclavo podría admitir 40 MHz para recibir datos, pero una velocidad menor como 24 MHz para la comunicación dúplex completa. Estas diferencias pueden surgir de la lógica interna requerida para muestrear y enviar datos simultáneamente. Para la mayoría de los dispositivos esclavos SPI, una regla de oro segura es mantener la tasa de reloj SPI por debajo deUna décima parte de la frecuencia de reloj del sistema del esclavoPara garantizar una transferencia de datos fiable.

Retrasos de procesamiento esclavo

Una alta frecuencia de reloj no siempre es igual a un alto rendimiento. La verdadera medida del rendimiento es la cantidad de datos que puede transferir a lo largo del tiempo. Muchos dispositivos esclavos necesitan una pausa entre las transacciones para procesar la información. Esto es conocido comoTiempo de procesamiento esclavoORetraso entre transacciones.

Imagina que envías un comando a un sensor. El sensor necesita tiempo para realizar una medición antes de tener los datos listos para la siguiente transferencia. Un reloj SPI rápido es inútil si el maestro tiene que esperar mucho tiempo para que el esclavo esté listo. Este retraso afecta dramáticamente su rendimiento general de datos.

Algunos escenarios comunes que requieren este retraso incluyen:

| Escenario | Por qué es necesario un retraso |

|---|---|

| El esclavo tiene una lógica interna lenta | El dispositivo necesita tiempo para procesar el byte de datos anterior. |

| Protocolos SPI multitrama | El protocolo en sí mismo requiere un intervalo de tiempo específico entre tramas. |

| SPI Flash escribe página | El chip de memoria debe hacer una pausa para bloquear una dirección antes de escribir datos. |

| Evitar errores de temporización | Un pequeño retraso puede ayudar a evitar errores a velocidades de reloj SPI muy altas. |

Entonces, ¿cómo sabes cuando el esclavo está listo para la próxima transferencia? Los dispositivos utilizan varios métodos para señalar su estado:

- Pin ocupado:Algunos dispositivos tienen un pin de salida dedicado que afirman para indicar que están ocupados procesando.

- Registro de estado:Puede sondar un registro de estado en el esclavo. Este registro a menudo contiene bits como

Por trdy(Transmitir listo) oRrdy(Recibir listo) para indicar su estado. - Interrupciones:El esclavo puede usar estos bits de estado para desencadenar una interrupción en el maestro, señalando activamente que está listo para la siguiente transacción SPI.

Capa física de la interfaz periférica en serie

Una vez que entiendas los límites de tuCircuitos integradosDeben observar las conexiones físicas entre ellos. Las pistas y cables de la placa de circuito impreso (PCB) que forman su bus SPI no son conductores perfectos. A altas frecuencias, estas rutas físicas introducen su propio conjunto de desafíos que pueden degradar la calidad de la señal y limitar su rendimiento general.

Trayectoria y diseño de señal

Cables largos y trazas de PCB pueden actuar como pequeñas antenas. Este comportamiento introduce retardo de propagación, que es el tiempo que tarda una señal en viajar desde el maestro a los dispositivos esclavos. A bajas velocidades, este retraso es insignificante. A altas tasas de transferencia de datos, se convierte en un problema importante.

Los desajustes en la longitud de la traza entre las líneas de reloj (SCK) y de datos (MOSI/MISO) causan errores de temporización. La señal de reloj puede llegar al receptor en un momento diferente al de los datos. Esto puede hacer que el dispositivo esclavo bloquee el bit de datos incorrecto, corrompiendo toda la transferencia. A medida que aumenta la frecuencia de su señal, el período de reloj se acorta, lo que hace que su diseño sea mucho más sensible incluso a pequeñas diferencias en el retraso de propagación.

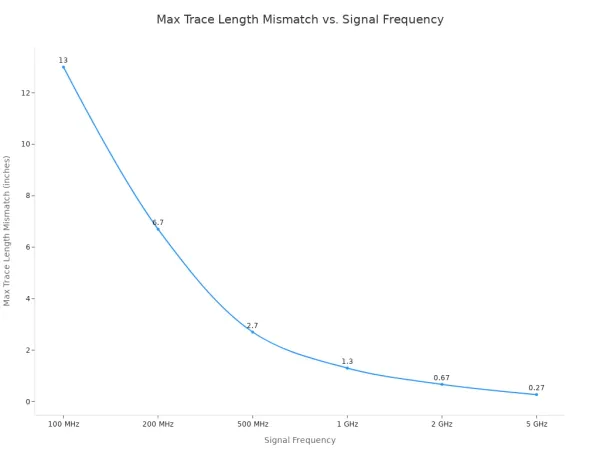

La siguiente tabla muestra la rapidez con que la tolerancia para la discordancia de longitud de traza se reduce a medida que aumenta la frecuencia de reloj SPI.

| Frecuencia de la señal | Período del reloj (T) | Max Skew Tolerance (20% T) | Retraso de propagación (FR4) | Desajuste de longitud de traza máx. |

|---|---|---|---|---|

| 100 MHz | 10 ns | 2 ns | ~ 150 ps/in | 13 en |

| 200 MHz | 5 ns | 1 ns | ~ 150 ps/in | ~ 6,7 en |

| 500 MHz | 2 ns | 0,4 ns | ~ 150 ps/in | ~ 2,7 en |

| 1 GHz | 1 ns | 0,2 ns | ~ 150 ps/in | 1,3 en |

| 2 GHz | 0,5 ns | 0,1 ns | ~ 150 ps/in | ~ 0,67 en |

| 5 GHz | 0,2 ns | 0,04 ns | ~ 150 ps/in | ~ 0,27 en |

Pro Tip:Cuando su bus SPI opera en el rango de 50-100 MHz, debe tratar las trazas como líneas de transmisión. Para evitar reflexiones de señal y timbre, puede agregar terminación de serie pequeñaResistencias(Por ejemplo, 22-33Ω) cerca de los pines del conductor. Colóquenlos en las líneas SCK, MOSI y CS en el maestro y en la línea MISO en cada esclavo.

Capacitancia e integridad del bus

Cada elemento en su PCB, desde elIC pinsA las trazas mismas, añade una pequeña cantidad de capacitancia no deseada. Esto se llamaCapacitancia parásita. Existe entre la traza de la señal y su plano de referencia más cercano, generalmente el plano de tierra. Si bien no puedes eliminarlo, debes manejarlo.

Esta capacitancia afecta directamente el tiempo de subida de la señal. El tiempo de subida es la rapidez con la que la señal puede pasar de un voltaje bajo a un voltaje alto.La alta capacitancia del bus actúa como un obstáculo, resistiendo la capacidad de la señal para elevarse. Esto ralentiza el tiempo de subida y redondea los bordes afilados de la señal del reloj. Si el borde del reloj se vuelve demasiado lento, el dispositivo esclavo puede no registrarlo correctamente, limitando su velocidad máxima de reloj. Curiosamente,La capacitancia tiene un efecto mucho menor en el tiempo de caída de la señal.

La adición de más dispositivos esclavos al bus SPI aumenta la capacidad de carga total, lo que puede degradar aún más la integridad de la señal. Puede controlar este efecto parasitario a través del diseño cuidadoso de PCB.

- Utilice laminados de capa superficial más delgadosPara reducir la distancia al plano de tierra adyacente.

- Elija materiales de baja Dk (constante dieléctrica)PCB para reducir la capacitancia total.

- Seleccionar componentes con tamaños de plomo más pequeñosMinimizar su contribución.

Crosstalk y ruido

Crosstalk ocurre cuando la energía electromagnética de un rastro de señal "se filtra" en un rastro vecino. En una PCB, esto ocurre a menudo entre dos trazas SPI que corren lado a lado. Esta energía acoplada crea ruido en el rastro de la "víctima". Si el ruido es lo suficientemente grande, puede causar falsas transiciones de señal y corromper la transferencia de datos.

Este fenómeno se debe principalmente al acoplamiento capacitivo. La mejor manera de combatir la diafonía y otros ruidos externos es con un plano de tierra bien diseñado.

Un plano de tierra sólido proporciona una trayectoria de retorno de baja impedancia para las corrientes de señal. Esto aprieta los campos electromagnéticos alrededor del rastro de la señal, conteniéndolos y previniéndolos de interferir con otras señales.Un plano de referencia más cercano conduce a un acoplamiento más estrecho y menos ruido.

Para mejorar su diseño y lograr mayores tasas de transferencia de datos, debe:

- Maximice su plano de tierra:Utilice tanto espacio libre en la PCB como sea posible para el plano de tierra.

- Utilice capas de tierra dedicadas:En tableros multicapa, un plano de tierra dedicado proporciona una excelente separación y reduce el ruido.

- Añadir vias de costura:Si debe dividir un plano de tierra, use vías para "unir" las áreas separadas, creando una ruta continua de baja impedancia.

Al administrar cuidadosamente el diseño, la capacitancia y la conexión a tierra de su PCB, puede preservar la integridad de la señal. Esto le permite ejecutar su bus SPI a una mayor velocidad spi y lograr un mejor rendimiento general.

El impacto del software en el rendimiento de SPI

Su hardware yDiseño de PCBEstablecer el potencial para la comunicación de alta velocidad, pero su software determina si realmente puede lograrlo. Las elecciones que realice en su código, desde la configuración básica del protocolo hasta los métodos de manejo de datos, controlan directamente su rendimiento y rendimiento final de SPI.

Modo SPI y temporización

ElProtocolo SPIEs sincrónico, lo que significa que los dispositivos maestro y esclavo deben estar de acuerdo en el tiempo. Puede configurar esta temporización seleccionando el modo SPI correcto. Un desajuste aquí hará que la transferencia falle por completo. El modo está definido por dos parámetros en la hoja de datos del dispositivo esclavo:

- Polaridad de reloj (CPOL):Esto establece el estado inactivo de la señal de reloj (bajo o alto).

- Fase de reloj (CPHA):Esto determina si los datos se muestrean en el primer (delantero) o en el segundo (trasero) borde del reloj.

Estos dos ajustes se combinan para crear cuatro modos SPI posibles. Si su maestro está configurado en Modo 0 (CPOL = 0, CPHA = 0), espera muestrear datos en un borde de reloj ascendente. Su dispositivo esclavo también debe configurarse para este modo para garantizar una transferencia de datos exitosa. Hacer esto mal es una fuente común de errores que impide la comunicación entre dispositivos.

Overhead del controlador y del sistema operativo

La forma en que su microcontrolador mueve los datos tiene un gran impacto en el rendimiento. Generalmente tiene dos opciones para manejar una transferencia SPI: interrupciones o acceso directo a memoria (DMA). Usar interrupciones es más simple para una transferencia básica, pero crea una sobrecarga de CPU significativa que limita sus tasas máximas de transferencia de datos. Para el alto rendimiento, DMA es el método superior.

💡DMA permite que el periférico SPI transfiera datos directamente hacia o desde la memoria sin involucrar a la CPU. Esto libera a la CPU para realizar otras tareas, aumentando drásticamente la eficiencia de su sistema y permitiendo una mayor velocidad de datos.

La siguiente tabla compara los dos enfoques:

| Característica | SPI impulsado por interrupciones | SPI impulsado por DMA |

|---|---|---|

| Sobrecarga de CPU | Alto; La CPU administra cada transferencia de bytes. | Bajo; CPU libre después de iniciar la transferencia. |

| Rendimiento | Inferior: limitado por la capacidad de la CPU para dar servicio a las interrupciones. | Más alto; Puede alcanzar la velocidad máxima de SPI. |

| Casos de uso | Bueno para baja tasaSensoresO comandos simples. | Ideal para streaming de alta velocidad y grandes bloques de datos. |

Cuando necesite alcanzar las tasas de transferencia de datos más altas de componentes como los ADC de alta resolución o la memoria flash, debe usar DMA. Este enfoque minimiza los retrasos de software y permite que su bus SPI funcione más cerca de sus límites de hardware.

Su velocidad SPI final depende de tres factores clave. Estos son los límites de su hardware, sus conexiones físicas y la eficiencia de su software. Debe considerar las tres áreas para lograr las altas tasas de transferencia de datos por las que SPI es conocido. Un sistema rápido requiere un enfoque completo.

💡Acción para llevar:Para encontrar su verdadera velocidad máxima, primero verifique la hoja de datos del dispositivo esclavo para conocer su límite de velocidad. A continuación, pruebe esta velocidad con su diseño y software de PCB. Ajuste hacia abajo desde allí para encontrar la tasa estable más rápida para su proyecto específico.