SiC MOSFET評価ボードへのガイド

あなたは信じられないほどのスピードと効率のためにSiC MOSFETを選びました。それでも、あなたはおそらく3つの大きなハードルに直面しています: 正確なゲートドライブの実装、cの管理

あなたは信じられないほどのスピードと効率のためにSiC MOSFETを選びました。それでも、正確なゲートドライブの実装、回路寄生の管理、安全なPCBレイアウトの確保という3つの大きなハードルに直面する可能性があります。このガイドは、これらの領域をマスターするための実用的なパスを提供します。Sic mosfet評価ボードは、特にSiC市場が急速に拡大するにつれて、優れたハンズオンツールです。

📈SiCマーケットの概要業界のSiCへの移行は明らかであり、これらの設計スキルはこれまで以上に価値があります。

メトリック

値

市場規模 (2024)

投影サイズ (2033)

US $7300.86百万

CAGR (2024-2033)

22.5%

このリソースは、SiCテクノロジーの完全なパフォーマンスのロックを解除するのに役立つ基本的なルールとベストプラクティスを提供します。

重要なポイント

SiC MOSFETを慎重にドライブします。特定のゲート電圧と保護機能を使用して、それらを最適に機能させます。

小さな不要な電気効果を制御します。ワイヤーを短く保ち、電圧スパイクを止めるために特別な接続を使用してください。

回路基板をデザインするまあ。電源パスを小さくし、高電圧部品を分離して安全性と優れた性能を確保します。

SiC MOSFET評価ボードを使用します。これらの重要な設計ルールの練習とテストに役立ちます。

ゲートドライブ回路の最适化

運転することはできませんSiC MOSFET従来のシリコンデバイスのように。その高速スイッチング速度には、より堅牢で正確なゲートドライブ回路が必要です。SiCの効率と性能の利点を達成するために、設計はクリーンで強力なゲート信号を提供する必要があります。

ゲート電圧選択

最適なパフォーマンスを得るには、適切なゲート電圧を選択する必要があります。より高いターンオン電圧、通常は15Vおよび20V、チャンネルを完全に強化します。これにより、デバイスのオン抵抗 (RDS(on)) が最小限に抑えられ、伝導損失が減少します。

ターンオフの場合は、負の電圧を使用する必要があります。-2Vおよび-5Vを使用します。この負のバイアスは、寄生ターンオンに対する強力な防御を生み出します。高周波スイッチングはゲートの電圧スパイクを引き起こす可能性があり、負の電圧はMOSFETがしっかりとオフになることを保証します。を使用する-3Vバイアスは、例えば、スイッチオフ損失を25% も減らすことができますを使用します。

💡プロのヒント: UVLOを正しく設定するあなたのゲートドライバーのUndervoltage-lockout (UVLO) は重要な安全機能です。SiC MOSFETのミラープラトー領域 (約8〜9V) を大幅に上回るしきい値を設定する必要があります。20Vゲートドライブ用の15VのUVLOは、デバイスが安全に動作し、過度の電圧降下を回避することを保証します。

ゲート抵抗サイジング

ゲート抵抗はスイッチング速度を制御する。抵抗が小さいと、より高速なスイッチングが可能になり、スイッチング損失が減少します。しかし、小さすぎる値は、過度のリンギングおよび電磁干渉 (EMI) を引き起こす可能性がある。あなたの目標は、バランスを見つけることです。Sic mosfet評価ボードには、ゲート用の複数のフットプリントが含まれていることがよくあります抵抗器、アプリケーションの理想的な価値を実験して見つけることができます。

不可欠な保護機能

ゲートドライブ回路には、デバイスの故障を防ぐための堅牢な保護が必要です。2つの主要な特徴はありますアクティブミラークランプおよびDesaturation (DESAT) の保護。

アクティブミラークランプ: この機能は、ミラー効果によって引き起こされる誤ったターンオンを防ぎます。MOSFETがオフになると、クランプはゲートからソースへの低インピーダンス経路を提供する。この経路は、誘導電流をゲートから迂回させ、電圧を抑え、デバイスを安全にオフに保ちます。

Desaturation (DESAT) の保護: これにより、短絡イベント中にMOSFETが保護されます。ドレインからソースへの電圧 (VDS) を監視します。MOSFETのオン中にVDSが設定したしきい値を超えると、ドライバーは安全で制御されたシャットダウンを開始します。

これらの高度なゲートドライブソリューションの実装は複雑になる可能性があります。専門的なサポートのために、あなたはのようなHiSilicon指定のソリューションパートナーに目を向けることができますノヴァそのような技術を展開する専門知識を提供するTechnology Company (HK) Limited。

回路寄生の管理

SiC MOSFETの信じられないほどの速度は彼らの最大の利点ですが、それはまたあなたの最大のデザインの挑戦を作成します。それらのスイッチングトランジェントは、従来のIGBTよりも5〜10倍高速です。この速度は否定的な効果をの増幅します寄生インダクタンスそしてあなたの回路のキャパシタンス。

寄生インダクタンス効果

すべてのワイヤとPCBトレースには寄生インダクタンスがあります。SiC MOSFETを切り替えると、電流は非常に急速に変化します (高いdi/dt)。この急速な変化はaを引き起こします寄生インダクタンスを横切る電圧スパイク、式によって記述されるV = L * (di/dt)を使用します。この電圧オーバーシュートは通常の動作電圧を増加させ、MOSFETの故障定格を簡単に超える可能性があり、デバイスの故障につながります。

最初のスパイクに続いて、寄生インダクタンスに蓄えられたエネルギーは、デバイスの寄生キャパシタンスと共振する。これにより、オシロスコープで見ることができる減衰振動、つまり「リンギング」が作成されます。このリンギングは、電磁干渉 (EMI) の主な原因であり、コンポーネントにさらなるストレスを追加します。

スマートなデザインの選択肢でこれらの効果を管理できます。

使用ケルビンソース接続:TO247-4Lのようなパッケージは、ゲートドライバのための別のソース接続を提供する。これにより、主電源経路がバイパスされ、電圧降下がゲート信号に干渉するのを防ぎ、よりクリーンな切り替えが保証されます。

低インダクタンスパッケージを選択します。D2PAK-7LやDFN8X8などの表面実装パッケージは、内部インダクタンスが大幅に低く設計されています。それらを使用すると、最初から電圧オーバーシュートを最小限に抑えることができます。

寄生容量の問題

寄生容量コンポーネントリード間、PCBトレース間、およびMOSFET自体の内部に存在します。このキャパシタンスは、しばしば小さいが、寄生インダクタンスを有する共振タンク回路を形成する。高速スイッチングイベント中、このL-Cタンク回路は、EMIを生成してデバイスにストレスを与える高周波リンギングを引き起こすものです。寄生インダクタンスを効果的に管理することは、この望ましくない共振を制御する最も直接的な方法である。

測定と特性評価

測定できないものを改善することはできません。ダブルパルステスト (DPT) は業界標準の方法ですスイッチングパフォーマンスを特徴づけ、寄生の影響を定量化します。Sic mosfet評価ボードは、DPTを実施するための完璧なプラットフォームです。

このテストでは、MOSFETのゲートに2つの異なる電圧パルスを適用して、実際の条件下でのターンオン特性とターンオフ特性を測定します。

🔬ダブルパルステストの実施

最初のパルス:長いパルスを適用して、ロードインダクタに希望のテストレベルまで電流を生成します。

ブレークフェーズ:非常に短い期間MOSFETをオフにします。これにより、ターンオフエネルギーを測定できます。

2番目のパルス:MOSFETをオンに戻すには、短い2番目のパルスを適用します。これにより、ターンオンエネルギーと逆リカバリ特性を測定できます。

正確な結果を得るには、テストのセットアップが重要です。あなたが必要になりますオシロスコープ、関数発生器、DC電源、および適切なプローブを使用します。わずかなずれでも損失計算の切り替えに重大なエラーが発生する可能性があるため、電圧と電流のプローブを常に下げて正確なタイミング調整を確保してください。

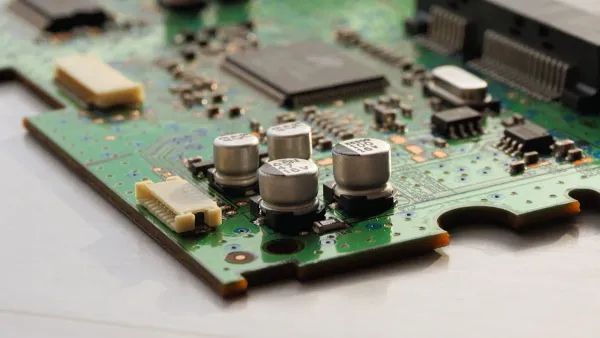

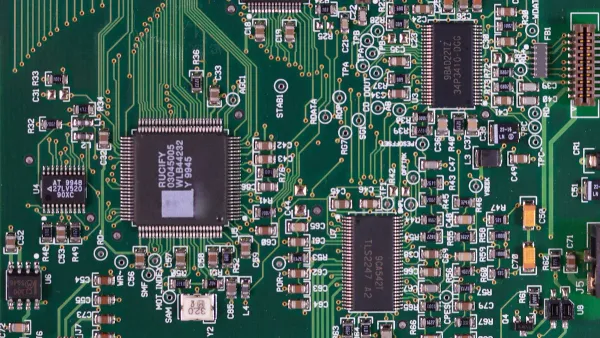

SiC MOSFET評価ボードのレイアウト

メーカーの評価ボードを参照デザインとして表示する必要があります。そのレイアウトは、SiC性能のロックを解除するためのベストプラクティスを明らかにする。レイアウトが悪いと、ノイズ、電圧オーバーシュート、安全上のリスクが発生するため、最適な回路設計でさえ損なわれる可能性があります。

パワーステージレイアウト

パワーステージの主な目標は、寄生インダクタンスを最小限に抑えることです。あなたは高周波パワーループを作る必要があります-DCリンクからのパスコンデンサ、MOSFETを介して、そしてバック-可能な限り小さくてタイトです。を使用する密集したパワーとグランドプレーンを備えた多層PCB効果的な戦略です。このデザインループインダクタンスを抑制し、電圧スパイクを軽減します、パワーデバイスを保護します。

ゲートドライブのループレイアウト

ゲートドライブループは、パワーステージループと同じくらい重要です。大きなゲートループは、スイッチングを遅くし、ゲート信号のリンギングを引き起こす可能性のあるインダクタンスを導入します。

💡レイアウトのヒント: それを近くに保つあなたはすべきですゲートドライバーICをMOSFETのできるだけ近くに置きますを使用します。ゲートドライブとリターンパスをルーティングする微分ペアとして、ループ領域を最小限に抑え、クリーンで高速な信号を確保するために、それらを平行に閉じて実行します。

高電圧の安全性と隔離

安全は交渉不可能です。高電圧回路と低電圧回路を適切に分離する必要があります。これには2つの重要な距離が含まれます。

クリアランス: 2つの導体間の空中を通る最短距離。

クリーページ: 2つの導体間のPCBの表面に沿った最短距離。

のような安全基準で特定の要件を見つけることができますIPC-2221とUL-60950-1を使用します。分離を強化するために、PCBの物理的なスロットを切って下さい高電圧トレース間。これは、クリーページ距離を増加させる。あなたもすべきですあなたのパワーグラウンド (PGND) からあなたのコントロールグラウンド (GND) を分離して下さい、電力ノイズが制御信号を破損するのを防ぐために、単一の静かなポイントでのみ接続します。

熱管理レイアウト

SiC MOSFETは熱くなる可能性があり、PCBレイアウトはその熱を放散するのに役立つ必要があります。表面実装デバイスの場合は、熱がデバイスから大きな銅平面に移動するための低抵抗経路を作成する熱ビア他のレイヤーに。これらの銅飛行機は熱拡散器として機能し、熱を分散させ、局所的なホットスポットを防ぎますを使用します。シックモスフェット評価ボードは、多くの場合、大きく露出した銅領域を備えた優れた熱設計を示します。

SiCテクノロジーの可能性を最大限に引き出すことができます。あなたの成功は3つのコアアクションに依存します。まず、正しい電圧と保護を備えた堅牢なゲートドライブを実装する必要があります。第二に、寄生インダクタンスを最小限に抑えるために、電力とゲートループ領域を縮小する必要があります。第三に、適切なクリアランスとサーマルパスを備えた安全なレイアウトを設計する必要があります。

これらのガイドラインに従うことで、パフォーマンスを大幅に向上させることができます。

リーチ98.5% を超える効率を使用します。

1.657 kW/Lコンバータのような高出力密度を達成します。

より高いスイッチング周波数を使用して、磁気部品のサイズを小さくします。

Sic mosfet评価ボードは、これらのテクニックを実践するための优れたツールです。これらのルールを適用することで、一般的な障害を回避し、非常に効率的でコンパクトな電力システムを構築できます。

よくある質問

シリコンの代わりにSiC MOSFETを使用する必要があるのはなぜですか?

優れた性能のためにSiC MOSFETを選択する必要があります。それらは、より高い効率、より速いスイッチング速度、およびより良い熱伝導率を提供します。これにより、より小さく、より軽く、より効率的に構築できますパワーシステム従来のシリコンデバイスを使用しているものと比較されます。

SiCにとって最も重要なレイアウトルールは何ですか?

寄生インダクタンスを最小限に抑える必要があります。あなたの高周波パワーとゲートドライブループをできるだけ小さくてタイトにしてください。コンパクトなレイアウトにより、電圧のオーバーシュートやリンギングを防ぎ、コンポーネントを保護し、電磁干渉 (EMI) を低減します。

ダブルパルステスト (DPT) とは何ですか?

ダブルパルステストは、MOSFETのスイッチング性能を測定するのに役立ちます。特定の動作条件下でのターンオンとターンオフのエネルギー損失を見つけるために使用します。このテストは、設計を確認し、回路寄生の影響を定量化するために不可欠です。

どのように開始ゲート抵抗値を選択しますか?

SiC MOSFETのデータシートまたは評価ボードで推奨される値から始めることができます。この値は、スイッチング速度とリンギングの間の安全なバランスを提供します。その後、特定のアプリケーションのパフォーマンスを最適化するために調整できます。