ASIC設計プロセス: 特定用途向け集積回路を作成するための段階的なガイド

ASIC設計プロセスは、特別な用途のチップの作成に役立ちます。通常のプロセッサとは異なり、ASICは特定のタスクに対して高いパフォーマンスを提供します。

The ASICデザインプロセス特別な用途のためのチップを作るのに役立ちます。通常のプロセッサとは異なり、ASICは特定のタスクに対して高いパフォーマンスを提供します。これらのカスタムチップはより良く機能し、コストが低く、より多くのことを行います。ASIC設計ステップには慎重な計画と作業が必要です。それらは、自動車、電話、ガジェットなどの業界にとって重要です。たとえば、電気自動車はASICを使用して電力を管理し、部品と話します。ASIC設計の明確なステップは、今日のニーズに対応する信頼性の高い省エネチップを作成するのに役立ちます。

重要なポイント

-

明確な目標は非常に重要です。彼らはASIC設計を導き、大きな間違いを防ぎます。

-

チップの機能を確認すると、正しく機能することがわかります。このステップは問題を早期に発見し、時間とお金を節約します。

-

コーディングとレイアウトにスマートツールを使用すると、非常に役立ちます。これらのツールは強くて速いチップを作ります。

-

テストフレンドリーなデザインはテストを容易にします。それらは問題を早期に見つけて修正するのに役立つので、チップは後でうまく機能します。

-

チップを作るには良いGDSIIファイルが必要です。設計が工場の規則に従い、適切に機能することを保証します。

仕様とRTLコード生成

仕様の設定

ASICを作成する最初のステップは、仕様の設定です。これは、チップが何をすべきか、どれだけ速く機能するか、そしてチップが持つ制限を決定することを意味します。このステップは、設計プロセスを整理して軌道に乗せます。Aクリア仕様はプランのように機能します、プロジェクト全体を指導します。作業を遅らせたり、コストを上げたりする可能性のある間違いを回避するのに役立ちます。注意が必要なため、この手順には通常2〜6週間かかります。

仕様は、チップの主な機能を理解するのにも役立ちます。たとえば、スマートフォン用のチップを作成している場合は、電力の節約と作業の高速化に集中することができます。明確な仕様は、チップが想定されていることを実行することを確認します。

RTLコードの書き込み

仕様を設定したら、RTL (Register Transfer Level) コードの書き込みを開始できます。このコードは、チップの動作と構築方法を示します。VerilogやVHDLなどの特別な言語を使用します。RTLコードは、仕様をチップの作業モデルに変えます。

この段階で、RTLコードが仕様と一致することを確認する必要があります。多くの場合、チェックは間違いを早期に見つけるのに役立ち、後で時間を節約します。たとえば、デバッグ中にチェックポイントを使用すると、不足している部分やエラーをすばやく見つけることができ、プロセスがスムーズになります。

仕様とRTLコードのツール

仕様の設定とRTLコードの作成に役立つツールがあります。これらのツールにより、プロセスが簡単になり、設計が改善されます。たとえば、シミュレーションツールを使用すると、RTLコードをテストして、計画どおりに機能することを確認できます。

ケーススタディは、RTLツールがどれほど役立つかを示しています。チェックポイントを使用したデバッグにより、ログを使用するよりも迅速に問題を見つけることができました。この合格率を72.4% から93.6% に改善しましたを使用します。これは、高度なツールがASIC設計をより良くする方法を示しています。

|

設定 |

パスレート (%) |

改善 (%) |

|---|---|---|

|

バニラLLM |

72.4 |

N/A |

|

単一エージェント |

83.9 |

11.5 |

|

マルチエージェント |

93.6 |

21.2 |

これらのツールを使用すると、ASICの信頼性が向上し、作業が向上します。

機能検証

機能検証は、チップが計画どおりに機能するかどうかを確認します。チップがその目標を達成し、間違いを回避することを確認します。このステップをスキップすると、失敗、お金の浪費、顧客の混乱を引き起こす可能性があります。早期に検証すると、エラーをキャッチし、チップの信頼性を高めることができます。

デザインが正しいことを確認する

このステップは、チップがその計画と一致し、うまく機能することを保証します。壊れたチップやパフォーマンスの低下などのリスクを低下させます。工場のない企業にとっては、優れたチップを提供することで顧客の信頼を築きます。また、設計が検証されたときに工場が失う材料も少なくなります。

-

機能検証が重要な理由:

-

チップがその計画に従っていることを確認します。

-

チップの問題の可能性を下げます。

-

顧客の信頼を構築します。

-

生産中に材料を節約します。

-

シミュレーションの使用

シミュレーションは、さまざまな状況でチップをテストします。彼らはチップを作る前に問題を見つけます。これらのテストは、チップがどのように動作し、実行するかをチェックします。このステップでは、ロジックテストや正式なチェックなどの方法が一般的です。

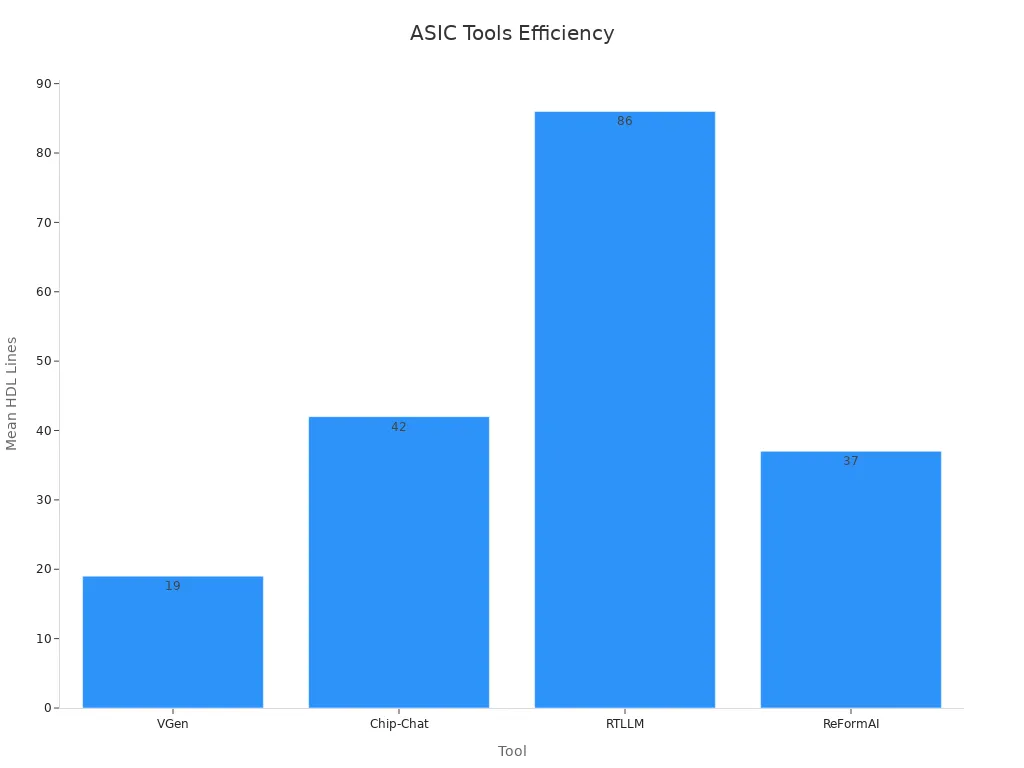

たとえば、VGenやRTLLMなどのツールは、さまざまなサイズのチップをテストするのに役立ちます。以下の表は、これらのツールがさまざまな量のコードをどれだけうまく処理するかを示しています:

|

ツール |

テスト済みのデザイン |

合計コードライン |

平均ライン |

最大ライン |

合計コードライン |

|---|---|---|---|---|---|

|

VGen |

17 |

0.3K |

19 |

48 |

0.3K |

|

チップチャット |

8 |

0.3K |

42 |

72 |

0.3K |

|

RTLLM |

30 |

2.5K |

86 |

518 |

2.5K |

|

ReFormAI |

30 |

2227K |

37 |

773 |

2227K |

デザインをチェックするためのツール

特別なツールにより、デザインのチェックがより簡単かつ優れています。これらのツールは問題をすばやく見つけて修正します。また、チップが目標を達成し、うまく機能するのにも役立ちます。

以下のグラフは、さまざまなツールが処理できるコードの量を示しています。

これらのツールを使用すると、チェックプロセスが高速になり、チップの成功が向上します。

ゲートレベルのネットリストへのRTL

合成とは

合成はASICを作る上で重要なステップです。RTL (レジスタ転送レベル) コードをゲートレベルのネットリストに変更します。このネットリストは、チップの物理論理ゲートを示す。合成は、デザインのアイデアを実際のチップに接続します。チップを構築し、計画どおりに機能することを確認します。

合成では、速度、サイズ、およびパワーのために設計が改善されます。これらの改善は、チップがパフォーマンスを失うことなく目標を達成するのに役立ちます。たとえば、合成ツールはRTLコードをライブラリから標準セルに変換します。これは、良いと作りやすいデザインを作成します。

RTLがゲートレベルのネットリストになる方法

RTLをゲートレベルのネットリストに変更するにはステップがあります。まず、合成ツールはRTLコードを基本的なゲートレベルの設計に変えます。次に、デザインが改善され、より速くなり、より少ない電力を使用し、より良く機能します。最後に、ネットリストは、元の計画と一致するようにチェックされる。

このプロセスは、タイミングやサイズの制限などのルールにも従います。これらのルールは、チップが実際にうまく機能することを確認します。たとえば、CPUまたは暗号化チップを作成する場合、合成ツールはレジスタを非常にうまく回復します。以下の表は、さまざまなデザインで合成ツールがどれだけうまく機能するかを示しています:

|

ハードウェアデザインタイプ |

回復率 |

注意事項 |

|---|---|---|

|

暗号Co-processors |

ほぼ完璧 |

高レベルのレジスタを効果的に回復する |

|

CPU |

ほぼ完璧 |

多くのデザインでうまく機能します |

|

OpenTitan (SoC) |

ほぼ完璧 |

業界の専門家によるサポート |

ゲートレベルのネットリストを作成するためのツール

多くのツールは、ASIC用のゲートレベルのネットリストの作成に役立ちます。人気のあるものは、Synopsys Design Compiler、Cadence Genus、およびMentor GraphicsPrecisionです。これらのツールにより、合成がより簡単かつ正確になります。また、タイミングをチェックし、優れたチップの鍵となる電力使用量を改善します。

これらのツールを使用すると、合成が速くなり、間違いが減ります。たとえば、Synopsys Design Compilerはタイミングをチェックし、パフォーマンスを向上させます。Cadence Genusは、電力使用量を削減するのに役立ち、ASIC設計に最適なツールになります。

ASICデザインレイアウト

レイアウトデザインの基本

ASICのレイアウトは、その構造のマップのようなものです。部品がどこに行き、どのように接続するかを示します。優れたレイアウトは、チップがうまく機能し、より少ない電力を使用し、その目標を達成するのに役立ちます。このステップは、チップの信頼性と有用性に影響するため、非常に重要です。

このステップでは、多くのことを考えなければなりません。これらには、ゲートを配置する場所、それらを接続する方法、および設計ルールに従うことが含まれます。すべての選択により、チップの動作と作成の容易さが変わります。たとえば、レイアウトを小さくすると、信号が速くなり、電力が節約されます。

レイアウトを作成する手順

レイアウトを作成するには、デザインを実際のチップに変えるための多くのステップがあります。まず、フロアプランニングはチップの主要部分を整理します。次に、配置は各パーツの行き先を正確に決定します。その後、ルーティングは遅延などの問題を回避しながら、部品をワイヤで接続します。

このステップでは、レイアウトを確認することが非常に重要です。ルールに従い、計画を満たしていることを確認する必要があります。ツールは、悪い信号やタイミングの問題などの問題をチェックします。これらのチェックは、チップを作る前に高価な間違いを止めます。

今日は、機械学習はこれらのタスクの多くに役立ちますを使用します。配置とルーティングを改善して、チップをより良くし、より少ない電力を使用するようにします。これにより、プロセスが高速になり、高品質のレイアウトが作成されます。

より良いレイアウトのためのツール

特別なツールにより、レイアウト設計がより簡単かつ迅速になります。AIを利用したツールは、多くのデザインをテストして最高のレイアウトを見つけます。時間を節約し、パフォーマンスを向上させ、チップの使用電力を減らします。過去のデータを使用することにより、これらのツールは古い方法よりも迅速に優れたレイアウトを作成します。

たとえば、機械学習ツールは、人間よりも設計タスクをうまく処理します。彼らはより高品質のチップを作り、それらをより速く準備します。これらのツールを使用すると、ASIC設計プロセスがよりスムーズで成功します。

テストテクニックのデザイン

テストをより簡単にする

テストを簡単にすることで、ASICそれが作られた後うまくいきます。テストを念頭に置いて設計すると、問題を早期に見つけて修正するのに役立ちます。これにより、チップの信頼性が高まり、生産中のコストのかかるミスを回避できます。

より良いテストはまた、チップが構築された後の結果を改善します。例:

-

特別なプローブは、フラックスなどの残りの材料を測定するのに役立ちます。

-

改善されたテストはより正確な電気テスト結果を与えます。

-

トリッキーですが、チゼル先端プローブ最もよい結果のためのキーである。

テストに焦点を合わせることはあなたを保障しますASICうまく機能し、実際の使用でその目標を達成します。

テスト用にデザインする一般的な方法

テスト用デザイン (DFT) 方法により、チップのチェックと修正が容易になります。これらの方法は次のとおりです。

-

スキャンチェーン: チェーン内の内部レジスタをリンクして障害を見つけます。

-

内蔵セルフテスト (BIST): 必要な機器を減らして、チップ自体をテストできます。

-

境界スキャン: チップ間の接続をチェックして、チップが通信することを確認します。

これらの方法を使用すると、テストが簡単になり、チップの品質が向上します。

テストデザイン用ツール

多くのツールが役立ちますDFTテクニック。人気のあるものは、Synopsys DFTMAX、Cadence Modus、およびMentor Tessentです。これらのツールは、スキャンチェーンの追加やテストパターンの作成などのタスクを自動化します。

たとえば、Synopsys DFTMAXは、パフォーマンスを損なうことなくテスタビリティを強化します。Cadence Modusはテスト時間を短縮し、より多くの障害を見つけます。Mentor Tessentは、BISTおよび境界スキャン用の高度な機能を追加します。

これらのツールを使用すると、テストが速くなり、ASIC信頼でき、よく実行します。

フロアプランニング

チップ部品の配置

フロアプランニングは、ASICを作成する上で重要なステップです。これは、チップの部品がうまく機能し、より良いパフォーマンスを発揮するように配置することを意味します。このステップでは、チップの各部分がどこに行くかを決定します。部品の接続方法、電力の流れ、信号強度などについて考えます。優れたフロアプランは、チップの実行速度が速くなり、使用電力が少なくなり、目標を達成するのに役立ちます。

フロアプランニングの重要な部分の1つは、ネットの取り扱いです。ネットはチップ部品間のリンクです。たとえば、60-70%ネットの他の1つの部分に接続します。これらのネットはしばしば近くの部分をリンクし、見つけやすいパターンを持っています。複数のパーツに接続するネットは、より均等に広がります。これらのパターンを知ることで、ワイヤを計画し、電力や速度の問題を回避できます。

|

統計の説明 |

値/詳細 |

|---|---|

|

FO = 1のネットの割合 |

60-70% |

|

FO = 1の特性 |

ロングテール、近くの隣人とサブグループルーティングのピーク |

|

FO> 1の特徴 |

対称的でフラットな分布 |

|

Wire-loadテーブルアプローチ |

最悪の場合のキャパシタンス推定のための80-90% パーセンタイル |

|

ネット長のバリエーション |

ブロックサイズに依存 (例えば、25 kゲート対5 kゲート) |

|

ブロック形状への依存 |

正方形ブロックに対して計算された統計 |

|

ネットリストタイプへの依存 |

合成の制約に基づいて変化します (たとえば、最小遅延と最小面積) |

重要なフロア計画要因

チップレイアウトを計画するときは、多くのことを考える必要があります。これらには、部品のサイズと形状、熱制御、および電力の流れが含まれます。たとえば、熱の計画は、チップを涼しく保ち、より良く機能するのに役立ちます。また、部品を適切な場所に配置すると、信号が速くなり、ワイヤが短くなります。

AIツールがフロアプランニングに役立つようになりましたタスクを自動的に実行します。AIはデザインをすばやく見て、最高のレイアウトを見つけます。これは時間を節約し、手作業で行うよりも優れたチップを作ります。

フロアプランニングのツール

最新のツールにより、フロアプランニングがより簡単かつ優れています。これらのツールを使用すると、さまざまなレイアウトを試したり、タイミングやパワーの問題を修正したりできます。AIを利用したツールは、速度とエネルギー使用のバランスをとるレイアウトを作成できます。また、ホットエリアを見つけ、チップの信頼性を維持するための修正を提案します。

これらのツールを使用すると、フロアプランニングがより迅速かつ正確になります。このステップは、実生活でうまく機能するASICを作るために非常に重要です。

配置

最高のパフォーマンスのためのコンポーネントの配置

チップ上にコンポーネントを配置することは非常に重要です。チップの動作速度と効率に影響します。配置とは、部品を整理して遅延を減らし、電力を節約することを意味します。良い配置はまた、後でワイヤを接続することを容易にする。

配置の品質をチェックするために、デザイナーは特定の手段を使用します。2つの一般的なものは半周囲ワイヤー長 (HPWL)と最悪の否定的なスラック (WNS)を使用します。これらは、配置が速度とエネルギーの使用にどのように影響するかを示すのに役立ちます。以下の表は、これらの対策を説明しています。

|

メトリック |

それが意味するもの |

なぜそれが重要なのか |

|---|---|---|

|

HPWL |

より短いワイヤーパス |

パワーを節約し、データフローを高速化 |

|

WNS |

タイミングの問題 |

それらを修正するとパフォーマンスが向上します |

|

FREQ |

チップ速度 |

より高い周波数はより速い操作を意味します |

これらに焦点を当てることにより、設計者はチップがその目標を達成していることを確認できます。

コンポーネントを配置する方法

チップ上に部品を配置するにはさまざまな方法があります。1つの方法は、小さな部品を列に並べた「標準セル配置」です。これはスペースを節約し、ワイヤーを短くします。もう1つの方法は、大きな部品を最初に配置する「マクロ配置」です。小さい部品は性能を改善するために後で加えられる。

シミュレートされたアニーリングや分割などの高度な方法も使用されます。これらの技術は、最良のものを見つけるために多くのレイアウトをテストします。たとえば、シミュレートされたアニーリングは、ワイヤの長さを短縮し、混雑した領域を回避するために部品を移動します。

より簡単な配置のためのツール

特別なツールは、配置タスクの自動化と結果の改善に役立ちます。Cadence Innovus、Synopsys IC Compiler II、Mentor Graphics Olympus-SoCなどのツールが人気です。彼らは、混雑したワイヤー、タイミングの問題、電力使用などの問題をチェックします。

以下の表は、これらのツールの測定値を示しています。

|

メトリック |

チェックするもの |

|---|---|

|

最悪の否定的なスラック (WNS) |

デザインで最大のタイミングの問題を見つけます。 |

|

総否定的なスラック (TNS) |

すべてのタイミングの問題を追加して、全体的なパフォーマンスを確認します。 |

|

違反パス (NVP) の数 |

タイミングルールに失敗するパスをカウントします。 |

|

混雑 |

一部の地域でワイヤーが混雑しすぎているかどうかを確認します。 |

|

ワイヤー長さ (WL) |

チップ上のワイヤの全長を測定します。 |

|

半周囲ワイヤー長 (HPWL) |

バウンディングボックスの半周を合計することにより、ワイヤの長さを推定します。 |

|

マクロHPWL (mHPWL) |

大きい部品だけのためのワイヤー長さに焦点を合わせます。 |

これらのツールを使用すると、高速で効率的で信頼性の高いチップを作成できます。

クロックツリー合成

チップ部品を同期させる

クロックツリーは、チップの重要な部分である。それはチップのすべての部分が同時に一緒に働くことを確認します。タイミングがオフの場合、チップはうまく機能しない可能性があります。クロックツリーは、クロック信号をチップのあらゆる部分に送る。これはタイミングを安定させ、チップの円滑な実行を助ける。信頼性が高く効率的なASICを作るためには非常に重要です。

クロックツリー合成は、クロック信号のタイミングのバランスをとるように働く。このバランスはクロックスキューと呼ばれ、問題を回避するために小さいままでなければなりません。優れたクロックツリー設計により、遅延が軽減され、チップのパフォーマンスが向上します。

クロックツリーをデザインするステップ

時計の木を作るには、タイミングとパワーを改善するためのいくつかのステップがあります。まず、クロック信号がどこから来て、どのように広がるかを決定します。次に、クロック信号がすべての部分に同時に到達することを確認します。電力を節約する1つの方法は、クロックツリーの未使用部分をオフにするクロックゲーティングです。クロックゲーティングは最大20% の電力を節約できますが、チップを少し大きくする可能性があります。

別の方法は、クロックツリー認識配置である。これにより、ネットスイッチング電力が低下します。25.3% 、総電力11.4%を使用します。これは、タイミング (2.0%) とチップサイズ (1.2%) にほとんど影響を与えません。マルチコーナーマルチモード (MCMM) 設計は、さまざまな状況でタイミング、電力、製造ルールを改善することでも役立ちます。

時計の木を作るためのツール

特別なツールにより、クロックツリーの合成が容易になります。人気のあるものは、Synopsys PrimeTime、Cadence Innovus、Mentor GraphicsOlympus-SoCです。これらのツールは、タイミングと電力のニーズを満たすために時計の木を設計およびチェックするのに役立ちます。また、クロックゲーティングとMCMMの機能も含まれているため、プロセスが高速化されます。

これらのツールを使用すると、ASIC設計の作業が改善され、長持ちします。タイミングの問題を解決し、電力使用量を削減し、タイミングの良い効率的なチップを作成します。

ルーティング

接続コンポーネント

ルーティングは、チップの一部をワイヤでリンクします。チップセクション間で信号が迅速かつ正確に移動することを保証します。ルーティングが悪いとチップが遅くなり、電力が無駄になり、パフォーマンスが低下する可能性があるため、このステップは非常に重要です。ワイヤーパスを計画することは、混雑したエリアを慎重に回避し、チップをうまく機能させ続けます。

ルーティングは、設計ルールに従いながら信号のパスを作成します。これらのルールには、ワイヤを離しておくこと、オーバーラップを回避すること、信号の問題を減らすことが含まれます。優れたルーティングにより、チップの信頼性が向上し、仕事が向上します。

ルーティング戦略

優れたルーティング戦略は、チップがより速く、より良く動作するのに役立ちます。さまざまな方法で、混雑したワイヤやタイミングの遅延などの問題を解決します。たとえば、ハイブリッドボンディングは複数のチップ層を接続し、必要なワイドワイヤパスが少なくなります。3D ICは2Dワイヤーの混雑を修正しますが、垂直接続で課題を追加します。AIツールは、接続ブロックをエッジの近くにスマートに配置して、ワイヤーレイヤーのバランスを取ります。

|

ルーティング戦略 |

それがどのように役立つか |

|---|---|

|

ハイブリッドボンディング |

複数のレイヤーをリンクし、必要なワイドワイヤパスが少なくなります。 |

|

3D IC |

2Dワイヤーの混雑を修正しますが、垂直接続の課題を追加します。 |

|

接続ブロックをエッジの近くに配置して、ワイヤ層のバランスを取ります。 |

強化学習 (RL) のような高度な方法により、ルーティングが高速化されます。RLは、以前の方法よりもワイヤ接続速度を45% 向上させ、タイミング重視の方法よりも32% 高速です。全体として、バックエンドプロセスは、ルーティング可能性の方法で22% 高速化され、タイミングの方法で15% 高速化されます。

-

高度なルーティングの改善:

-

45% 高速ワイヤ接続Routabilityメソッドより。

-

タイミング重視の方法より32% 高速。

-

バックエンドプロセスの高速化: 22% (ルーティング可能性) および15% (タイミング)。

-

ルーティングのツール

ルーティングツールにより、チップ部品の接続がより簡単かつ正確になります。人気のあるツールには、Cadence Innovus、Synopsys IC Compiler II、Mentor GraphicsOlympus-SoCなどがあります。これらのツールは、ワイヤーパスを計画し、混雑を減らし、タイミングを改善します。また、チップのニーズを満たすために設計ルールに従います。

最新のツールは、ルーティングを改善するためにAIを使用することがよくあります。AIは設計をチェックし、最適なワイヤパスを見つけて、電力と時間を節約します。これらのツールを使用すると、ルーティングが高速になり、より良い結果が得られます。

物理検証チェック

チップデザインの確認

物理的な検証により、チップが設計ルールに従い、機能することを確認できます。このステップでは、チップレイアウトが元の計画と一致するかどうかを確認します。また、構築時にチップが正しく動作することを保証します。問題を早期に修正すると、コストを節約し、チップのパフォーマンスを向上させます。

ここでは2つの主要なチェックが必要です。まず、デザインが工場のルールに従っていることを確認します。第二に、レイアウトが論理デザインと一致することを確認します。これらのチェックでは、ワイヤが近すぎる、間隔が間違っている、リンクが欠落しているなどの問題が見つかります。これらの問題を早期に解決すると、チップ製造プロセスがスムーズになります。

デザインを確認する方法

チップデザインを確認するにはさまざまな方法があります。デザインルールチェック (DRC) は、レイアウトが工場規則に従うことを保証します。Layout Versus Schematic (LVS) は、レイアウトを設計計画と比較して、一致するようにします。寄生抽出 (PEX) は、レイアウトによって引き起こされる望ましくない電気的効果を発見する。

たとえば、DRCはワイヤを近づけすぎてスポットし、問題を引き起こす可能性があります。LVSは、レイアウト内のすべての接続がプランに存在することを確認します。PEXは、不要な効果がチップのパフォーマンスをどのように変化させるかを予測します。これらすべての方法を使用すると、チップ設計を完全に確認できます。

チップ検証のツール

特別なツールにより、デザインのチェックがより速く簡単になります。人気のあるものには、ケイデンスペガサス、シノプシスICバリデーター、メンターキャリバーなどがあります。これらのツールは、DRC、LVS、PEXなどのタスクを自動化し、時間を節約し、間違いを減らします。また、問題を迅速に解決するための詳細なレポートも提供します。

たとえば、Mentor Calibreは、正確なDRCおよびLVSチェックに最適です。Synopsys IC Validatorは、複雑な設計をうまく処理します。ケイデンスペガサスは大きなチップに対して迅速に機能します。これらのツールを使用すると、チップがすべてのルールを満たし、確実に機能します。

GDSIIファイルの準備

製造のためのデザインの準備をする

ASICを作成する最後のステップは、製造の準備を整えることです。ここでは、チップ設計がすべての工場規則を満たしていることを確認します。また、チップが作成されたら適切に機能することを確認します。チップのパフォーマンスや持続を損なう可能性のある間違いを修正することが重要です。

このステップは、デジタルデザインを実際のチップに変えるため、非常に重要です。よく準備された設計は、生産中の高価な問題を回避するのに役立ちます。また、プロセスをスムーズかつ効率的に保ちます。

GDSIIファイルを作成する手順

デザインを準備するには、GDSIIファイルを作成する必要があります。このファイルは、チップのマップのようなものです。これは、すべての部品がどこに行くか、ワイヤーがどのように接続するか、およびレイヤーの詳細を示します。

まず、デザインツールからレイアウトをGDSII形式にエクスポートします。次に、ファイルをチェックして、デザインと完全に一致することを確認します。最後に、ファイルを工場に送信してチップを構築します。問題を引き起こす可能性のある間違いを避けるために、各ステップを慎重に行う必要があります。

GDSIIファイルを支援するツール

GDSIIファイルの作成とチェックを容易にするツールがあります。人気のあるものには、Cadence Virtuoso、Synopsys IC Compiler II、およびMentor GraphicsCalibreがあります。これらのツールは、レイアウトデータの取得、ファイルの作成、エラーの検索などのタスクを自動化します。また、設計が工場の規則に従うことを保証し、生産上の問題の可能性を減らします。

これらのツールを使用すると、ASIC設計プロセスがより速く、より信頼性が高くなります。それらはあなたのチップが計画通りに機能することを保証するのを助けます。

ASIC設計プロセスは、専用チップを作成するための鍵です。それは、より少ない電力を使用してうまく機能するチップを作成するのに役立ちます。明確な計画により、プロセスが簡単になり、コストが削減されます。これは作ることのために大きいです1,000〜100,000チップをご利用ください。ベンダーのテスト済みの方法を使用すると、リスクが軽減され、生産がスピードアップします。

チームワークとスマートデザインツールは成功のために非常に重要です。これらのツールにより、タスクがより簡単で正確になります。また、チップが計画どおりに機能するようにします。明確な手順に従うことで、スペースを節約し、今日の技術ニーズを満たすチップを構築できます。

よくある質問

ASICとは何ですか、そしてなぜそれが重要なのですか?

ASICは、1つのジョブ用に作られた特別なチップです。それは通常のチップよりもうまく機能し、より少ない電力を使用します。車や電話などの業界は、ニーズに合ったカスタムソリューションにASICを使用しています。

ASICはどのように設計されていますか?

ASICの設計には、計画、チェック、テストなどの多くのステップがあります。各ステップは、チップがうまく機能し、構築できることを確認します。このプロセスは、信頼性が高く高性能なチップを作成するのに役立ちます。

ASICの作成に役立つツールは何ですか?

Synopsys Design CompilerやCadence Innovusなどのツールが使用されています。彼らは、その目標を達成するためにチップの構築、配置、およびチェックを支援します。

チップの機能をチェックすることが重要なのはなぜですか?

チェックすると、チップが計画どおりに機能することが確認されます。それは間違いを早く見つけ、時間とお金を節約します。このステップは、良好で信頼できるチップを作るための鍵です。

レイアウトはチップにどのように影響しますか?

レイアウトは、部品がどこに行き、どのように接続するかを示します。優れたレイアウトにより、チップが高速になり、電力が節約され、全体的な動作が向上します。