集積回路パッケージング: 技術、標準、および将来のトレンド

集積回路パッケージは、半導体が将来どのように機能するかを決定するのに役立ちます。エンジニアは、半導体をより良く機能させるためにパッケージングを使用します。また、デバイスをより小さく、より速くするのに役立ちます。

集積回路パッケージは、半導体が将来どのように機能するかを決定するのに役立ちます。エンジニアは、半導体をより良く機能させるためにパッケージングを使用します。また、デバイスをより小さく、より速くするのに役立ちます。業界は単純な集積回路パッケージから始まりました。現在、より複雑なシステムに高度なソリューションを使用しています。これらのソリューションは、さまざまなタイプの部品の混合にも役立ちます。半導体をより良くするためには、パッケージングが非常に重要になりました。パッケージの変更を見る人は、新しいアイデアを作成するのに役立ちます。

重要なポイント

-

集積回路パッケージングはチップを安全に保ちます。それは異なった部品を一緒に接続します。また、デバイスが小さくて速くなるのにも役立ちます。これにより、それらはより良く機能し、長持ちします。

-

3Dスタッキング、ファンアウトウェーハレベルのパッケージング、チップレットデザインなどの高度なパッケージング方法により、物事がより良く機能します。彼らはより少ない力を使います。また、より複雑なシステムの構築にも役立ちます。

-

JEDECとIPCの業界標準は、パッケージングとテストが良好であることを確認しています。それらは物事を安全に保ち、部品が一緒に機能することを確認するのに役立ちます。

-

新しい材料と冷却技術は、熱の制御に役立ちます。また、最新の半導体パッケージを長持ちさせます。

-

企業は協力して新しいものを発明し続けます。これはチップを作る際の問題を解決するのに役立ちます。また、将来のパッケージングの改善にも役立ちます。

集積回路パッケージングの概要

目的と関数

集積回路パッケージングエレクトロニクスがどれだけうまく機能するかは非常に重要です。エンジニアの使用Ic包装チップと他の部品を一緒に置く。これは完全なシステムを作ります。それは物事を小さくし、それらをより速く働かせるのを助けます。0201および01005のような小さい部品はいかに示しますIc包装デバイスを縮小しますが、より多くの機能を追加します。

のいくつかの主な仕事Ic包装は次のとおりです。

-

回路やその他の部品をサポートする

-

高速信号とデータの電気経路を作る

-

マイクロヒートパイプのような冷却ツールで熱を処理する

-

を維持するIcダメージや环境から安全

-

システムオンパッケージとパッケージオンパッケージで3Dのスタックパーツを支援

-

強力なテストと新しい材料で物事を長持ちさせる

エンジニアは、のような新しい材料を探しますカーボンナノチューブ、作るためにIc包装より良い。の基板Ic包装物事を小さくし、より良く機能させるための鍵でもあります。

ICパッケージングの進化

の物語Ic包装半導体の変化の速さを示しています。1970年代、マルチチップモジュールはさまざまな部品の混合を開始しました。古いIc包装ロジックを置く新しいものに変更された方法、メモリ, センサー、そして一緒にアンテナ。ムーアの法則は2Dだけに追いつくことができなかったため、業界は3Dスタッキングとミキシングパーツに移行しました。

スルーシリコンのvias、インターポーザー、およびFan-out wafer-levelの包装変更されましたIc包装を使用します。これらにより、デバイスの動作が改善され、小さくなり、より多くの作業が可能になります。現在、デバイス、パッケージ、およびPCB設計は、高速コンピューティングとIoTのカスタムソリューションで連携しています。この変更はどのように示しています集積回路包装単純な箱から多くの技術を持つ複雑なシステムに行きました。

業界のスナップショット:

キー統計

詳細

市場規模 (2024)

予測される市場規模 (2033)

901.8億米ドル

CAGR (2025-2033)

9.35%

最大の地域市場

アジア太平洋

最も急成長している地域

北米

支配的なタイプセグメント

オーガニック基板

主要なエンドユーザーセグメント

家電製品

主要な包装技術

SOP、DFN、GA、FOWLP

市場のドライバー

家電、5G、パッケージングの革新に対する需要

主要なマーケットプレーヤー

Amkor、ASEグループ、ヘンケル、日立ケミカル、住友ベークライト、LG化学、Powertech、Toray

注目すべきトレンド

パフォーマンスと小型化のためのFOWLPの採用

地域のハイライト

中国の産業は2023年に18.5% 成長しました。米国は75% のシェアで北米をリードしています

戦略的要因

研究開発、コラボレーション、政府のイニシアチブ

ICパッケージング技術

従来のパッケージ

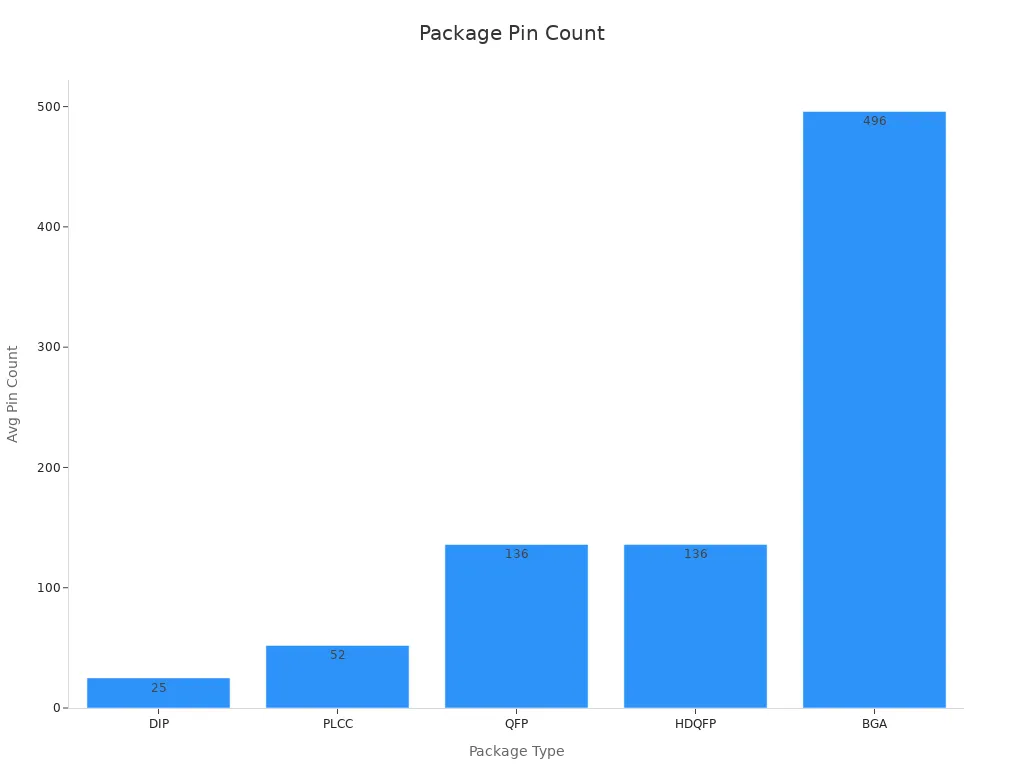

エンジニアは従来を使用しましたIc包装何年もの間。これらのパッケージは、チップの保護と接続に役立ちます。いくつかの一般的なタイプは、デュアルインラインパッケージ (DIP) 、プラスチックリードチップキャリア (PLCC) 、およびクワッドフラットパッケージ (QFP) です。各タイプは特定のデバイスに最適です。

-

DIPは2列のピンを有する。それは8から42ピンを持つことができます。ピンは1.778〜2.54mm離れている。DIPはスルーホール取り付けに適しています。セラミックDIPは非常に信頼性があります。

-

PLCCは、J字型のリードを有する。それは20から84ピンを持つことができます。PLCCはスペースを節約し、表面またはソケットに取り付けることができます。

-

QFPにはガルウィングリードがあります。それは32から240ピンを持つことができます。ピンの間隔は0.4mmと小さくすることができます。QFPは熱を助けるためにパッドを露出させました。

これらの伝統的なIc包装タイプは成熟しており、低コストです。それらは多くの使用のためによく働きます。しかし、ピン数、サイズ、およびパフォーマンスには制限があります。デバイスがより小さく複雑になるにつれて、エンジニアはチップをパッケージ化する新しい方法を必要とします。

注:伝統的なIc包装より長い接続を使用します。これは、より多くの信号損失およびより低い密度を引き起こし得る。

|

パッケージタイプ |

ピンカウント範囲 |

ピッチの範囲 (mm) |

ボディ寸法 (mm) |

厚さの範囲 (mm) |

主なパフォーマンスのハイライト |

|---|---|---|---|---|---|

|

ディップ |

8 - 42 |

1.778 - 2.54 |

幅: 6.35 - 13.97 |

0.81 - 12.96 |

高信頼性のための成熟した、安価な、スルーホール取り付け、セラミックバージョン |

|

PLCC |

20 - 84 |

1.27 |

幅/長さ: 9 - 29.28 |

3.56 - 4.57 |

Jリード、表面またはソケットマウント、スペース効率の高いリード形状 |

|

QFP |

32 - 240 |

0.4 - 0.8 |

幅/長さ: 5 - 45.7 |

1 - 4.9 |

ガルウィングリード、表面マウント、信頼性の高いセラミックバージョン、ヒートシンク用の露出パッド |

高度なソリューション

高度なパッケージングにより、エンジニアの設計方法が変更されましたIc包装を使用します。これらの新しい方法には、ボールグリッドアレイ (BGA) 、チップスケールパッケージ (CSP) 、ウェーフレベルパッケージ (WLP) 、ファンアウトウェーフレベルパッケージ (FOWLP) 、およびシステムインパッケージ (SiP) が含まれます。これらは、接続を短くし、ピンを追加し、信号を改善するのに役立ちます。

-

BGAはリードの代わりにはんだボールを使用します。それは975ピンまで持つことができます。BGAはよりよい熱および電気性能を与える。

-

CSPとWLPは、パッケージをチップとほぼ同じくらい小さくします。これは、デバイスをさらに小さくするのに役立ちます。

-

FOWLPにより、より多くの部品が1つのパッケージに収まります。それはまた熱に役立ちます。

-

SiPは異なる置きますIcロジック、メモリ、RFなどのタイプが一緒になります。これは複雑なデバイスを作るのに役立ちます。

エンジニアは、これらの高度な方法を使用して、高速データ、小型、および優れた熱制御を行います。これらの方法はまた、干渉を減らし、デバイスの信頼性を高める。フリップチップボンディングとスルーシリコンvias (TSV)小さなつながりを作ります。これらの特徴は信号を助け、望ましくない影響を減らす。

-

スマートフォンでは、高度なIc包装プロセッサ、メモリ、およびRFモジュールをまとめます。これにより、電話は強力で小さくなります。

-

自動車では、強力なSiPモジュールが、困難な場所での電子機器の動作に役立ちます。

-

データセンターでは、高速プロセッサは高度なパッケージを使用して速度を向上させ、電力を減らします。

ヒント:高度なIc包装チップを積み重ねて、より短い接続を使用できるようにします。これは、より速い速度、より少ない遅延、およびより良い性能を意味する。

3D ICパッケージング

3DIc包装チップ技術の大きな一歩です。このメソッドスタックIcお互いの上にレイヤー。スルーシリコンビアやシリコンインターポーザーなどを使用します。エンジニアは3Dを使用しますIc包装より高い密度、よりよい信号およびより少ない力の使用のため。

-

2024年には、420億以上の3Dスタックダイユニットが出荷されましたを使用します。これは多くの人々が3Dを使うことを示しますIc包装今だ

-

3Dパッケージは、cm ² あたり最大2,300の接続を持つことができます。

-

FOWLPは0.6 ℃/Wと低い熱抵抗を有する。これは熱に役立ちます。

-

3Dスタックパッケージは現在、ロジックチップの収益の28% を占めています。

|

メトリック/トレンド |

値/統計 |

説明 |

|---|---|---|

|

3D-stackedダイユニット出荷 (2024) |

420億以上 |

3D ICパッケージングの迅速な採用 |

|

3Dパッケージでの相互接続密度 |

Cm ² あたり2,300 I/O |

統合密度の増加 |

|

FOWLPの熱抵抗 |

0.6 °C/W |

熱性能の向上 |

|

3Dスタックパッケージの収益シェア |

ロジックチップの総収益の28% |

重要な市場貢献 |

|

高度なパッケージングを使用したAIアクセラレータ |

72% 以上 (2024) |

パフォーマンスセグメントでの高い採用 |

|

信号の完全性の改善 (FO-PLP) |

FO-WLPより30% 良い |

高められた信号質 |

|

寄生インダクタンスの低下 |

24% 減少 |

電気性能の向上 |

|

TSV耐性改善 |

19% 良い |

垂直相互接続技術の進歩 |

|

チプレットパッケージングによる省電力 |

18% の平均節約 |

エネルギー効率の向上 |

|

商用DRAMのスタッキングレベルを死ぬ |

最大8つのレイヤー |

垂直統合の進歩 |

エンジニアは、チップレット設計を使用して、小さくて再利用可能なブロックを備えた複雑なシステムを構築します。Chipletパッケージを使用すると、ロジック、メモリ、アナログなどのさまざまな機能を1つのSiPに組み合わせることができます。これは、サードパーティのチップレットの設計に役立ち、製品の開発を迅速に行います。

-

Chipletパッケージにより、接続が短くなり、信号が向上します。

-

組み込み型テクノロジーにより、遅延が22% 削減され、最大18% の電力が節約されます。

-

フリップチップバンプピッチは、sub-5nm設計で約80μmになりました。これは物事を小さくするのに役立ちます。

注:2024年の高度な包装市場は703億ドルでした。それは毎年13.2% 成長しました。2026年までに、プロセッサの利益の40% 以上がIc包装改善。

エンジニアは、新しいデバイスにSiPとチップレットソリューションを使用します。これらの方法は、デバイスをより小さく、より速く、より安くするのに役立ちます。業界が成長するにつれて、Ic包装より良いパフォーマンスと新しいアイデアのためにさらに重要になります。

業界標準

JEDECおよびIPC

JEDECとIPCは、集積回路パッケージングの重要なルールを作成します。これらのグループは、企業が製品を設計およびテストするのに役立つドキュメントを作成します。JEDECは半導体デバイスのルールを作成します。IPCはプリント回路基板とアセンブリのルールを作成します。彼らは製品を安全かつ高品質に保つために協力します。

|

標準/ドキュメントタイトル |

標準番号 |

日付 |

目的 |

委員会 |

|---|---|---|---|---|

|

J-STD-020F |

2022年12月 |

安全な包装と取り扱いのための水分感度レベルを定義 |

JC-14、JC-14.1 |

|

|

水分/リフローに敏感なSMDの取り扱い、梱包、配送、使用 |

J-STD-033D |

2018年4月 |

損傷を防ぐために取り扱いと出荷を標準化 |

JC-14、JC-14.1 |

|

信頼性テスト前の非気密表面マウントデバイスの事前調整 |

JESD22-A113I |

4月20 20 |

信頼性テスト用のプレコンディショニングフローを設定 |

JC-14.1 |

|

高温での表面マウントICのパッケージWarpage測定 |

JESD22-B112C |

2023年11月 |

はんだ付け中の対策パッケージwarpage |

JC-14、JC-14.1 |

|

アダプターテストボードの信頼性テストガイドライン |

JEP176A |

2025年6月 |

ガイドの信頼性テストアダプタボード付きIC |

JC-14、JC-14.3 |

これらのルールは、企業が間違いを減らし、より良い協力をするのに役立ちます。また、企業が医療、自動車、家電の法律に従うのにも役立ちます。

品質と相互運用性

品質と相互運用性は、集積回路のパッケージングにとって非常に重要です。IPC-A-600やIPC-6012のようなIPCルール良い外観とパフォーマンスのための明確なステップを設定します。以下の表は、いくつかの主なIPCルールとその機能を示しています。

|

IPCスタンダード |

フォーカスエリア |

ICパッケージング技術の信頼性の検証における役割 |

|---|---|---|

|

IPC-A-600 |

プリントボードの視覚的受容性 |

欠陥のないPCBのみが検査に合格し、パッケージングの信頼性をサポートします。 |

|

IPC-6012 |

リジッドPCBの資格と性能 |

耐久性と長期信頼性の要件を定義します。 |

|

IPC-A-610 |

电子アセンブリの受け入れ可能性 |

ガイドアセンブリ品質、はんだ付け、およびコンポーネントの配置。 |

|

IPC-2221 |

PCBデザインの一般的な標準 |

エラーを減らし、一貫性を向上させるためのベストプラクティスを確立します。 |

|

IPC-7711/7721 |

リワーク、修正、および修理 |

安全なリワークと修理プロセスを提供し、変更後の品質を維持します。 |

テストはプロダクトが一緒によく働くことを確かめるために重要です:

-

内蔵の自己テストアルゴリズム高速接続で問題を見つける。

-

信号整合性モニターは、チップリンクの健全性をチェックします。

-

冗長性と修理は、信号を強く保つために追加のレーンを使用します。

-

高速アクセスとテスト機能は、あらゆるステップでチップをテストするのに役立ちます。

-

環境テストは、チップが熱、電力、およびプロセスの変化にどのように作用するかをチェックします。

企業はこれらのルールとテストを使用して、製品が強力で重要な仕事に適していることを確認します。

ICパッケージングのトレンド

3Dインテグレーション

3D統合は大きなトレンドですIc包装を使用します。この方法は多くを積み重ねますIcお互いの上にレイヤー。それらは、スルーシリコンビアと呼ばれる特別なリンクでレイヤーを接続します。企業は3Dスタッキングを使用して、デバイスの動作を改善し、使用する電力を減らします。また、デバイスを小さくするのにも役立ちます。業界は次のような重要な数字で進捗状況をチェックしますパッケージ、パフォーマンス、パワー、プロファイル、コスト、サイクルタイムを使用します。TSMCのDougYuは、新しいアイデアを導くためにこれらの数字を作成しました。

|

アスペクト |

詳細 |

|---|---|

|

主要パフォーマンスインジケータ (KPI) |

パッケージ、パフォーマンス、パワー、プロファイル、コスト、サイクルタイム (PPPCC) |

|

養子縁組の課題 |

TSVテクノロジーは、コストと技術的な問題のため、コストに敏感なモバイルアプリケーションでは広く採用されていません |

|

2008年のQuimondaの閉鎖により、DRAMスタッキングの採用が遅れた |

|

|

ファンアウトウェーハレベルパッケージング (FOWLP) との競争により、3D ICの採用が置き換えられました |

|

|

採用例 |

一部のスマートフォンはTSVベースの3D ICを使用しており、大量生産を示しています |

|

マイルストーン |

SKハイニックスは2015年に3D TSV DRAMスタック (HBM) を発表しました |

|

2022年頃に予定されているウェーハ間スタッキング (W2W) およびダイツーウェーハ (D2W) による3Dシステム統合 |

|

|

将来の開発 |

D2Wスタッキングの歩留まりとパフォーマンスを向上させるハイブリッドボンディングとピッチスケーリング |

|

業界のロードマップと専門家のコンセンサスが継続的な3D統合の進歩をサポート |

エンジニアは、3D統合におけるコストと技術的な問題の解決に取り組み続けています。ハイブリッドボンディングとピッチスケーリングは、より多くのチップを作成し、パフォーマンスを向上させるのに役立ちます。多くのスマートフォンが3Dを使用Ic包装したがって、この傾向は現在一般的です。専門家は、新しいチップ設計が出現するにつれて、3D統合は成長し続けると考えています。

ファンアウトとウエハーレベル

ファンアウトウェーハレベルパッケージングとウェーハレベルチップスケールパッケージングが変更されましたIc包装たくさん。これらの新しいタイプは、デバイスを小さくし、より多くの部品を詰め込むのに役立ちます。ウェーハレベルのチップスケール包装の市場は2023年には約49億ドルを使用します。2031年までに370億ドル以上に成長する可能性があります。この急速な成長は、多くの企業がこれらの新しい方法を使用していることを示しています。

-

ファンインWLCSPにより、より多くの部品でデバイスをより小さく、より安価にすることができます。

-

ファンアウトウェーハレベルのパッケージングは、ワイヤをチップの外側に広げることにより、I/Oを追加します。これは熱に役立ち、より多くの部品がフィットします。

-

より良いピッチ技術と新しい材料は、より良いチップを作り、コストを下げるのに役立ちます。

-

より短いリンクとより良い熱制御は、デバイスをより良く動作させ、より長く持続させます。

📈業界の洞察:

ファンアウトウェーハレベルのパッケージングとウェーハレベルのチップスケールパッケージングは、デバイスを小型化し、チップの歩留まりを向上させるのに役立ちます。これらの方法により、企業はより少ないお金でより小さく、より強力なデバイスを作ることができます。

エンジニアは、これらのパッケージタイプを電話、ウェアラブル、カーエレクトロニクスに使用します。より小さく、より良いデバイスのプッシュは新しい運転を続けますIc包装アイデア。

不均一な統合

不均一な統合は現在、Ic包装を使用します。この方法は異なるIc1つのパッケージのタイプ、材料および仕事。エンジニアは、スルーシリコンビアを使用して、基板上の多くのチップをリンクします。これは古いサイズ制限を破ります。また、システムを安価にし、チプレットベースのシステムを機能させるのにも役立ちます。

新しい3D異種統合チップは、サブミクロンまで、非常に小さなサイズで接続できます。業界は現在、3Dスタッキング、多くの仕事の混合、およびハイブリッド統合を使用しています。これらの変化は、高密度、より低い電力使用、より小さいサイズ、およびより良い信頼性をもたらす。

Chipletのデザインは、このトレンドにとって非常に重要です。設計者は、ロジック、メモリ、またはアナログジョブ用のチップレットを選択できます。これにより、システムインパッケージソリューションは柔軟かつ迅速に構築できます。また、新製品の発売を早め、チップの新しいアイデアをサポートします。

💡ヒント:

不均一な統合とチップレットの設計は、エンジニアが複雑なシステムをより速く、より簡単にするのに役立ちます。この傾向は、小型で強力な電子機器の必要性を満たしています。

高度な材料

高度な材料で多くの新しいトレンドの背後にありますIc包装を使用します。エンジニアは、熱をうまく動かし、電気でよりよく働き、長持ちする材料を選びます。これらの材料はハイパワーに役立ちますIc必要があります。銅リンク、低k誘電体、および新しい基板により、3Dパッケージングやウェーハレベルのパッケージングなどの新しいパッケージタイプが可能になります。

-

マイクロ流体冷却や内蔵ヒートパイプなどの新しい冷却材料は、チップを冷たく保ち、長持ちさせるのに役立ちます。

-

より優れたサーマルインターフェイス材料は、チップがより多くの熱を処理するのに役立ちます。

-

不均一な統合は、1つのパッケージで多くの半導体材料を使用します。これにより、パフォーマンスが向上し、電力使用量が削減されます。

-

業界は地球を助けるためにリサイクル可能でグリーンなパッケージを作っています。

-

パッケージングは、熱、電力、温度変化、およびEMIやクロストークなどの信号の問題を処理する必要があります。

-

より小さなデバイスには、それでもうまく機能し、コストがかからない、小さくて複雑なパッケージが必要です。

エンジニアは、新しい技術とチップ設計を支援する新しい材料を探し続けています。これらの努力は確かめますIc包装現代のチップが必要とするものについていく。

🔍注:

高度な材料および新しい包装の方法への移动は未来をの形作りますIc包装を使用します。これらの分野で働く企業は、チップの次の大きな変化をリードします。

課題と考慮事項

製造の複雑さ

集積回路パッケージングは、製品の製造において多くの問題を抱えている。業界は多くのステップと厳格な規則に従わなければなりません。研究はこれらの製品を作る際のいくつかの大きな問題を示しています:

-

半導体工場が足りないより少ないチップが作られることを意味します。これにより、新しいテクノロジーが遅くなります。

-

他の国の部品に依存すると、サプライチェーンの問題を引き起こす可能性があります。

-

厳しい政府の規則により、新しい工場を建設することは困難です。これは市場を遅くします。

これらのことはより多くの包装を作ることを難しくします。企業はより良い機械を購入し、熟練労働者を雇う必要があります。この作業には、クリーンルームと特別なツールが必要です。パッケージングが良くなるにつれて、すべてのステップがより高い基準を満たす必要があります。

テストと信頼性

テストと信頼性はパッケージングにおいて非常に重要です。企業は、より良い結果を得るために新しい品質管理システムを使用しています。例:

-

台湾の会社はテストしました新しいリアルタイム品质管理システムを使用します。

-

システムは特別な方法を使用して最良の設定を見つけます。

-

これは、より良い製品とより少ない間違いを作るのに役立ちます。

-

品質チェックでは、回路プローブテストがどれだけうまく機能するかを調べます。

-

このシステムは、スマートファクトリーがパッケージング前に高い基準を維持するのに役立ちます。

これらの方法は、企業が問題を早期に発見し、製品がうまく機能することを確認するのに役立ちます。チップが小さくなるにつれて、テストはさらに注意する必要があります。

コストとスケーラビリティ

コストとスケーラビリティはパッケージングの大きな心配です。新しい包装には、高価な材料と機械が必要です。企業は新しいことに挑戦するだけでなく、価格を低く抑える必要があります。より多くの製品を作ることはお金と資源を使い果たすことができます。中小企業は大企業との競争に苦労するかもしれません。業界はお金を節約する方法を探していますが、それでも良い製品を作り、需要を満たしています。

エコシステムコラボレーション

生態系のコラボレーションは、パッケージングの前進に役立ちます。一人ですべてを行うことはできません。サプライヤーや機器メーカーと協力することで、新しいアイデアを生み出すことができます。ルールを共有し、率直に話すことで、問題の解決と作業が容易になります。チームワークはまた、サプライチェーンの問題に役立ち、部品を継続します。

💡エコシステムの優れたチームワークは、より速い進歩とより良いパッケージングソリューションをもたらします。

集積回路パッケージングは、半導体にとって依然として非常に重要です。以下の表は、パッケージングが業界の成長と変化にどのように役立つかを示しています。

|

メトリック/トレンド |

詳細 |

|---|---|

|

約6,970億ドル |

|

|

市場成長率 (2025-2030) |

毎年7%-9% |

|

キーテクノロジー |

3Dスタッキング、システムインパッケージ、ファンアウトウェハレベルのパッケージ |

包装のトレンドを見ている人は、新しいニーズに追いつくことができます。彼らはまた、新しい技術をリードするのに役立ちます。パッケージングは、より良いパフォーマンスと将来の新しい用途のために重要なままになります。

よくある質問

集積回路パッケージングとは何ですか?なぜ重要なのですか?

集積回路パッケージングは、チップを害から安全に保ちます。チップをデバイス内の他の部品に接続します。また、熱をチップから遠ざけるのにも役立ちます。これにより、デバイスの動作が改善され、長持ちします。エンジニアはパッケージングを使用して、電子機器をより強く、より速くします。

高度なパッケージング技術は半導体のパフォーマンスをどのように改善しますか?

高度なパッケージング技術により、接続が短くなります。これは、信号がより速く、より良く動くのを助けます。これらの方法により、より多くの部品が小さなスペースに収まります。デバイスはより速く動作し、より少ない電力を使用できます。これは電子工学をよく働かせ、エネルギーを節約します。

チプレットベースのデザインとは何ですか?なぜ人気があるのですか?

Chipletベースのデザインは、チプレットと呼ばれる小さなブロックを使用します。エンジニアは1つのパッケージに異なるチップレットを混ぜることができます。これは、新しいデバイスをより速くするのに役立ちます。チップレットの設計により、企業は他の部品を使用できます。ユニバーサルチップレット相互接続エクスプレスは、チップレットをリンクするのに役立ちます。

どの基準がicの包装と製造プロセスをガイドしますか?

JEDECとIPCは、icのパッケージングとテストのルールを作成します。これらの規則は、企業が優れた安全な製品を作るのに役立ちます。また、さまざまな企業が協力するのにも役立ちます。ルールは、icパッケージを作成およびテストする新しい方法をサポートしています。

Icパッケージングの未来を形作るトレンドは何ですか?

トレンドには、3Dスタッキング、チプレットシステム、および新素材が含まれます。エンジニアはこれらを使用して、より小型で高速なデバイスを作成します。業界はまた、地球を助けるためにグリーンパッケージに取り組んでいます。新しいアイデアは、電子機器の動作を改善し、長持ちさせるのに役立ちます。