Una guía para las placas de evaluación SiC MOSFET

Eligió los MOSFET de SiC por su increíble velocidad y eficiencia. Sin embargo, es probable que se enfrentan a tres grandes obstáculos: la implementación de una unidad de puerta precisa, la gestión de c

Eligió los MOSFET de SiC por su increíble velocidad y eficiencia. Sin embargo, es probable que se enfrente a tres grandes obstáculos: implementar una unidad de puerta precisa, administrar los parásitos del circuito y garantizar un diseño de PCB seguro. Esta guía proporciona un camino práctico para dominar estas áreas. Una placa de evaluación sic mosfet es una excelente herramienta práctica, especialmente a medida que el mercado de SiC se expande rápidamente.

📈El mercado de SiC de un vistazoEl cambio de la industria a SiC es claro, haciendo que estas habilidades de diseño sean más valiosas que nunca.

Métrica

Valor

Tamaño del mercado (2024)

Tamaño proyectado (2033)

US $7300,86 millones

CAGR (2024-2033)

22,5%

Este recurso ofrece las reglas esenciales y las mejores prácticas para ayudarlo a desbloquear el rendimiento completo de la tecnología SiC.

Puntos clave

Conduzca los MOSFETs de SiC con cuidado. Use voltajes de puerta específicos y características de protección para que funcionen mejor.

Control de pequeños efectos eléctricos no deseados. Mantenga los cables cortos y use conexiones especiales para detener los picos de voltaje.

Diseñe su placa de circuitoBien. Haga que las rutas de alimentación sean pequeñas y mantenga las piezas de alto voltaje separadas para mayor seguridad y buen rendimiento.

Utilice una placa de evaluación SiC MOSFET. Le ayuda a practicar y probar estas importantes reglas de diseño.

Optimización del circuito Gate Drive

No puede conducir unMOSFET SiCComo un dispositivo de silicio tradicional. Su velocidad de conmutación rápida exige un circuito de accionamiento de puerta más robusto y preciso. Su diseño debe entregar señales de puerta limpias y fuertes para lograr los beneficios de eficiencia y rendimiento de SiC.

Selección del voltaje de la puerta

Debe seleccionar los voltajes de puerta correctos para un rendimiento óptimo. Un voltaje de encendido más alto, típicamente entre15V y 20V, Mejora completamente el canal. Esto minimiza la resistencia de encendido del dispositivo (RDS(on) y reduce las pérdidas de conducción.

Para apagar, debe usar un voltaje negativo, a menudo entre-2V y-5V. Este sesgo negativo crea una fuerte defensa contra el encendido parasitario. La conmutación de alta frecuencia puede inducir picos de voltaje en la puerta, y un voltaje negativo asegura que el MOSFET permanezca firmemente apagado. Usando un-3V sesgo, por ejemplo, puede reducir las pérdidas de apagado hasta en un 25%.

💡Consejo profesional: establece tu UVLO correctamenteEl bloqueo de subtensión (UVLO) del conductor de la puerta es una característica de seguridad crítica. Debe establecer su umbral significativamente por encima de la región de meseta Miller del MOSFET de SiC (alrededor de 8-9V). Un UVLO de 15V para una impulsión de la puerta 20V se asegura que el dispositivo actúa con seguridad y evita caída de voltaje excesiva.

Tamaño del resistor de la puerta

La resistencia de puerta controla la velocidad de conmutación. Una resistencia más pequeña permite una conmutación más rápida, lo que reduce las pérdidas de conmutación. Sin embargo, un valor que es demasiado pequeño puede causar ruido excesivo e interferencia electromagnética (EMI). Tu objetivo es encontrar un equilibrio. Una junta de evaluación sic mosfet a menudo incluye múltiples huellas para la puertaResistencias, Lo que le permite experimentar y encontrar el valor ideal para su aplicación.

Características de protección esenciales

Su circuito de accionamiento de puerta necesita una protección robusta para evitar el fallo del dispositivo. Dos características clave son laAbrazadera Miller activaProtección de la desaturación (DESAT).

Abrazadera Miller activa: Esta función evita el encendido falso causado por el efecto Miller. Cuando el MOSFET se apaga, la pinza proporciona una trayectoria de baja impedancia desde la puerta hasta la fuente. Esta ruta desvía la corriente inducida lejos de la puerta, manteniendo el voltaje bajo y manteniendo el dispositivo apagado de forma segura.

Protección de la desaturación (DESAT)Esto protege al MOSFET durante eventos de cortocircuito. Supervisa el voltaje de drenaje a fuente (VDS). Si VDS se eleva por encima de un umbral establecido mientras el MOSFET está encendido, el controlador inicia un apagado seguro y controlado.

La implementación de estas soluciones avanzadas de accionamiento de puerta puede ser compleja. Para obtener soporte especializado, puede buscar socios de soluciones designados por HiSilicon comoNovaTechnology Company (HK) Limited, que proporciona experiencia en el despliegue de tales tecnologías.

Gestión de circuitos parasitáticos

La increíble velocidad de los MOSFET de SiC es su mayor ventaja, pero también crea su mayor desafío de diseño. Sus transitorios de conmutación son de 5 a 10 veces más rápidos que los IGBT tradicionales. Esta velocidad amplifica los efectos negativos deInductancia parásitaY la capacitancia en su circuito.

Efectos de inductancia parasitaria

Cada traza de alambre y PCB tiene inductancia parásita. Cuando se cambia un MOSFET SiC, la corriente cambia muy rápidamente (un di/dt alto). Este cambio rápido induce aPico de tensión a través de la inductancia parásita, Descrito por la fórmulaV = L * (di/dt). Este exceso de voltaje se suma al voltaje de funcionamiento normal y puede exceder fácilmente la clasificación de ruptura del MOSFET, lo que lleva a la falla del dispositivo.

Después del pico inicial, la energía almacenada en la inductancia parásita resuena con la capacitancia parásita del dispositivo. Esto crea una oscilación amortiguada, o "timbre", que se puede ver en un osciloscopio. Este sonido es una fuente importante de interferencia electromagnética (EMI) y agrega más estrés al componente.

Puede administrar estos efectos con opciones de diseño inteligentes:

UsoConexiones Kelvin-Fuente:Paquetes como el TO247-4L proporcionan una conexión de fuente separada para el controlador de puerta. Esto evita la ruta de la fuente de alimentación principal, evitando que las caídas de voltaje interfieran con la señal de la puerta y asegurando una conmutación más limpia.

Seleccionar paquetes de baja inductancia:Los paquetes de montaje en superficie como el D2PAK-7L o el DFN8X8 están diseñados con una inductancia interna significativamente más baja. Usarlos ayuda a minimizar el exceso de voltaje desde el principio.

Problemas de capacitancia parasitaria

Capacitancia parásitaExiste entre los cables de los componentes, a través de rastros de PCB y dentro del propio MOSFET. Aunque a menudo pequeña, esta capacitancia forma un circuito de tanque resonante con inductancia parásita. Durante eventos de conmutación rápida, este circuito de tanque de L-C es lo que causa el timbre de alta frecuencia que genera EMI y estresa su dispositivo. La gestión eficaz de la inductancia parásita es la forma más directa de controlar esta resonancia no deseada.

Medición y caracterización

No puedes mejorar lo que no puedes medir. ElLa prueba de doble pulso (DPT) es el método estándar de la industriaPara caracterizar el rendimiento de conmutación y cuantificar el impacto de los parásitos. Una placa de evaluación sic mosfet es la plataforma perfecta para realizar un DPT.

La prueba consiste en aplicar dos pulsos de voltaje distintos a la puerta del MOSFET para medir sus características de encendido y apagado en condiciones reales.

🔬Realización de una prueba de doble pulso

Primer pulso:Se aplica un pulso largo para construir corriente en el inductor de carga a su nivel de prueba deseado.

Fase de interrupción:Apaga el MOSFET por un período muy corto. Esto le permite medir la energía de apagado.

Segundo pulso:Se aplica un segundo pulso corto para volver a encender el MOSFET. Esto le permite medir la energía de encendido y las características de recuperación inversa.

Para obtener resultados precisos, la configuración de la prueba es crítica. Necesitarás unOsciloscopio, un generador de funciones, una fuente de alimentación de CC y sondas adecuadas. Deskew siempre sus sondas de voltaje y corriente para garantizar una alineación de tiempo precisa, ya que incluso pequeñas desalineaciones pueden provocar errores significativos en los cálculos de pérdida de conmutación.

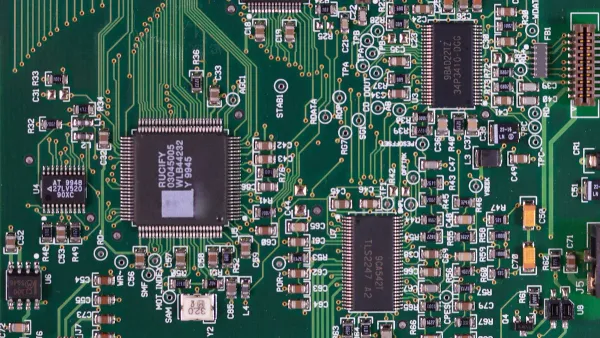

Diseño para una placa de evaluación SiC MOSFET

Debe ver la placa de evaluación del fabricante como un diseño de referencia. Su diseño revela las mejores prácticas para desbloquear el rendimiento de SiC. Un diseño deficiente puede socavar incluso el mejor diseño de circuito al introducir ruido, exceso de voltaje y riesgos de seguridad.

Disposición de la etapa del poder

Su objetivo principal en la etapa de potencia es minimizar la inductancia parásita. Debe hacer que el bucle de potencia de alta frecuencia-la ruta desde el enlace de CCCondensador, A través del MOSFET, y atrás-tan pequeño y apretado como sea posible. Usando unPCB multicapa con planos de potencia y tierra estrechamente espaciadosEs una estrategia eficaz. Este diseñoSuprime la inductancia de bucle y mitiga los picos de tensión, Que protege sus dispositivos de potencia.

Diseño de bucle Gate Drive

El bucle de accionamiento de puerta es tan crítico como el bucle de etapa de potencia. Un bucle de puerta grande introduce inductancia que puede ralentizar la conmutación y causar timbre en la señal de la puerta.

💡Sugerencia de diseño: Keep It CloseDeberíasColoque el controlador de la puerta IC lo más cerca posible del MOSFET.Ruta de las rutas de retorno y de la unidad de puertaComo un par diferencial, ejecutándolos en paralelo y cerca para minimizar el área del bucle y garantizar una señal limpia y rápida.

Seguridad y aislamiento de alto voltaje

La seguridad no es negociable. Debe mantener una separación adecuada entre los circuitos de alto voltaje y bajo voltaje. Esto implica dos distancias clave:

LiquidaciónLa distancia más corta a través del aire entre dos conductores.

Creepage (en inglés)Distancia más corta a lo largo de la superficie de la PCB entre dos conductores.

Puede encontrar requisitos específicos en normas de seguridad comoIPC-2221YUL-60950-1. Para mejorar el aislamiento, puedeCortar ranuras físicas en el PCBEntre trazas de alto voltaje. Esto aumenta la distancia de fuga. También deberíasSepare su tierra de control (GND) de su tierra de poder (PGND), Conectándolos solo en un punto único y silencioso para evitar que el ruido de alimentación corrompa sus señales de control.

Diseño de gestión térmica

Los MOSFET de SiC pueden calentarse, y su diseño de PCB debe ayudar a disipar ese calor. Para dispositivos de montaje en superficie, puede utilizarVías térmicas para crear una ruta de baja resistencia para que el calor viaje desde el dispositivo a grandes planos de cobreEn otras capas. EstosLos aviones de cobre actúan como esparcidores del calor, distribuyendo el calor y previniendo puntos calientes localizados. Una placa de evaluación sic mosfet a menudo demuestra un excelente diseño térmico con grandes áreas de cobre expuestas.

Puede desbloquear todo el potencial de la tecnología SiC. Tu éxito depende de tres acciones principales. En primer lugar, debe implementar una unidad de puerta robusta con voltajes y protección correctos. En segundo lugar, necesita reducir sus áreas de potencia y de bucle de puerta para minimizar la inductancia parásita. En tercer lugar, debe diseñar un diseño seguro con espacios libres adecuados y trayectorias térmicas.

Seguir estas pautas le ayuda a lograr importantes ganancias de rendimiento:

AlcanceEficiencia superior al 98,5%.

Lograr una alta densidad de potencia, como un convertidor de 1.657 kW/L.

Reduzca el tamaño de los componentes magnéticos utilizando frecuencias de conmutación más altas.

Una tabla de evaluación sic mosfet es una excelente herramienta para practicar estas técnicas. Al aplicar estas reglas, puede evitar fallas comunes y construir sistemas de energía altamente eficientes y compactos.

Preguntas frecuentes

¿Por qué debería usar MOSFET de SiC en lugar de silicio?

Debe elegir los MOSFET de SiC por su rendimiento superior. Ofrecen una mayor eficiencia, velocidades de conmutación más rápidas y una mejor conductividad térmica. Esto le permite construir más pequeño, más ligero y más eficienteSistemas eléctricosComparados con los dispositivos de silicio tradicionales.

¿Cuál es la regla de diseño más importante para SiC?

Debe minimizar la inductancia parásita. Mantenga sus bucles de potencia de alta frecuencia y de accionamiento de puerta lo más pequeños y ajustados posible. Un diseño compacto evita el exceso de voltaje y el zumbido, lo que protege sus componentes y reduce la interferencia electromagnética (EMI).

¿Qué es una prueba de doble pulso (DPT)?

Una prueba de doble pulso le ayuda a medir el rendimiento de la conmutación de su MOSFET. Se utiliza para encontrar las pérdidas de energía de encendido y apagado en condiciones de funcionamiento específicas. Esta prueba es esencial para verificar su diseño y cuantificar el impacto de los parásitos del circuito.

¿Cómo se elige un valor de resistencia de puerta de arranque?

Puede comenzar con el valor recomendado en la hoja de datos del MOSFET SiC o en la placa de evaluación. Este valor proporciona un equilibrio seguro entre la velocidad de conmutación y el timbre. A continuación, puede ajustarlo para optimizar el rendimiento de su aplicación específica.