Proceso de diseño de ASIC: una guía paso a paso para crear circuitos integrados específicos para aplicaciones

El proceso de diseño ASIC ayuda a hacer chips para usos especiales. A diferencia de los procesadores normales, los ASIC ofrecen un alto rendimiento para tareas específicas.

ElProceso de diseño de ASICAyuda a hacer chips para usos especiales. A diferencia de los procesadores normales, los ASIC ofrecen un alto rendimiento para tareas específicas. Estos chips personalizados funcionan mejor, cuestan menos y hacen más. ElASICPasos de diseño necesitan una cuidadosa planificación y trabajo. Son importantes para industrias como automóviles, teléfonos y gadgets. Por ejemplo, los autos eléctricos usan ASIC para administrar la energía y hablar con las piezas. Los pasos claros en el diseño de ASIC ayudan a crear chips confiables y ahorradores de energía para las necesidades de hoy.

Puntos clave

-

Los objetivos claros son muy importantes. Guían el diseño ASIC y evitan grandes errores.

-

La comprobación de la función del chip asegura que funciona bien. Este paso encuentra problemas temprano, ahorrando tiempo y dinero.

-

El uso de herramientas inteligentes para la codificación y el diseño ayuda mucho. Estas herramientas hacen chips fuertes y rápidos.

-

Los diseños amigables con la prueba facilitan las pruebas. Ayudan a encontrar y solucionar problemas temprano para que el chip funcione bien más tarde.

-

Se necesita un buen archivo GDSII para hacer chips. Asegura que el diseño siga las reglas de fábrica y funcione correctamente.

Especificación y generación de código RTL

Configuración de especificaciones

El primer paso para hacer un ASIC es establecer especificaciones. Esto significa decidir qué debe hacer el chip, qué tan rápido debe funcionar y los límites que tiene. Este paso mantiene el proceso de diseño organizado y en marcha. AEspecificación clara funciona como un planGuiando todo el proyecto. Ayuda a evitar errores que podrían retrasar el trabajo o aumentar los costos. Este paso generalmente toma de 2 a 6 semanas porque necesita atención cuidadosa.

Las especificaciones también te ayudan a descubrir las características principales del chip. Por ejemplo, si está haciendo un chip para un teléfono inteligente, puede centrarse en ahorrar energía y trabajar más rápido. Las especificaciones claras aseguran que el chip haga lo que se supone que debe hacer.

Escribir código RTL

Después de establecer las especificaciones, puede comenzar a escribir el código RTL (Register Transfer Level). Este código muestra cómo funciona y se construye el chip. Utiliza lenguajes especiales como Verilog o VHDL. Código RTL convierte las especificaciones en un modelo de trabajo del chip.

En esta etapa, debe verificar que el código RTL coincida con las especificaciones. La verificación a menudo ayuda a encontrar errores temprano y ahorra tiempo más tarde. Por ejemplo, el uso de puntos de control durante la depuración puede ayudar a encontrar piezas faltantes o errores más rápido, haciendo que el proceso sea más suave.

Herramientas para especificaciones y código RTL

Hay herramientas para ayudar con el establecimiento de especificaciones y la escritura de código RTL. Estas herramientas facilitan el proceso y mejoran el diseño. Por ejemplo, las herramientas de simulación le permiten probar el código RTL para asegurarse de que funciona según lo planeado.

Un estudio de caso muestra cuán útiles pueden ser las herramientas RTL. La depuración con puntos de control ayudó a encontrar problemas más rápido que solo usar registros. EstoLa tasa de aprobación mejoró de 72.4% a 93.6%.. Muestra cómo las herramientas avanzadas pueden mejorar el diseño de ASIC.

|

Configuración |

Tasa de pase (%) |

Mejora (%) |

|---|---|---|

|

LLM vainilla |

72,4 |

N/A |

|

Agente único |

83,9 |

11,5 |

|

Multi-agente |

93,6 |

21,2 |

El uso de estas herramientas puede hacer que su ASIC sea más confiable y funcione mejor.

Verificación funcional

La verificación funcional verifica si el chip funciona según lo planeado.Se asegura de que el chip cumpla con sus objetivos y evite errores. Saltar este paso puede causar fallas, perder dinero y molestar a los clientes. La verificación temprana ayuda a detectar errores y hace que el chip sea más confiable.

Asegurarse de que el diseño es correcto

Este paso asegura que el chip coincida con su plan y funcione bien. Reduce los riesgos como chips rotos o bajo rendimiento. Para las empresas sin fábricas, construye la confianza del cliente mediante la entrega de buenos chips. Las fábricas también pierden menos material cuando se verifican los diseños.

-

Por qué es importante la verificación funcional:

-

Se asegura de que el chip siga su plan.

-

Disminuye las posibilidades de problemas con el chip.

-

Construye la confianza del cliente.

-

Ahorra materiales durante la producción.

-

Uso de simulaciones

Las simulaciones prueban el chip en diferentes situaciones. Encuentren problemas antes de hacer el chip. Estas pruebas verifican cómo se comporta y funciona el chip. Los métodos como pruebas lógicas y comprobaciones formales son comunes para este paso.

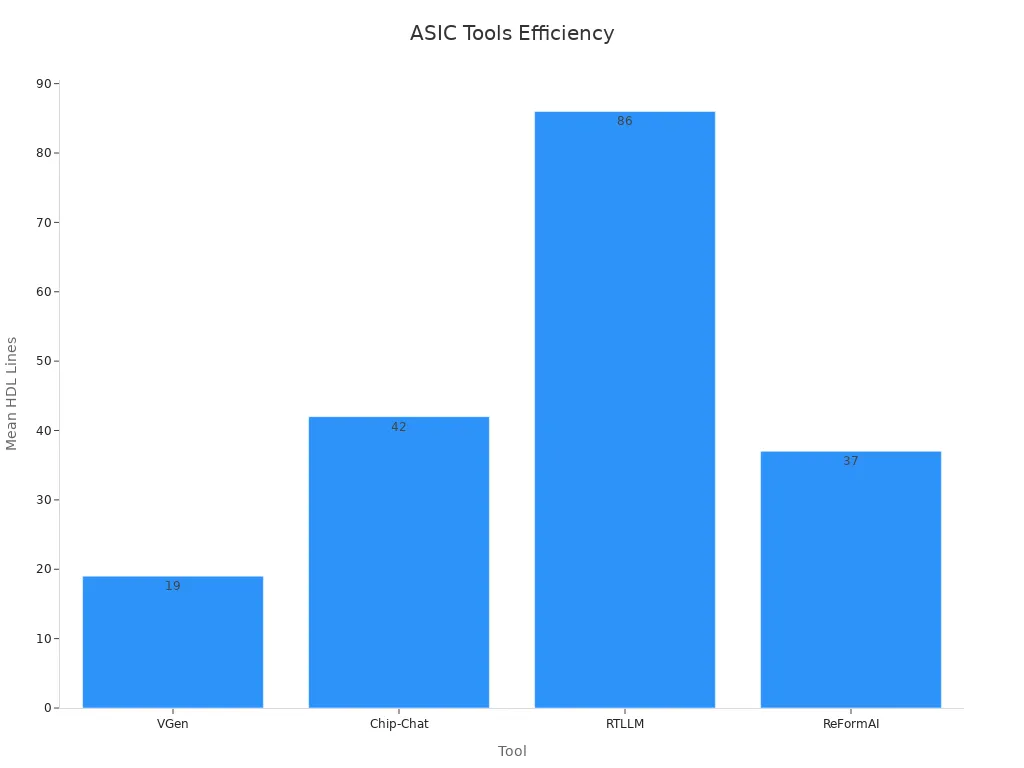

Por ejemplo, herramientas como VGen y RTLLM ayudan a probar chips de diferentes tamaños.La siguiente tabla muestra qué tan bien estas herramientas manejan diferentes cantidades de código:

|

Herramienta |

Diseños probados |

Total de líneas de código |

Líneas promedio |

Max Líneas |

Total de líneas de código |

|---|---|---|---|---|---|

|

VGen |

17 |

0,3 K |

19 |

48 |

0,3 K |

|

Chip-Chat |

8 |

0,3 K |

42 |

72 |

0,3 K |

|

RTLLM |

30 |

2,5 K |

86 |

518 |

2,5 K |

|

ReFormAI |

30 |

Por 2227K |

37 |

773 |

Por 2227K |

Herramientas para comprobar diseños

Las herramientas especiales hacen que la comprobación de los diseños sea más fácil y mejor. Estas herramientas encuentran y solucionan problemas rápidamente. También ayudan al chip a cumplir sus objetivos y a funcionar bien.

El siguiente gráfico muestra cuánto código pueden manejar diferentes herramientas:

El uso de estas herramientas hace que el proceso de verificación sea más rápido y mejora el éxito del chip.

RTL a nivel de puerta Netlist

¿Qué es Síntesis?

La síntesis es un paso importante en la fabricación de ASICs. Cambia el código RTL (Register Transfer Level) en una netlist de nivel de puerta. Esta netlist muestra las puertas lógicas físicas del chip. Synthesis conecta la idea de diseño con el chip real. Se asegura de que el chip se pueda construir y aún funcione según lo planeado.

En síntesis, el diseño se mejora en velocidad, tamaño y potencia. Estas mejoras ayudan al chip a cumplir sus objetivos sin perder rendimiento. Por ejemplo, las herramientas de síntesis convierten el código RTL en celdas estándar de una biblioteca. Esto crea un diseño que es bueno y fácil de hacer.

Cómo RTL se convierte en una Netlist de nivel de puerta

Cambiar RTL a una netlist de nivel de puerta tiene pasos. En primer lugar, las herramientas de síntesis convierten el código RTL en un diseño básico de nivel de puerta. Luego, el diseño se mejora para hacerlo más rápido, usar menos energía y trabajar mejor. Finalmente, la lista de redes se comprueba para que coincida con el plan original.

Este proceso también sigue reglas como límites de tiempo y tamaño. Estas reglas aseguran que el chip funcione bien en la vida real. Por ejemplo, al hacer CPUs o chips criptográficos, las herramientas de síntesis recuperan muy bien los registros.La siguiente tabla muestra qué tan bien funcionan las herramientas de síntesis para diferentes diseños:

|

Tipo de diseño de hardware |

Tasa de recuperación |

Notas |

|---|---|---|

|

Coprocesadores criptográficos |

Casi perfecto |

Recupera los registros de alto nivel de manera efectiva |

|

CPUs |

Casi perfecto |

Funciona bien en muchos diseños |

|

OpenTitan (SoC) |

Casi perfecto |

Apoyado por expertos de la industria |

Herramientas para hacer listas de redes a nivel de puerta

Muchas herramientas ayudan a crear netlists a nivel de puerta para ASIC. Los más populares son Synopsys Design Compiler, Cadence Genus y Mentor Graphics Precision. Estas herramientas hacen que la síntesis sea más fácil y más precisa. También verifican el tiempo y mejoran el uso de energía, que son clave para buenos chips.

El uso de estas herramientas hace que la síntesis sea más rápida y reduce los errores. Por ejemplo, Synopsys Design Compiler comprueba el tiempo y aumenta el rendimiento. Cadence Genus ayuda a reducir el uso de energía, por lo que es una gran herramienta para el diseño ASIC.

Diseño ASIC Diseño

Fundamentos del diseño de layout

El diseño de un ASIC es como un mapa de su estructura. Muestra dónde van las partes y cómo se conectan. Un buen diseño ayuda a que el chip funcione bien, use menos energía y cumpla sus objetivos. Este paso es muy importante porque afecta cuán confiable y útil será el chip.

Durante este paso, debes pensar en muchas cosas. Estos incluyen dónde colocar las puertas, cómo conectarlas y seguir las reglas de diseño. Cada elección cambia la forma en que funciona el chip y lo fácil que es hacerlo. Por ejemplo, un diseño más pequeño puede hacer que las señales sean más rápidas y ahorrar energía.

Pasos para hacer un layout

Hacer un diseño tiene muchos pasos para convertir el diseño en un chip real. Primero, la planificación del piso organiza las partes principales del chip. Luego, la colocación decide exactamente dónde va cada parte. Después de eso, el enrutamiento conecta las partes con cables y evita problemas como retrasos.

Comprobar el diseño es muy importante en este paso. Debe asegurarse de que siga las reglas y cumpla con el plan. Las herramientas verifican problemas como malas señales o problemas de tiempo. Estos controles detienen errores costosos antes de hacer el chip.

Hoy,Machine Learning ayuda con muchas de estas tareas. Mejora la colocación y el enrutamiento para mejorar los chips y usar menos energía. Esto hace que el proceso sea más rápido y crea diseños de mayor calidad.

Herramientas para mejores diseños

Herramientas especiales hacen diseño de diseño más fácil y más rápido. Las herramientas impulsadas por AI prueban muchos diseños para encontrar el mejor diseño. Ahorra tiempo, mejora el rendimiento y hace que los chips usen menos energía. Al usar datos pasados, estas herramientas crean mejores diseños más rápido que los métodos más antiguos.

Por ejemplo, las herramientas de aprendizaje automático manejan las tareas de diseño mejor que los humanos. Hacen chips de mayor calidad y los preparan más rápido. El uso de estas herramientas hace que el proceso de diseño de ASIC sea más suave y más exitoso.

Diseño para técnicas de prueba

Hacer las pruebas más fáciles

Hacer la prueba más fácil asegura suASICFunciona bien después de que está hecho. Diseñar con pruebas en mente ayuda a encontrar y solucionar problemas temprano. Esto hace que su chip sea más confiable y evita errores costosos durante la producción.

Mejores pruebas también mejoran los resultados después de construir el chip. Por ejemplo:

-

Las sondas especiales ayudan a medir los materiales sobrantes como el flujo.

-

Las pruebas mejoradas proporcionan resultados de pruebas eléctricas más precisos.

-

Aunque difícil,Sondas de punta de celoSon clave para obtener los mejores resultados.

Centrarse en las pruebas asegura suASICFunciona bien y cumple sus objetivos en uso real.

Formas comunes de diseñar para las pruebas

Diseño para pruebas (DFTLos métodos hacen que los chips sean más fáciles de verificar y arreglar. Estos métodos incluyen:

-

Cadenas de escaneoEnlace registros internos en una cadena para encontrar fallas.

-

Autoprueba incorporada (BIST): Deja que el chip se pruebe a sí mismo, necesitando menos equipo.

-

Exploración de límitesComprueba las conexiones entre los chips para asegurarse de que se comunican.

El uso de estos métodos simplifica las pruebas y mejora la calidad de su chip.

Herramientas para el diseño de pruebas

Muchas herramientas ayudan conDFTTécnicas. Los más populares son Synopsys DFTMAX, Cadence Modus y Mentor Tesent. Estas herramientas automatizan tareas como agregar cadenas de escaneo y crear patrones de prueba.

Por ejemplo, Synopsys DFTMAX aumenta la testabilidad sin dañar el rendimiento. Cadence Modus reduce el tiempo de prueba y encuentra más fallas. Mentor TessentMentor añade características avanzadas para BIST y escaneos de límites.

El uso de estas herramientas hace que las pruebas sean más rápidas y asegura suASICEs fiable y funciona bien.

Planificación del piso

Organando piezas de chip

La planificación del piso es un paso clave en la fabricación de ASIC. Significa organizar las partes del chip para que funcionen bien y funcionen mejor. En este paso, usted decide a dónde va cada parte del chip. Piensas en cosas como cómo se conectan las partes, el flujo de potencia y la intensidad de la señal. Un buen plano de planta ayuda a que el chip funcione más rápido, use menos energía y cumpla con sus objetivos.

Una parte importante de la planificación del piso es el manejo de redes. Las redes son los enlaces entre las partes del chip. Por ejemplo,60-70%Redes se conectan a una sola parte. Estas redes a menudo conectan partes cercanas y tienen patrones que son fáciles de detectar. Las redes que se conectan a más de una parte tienen una extensión más uniforme. Conocer estos patrones le ayuda a planificar los cables y evitar problemas con la potencia o la velocidad.

|

Descripción estadística |

Valor/Detalles |

|---|---|

|

Porcentaje de redes con FO = 1 |

60-70% |

|

Características de FO = 1 |

Cola larga, picos para vecinos cercanos y enrutamiento de subgrupos |

|

Características de FO > 1 |

Distribución simétrica y más plana |

|

Enfoque de tabla de carga de alambre |

80-90% percentil para estimación de capacitancia en el peor de los casos |

|

Variación en la longitud neta |

Depende del tamaño del bloque (por ejemplo, 25 k-gate vs. 5 k-gate) |

|

Dependencia en forma de bloque |

Estadísticas calculadas para bloques cuadrados |

|

Dependencia del tipo netlist |

Varía según las restricciones de síntesis (por ejemplo, retraso mínimo frente a área mínima) |

Factores importantes de planificación del piso

Al planificar un diseño de chip, debe pensar en muchas cosas. Estos incluyen el tamaño y la forma de las piezas, el control de calor y el flujo de potencia. Por ejemplo, la planificación para el calor puede ayudar a que el chip se mantenga fresco y funcione mejor. Además, colocar las piezas en los lugares correctos puede hacer que las señales sean más rápidas y los cables más cortos.

Las herramientas de AI ahora ayudan con la planificación de pisosRealizando tareas automáticamente. AI mira los diseños rápidamente y encuentra los mejores diseños. Esto ahorra tiempo y hace mejores chips que hacerlo a mano.

Herramientas para planificación de pisos

Las herramientas modernas hacen que la planificación del piso sea más fácil y mejor. Estas herramientas le permiten probar diferentes diseños y solucionar problemas con el tiempo o la potencia. Las herramientas impulsadas por AI pueden crear diseños que equilibran la velocidad y el uso de energía. También encuentran áreas calientes y sugieren soluciones para mantener el chip confiable.

El uso de estas herramientas hace que la planificación del piso sea más rápida y precisa. Este paso es muy importante para hacer que los ASIC funcionen bien en la vida real.

Colocación

Organización de los componentes para obtener el mejor rendimiento

Colocar los componentes en un chip es muy importante. Afecta a la rapidez y eficiencia con la que funciona el chip. Colocación significa organizar las piezas para que reduzcan los retrasos y ahorren energía. La buena colocación también facilita la conexión de los cables más adelante.

Para verificar la calidad de la colocación, los diseñadores usan ciertas medidas. Dos comunes sonLongitud de cable de medio perímetro (HPWL)YPeor holgor negativo (WNS). Estos ayudan a mostrar cómo la colocación afecta la velocidad y el uso de energía. En el cuadro siguiente se explican estas medidas:

|

Métrica |

Lo que significa |

Por qué importa |

|---|---|---|

|

HPWL |

Trayectorias de alambre más cortas |

Ahorra energía y acelera el flujo de datos |

|

WNS |

Problemas de temporización |

Fijarlos mejora el rendimiento |

|

Preguntas frecuentes sobre FREQ |

Velocidad de chip |

Una frecuencia más alta significa una operación más rápida |

Al centrarse en estos, los diseñadores pueden asegurarse de que el chip cumpla con sus objetivos.

Maneras de colocar componentes

Hay diferentes maneras de organizar las piezas en un chip. Un método es la “colocación estándar de celdas”, donde las piezas pequeñas se alinean en filas. Esto ahorra espacio y acorta los cables. Otra forma es la "macro colocación", que coloca primero las partes grandes. Piezas más pequeñas se añaden más tarde para mejorar el rendimiento.

También se usan métodos avanzados como el recocido simulado y la partición. Estas técnicas prueban muchos diseños para encontrar el mejor. Por ejemplo, el recocido simulado mueve piezas para reducir la longitud del cable y evitar áreas abarrotadas.

Herramientas para una colocación más fácil

Herramientas especiales ayudan a automatizar las tareas de colocación y mejorar los resultados. Herramientas como Cadence Innovus, Synopsys IC Compiler II y Mentor Graphics Olympus-SoC son populares. Verifica problemas como cables abarrotados, problemas de sincronización y uso de energía.

La siguiente tabla muestra lo que miden estas herramientas:

|

Métrica |

Lo que comprueba |

|---|---|

|

Peor holgor negativo (WNS) |

Encuentra el mayor problema de tiempo en el diseño. |

|

Total de holgura negativa (TNS) |

Agrega todos los problemas de tiempo para ver el rendimiento general. |

|

Número de rutas infractores (NVP) |

Cuenta rutas que no cumplen las reglas de temporización. |

|

Congestión |

Comprueba si los cables están demasiado llenos en algunas áreas. |

|

Longitud del alambre (WL) |

Mide la longitud total de los cables en el chip. |

|

Longitud de cable de medio perímetro (HPWL) |

Calcula la longitud del cable sumando la mitad de los perímetros de los cuadros delimitadores. |

|

Macro HPWL (mHPWL) |

Se centra en la longitud del cable solo para piezas grandes. |

El uso de estas herramientas ayuda a crear chips que son rápidos, eficientes y confiables.

Síntesis del árbol del reloj

Mantener las piezas del chip sincronizadas

El árbol del reloj es una parte clave de un chip. Se asegura de que todas las partes del chip funcionen juntas al mismo tiempo. Si el tiempo está apagado, el chip puede no funcionar bien. El árbol de reloj envía la señal de reloj a cada parte del chip. Esto mantiene la sincronización constante y ayuda a que el chip funcione sin problemas. Es muy importante para hacer un ASIC confiable y eficiente.

La síntesis del árbol del reloj funciona para equilibrar la sincronización de la señal del reloj. Este equilibrio se llama desvío del reloj, y debe permanecer pequeño para evitar problemas. Un buen diseño de árbol de reloj reduce los retrasos y ayuda a que el chip funcione mejor.

Pasos para diseñar un árbol de reloj

Hacer un árbol de reloj tiene varios pasos para mejorar el tiempo y la potencia. Primero, decida de dónde provienen las señales de reloj y cómo se propagarán. Luego, asegúrese de que la señal del reloj llegue a todas las partes al mismo tiempo. Una forma de ahorrar energía es la puerta del reloj, que desactiva las partes no utilizadas del árbol del reloj. La apertura del reloj puede ahorrar hasta un 20% de energía, pero puede hacer que el chip sea un poco más grande.

Otro método es la colocación consciente del árbol de reloj. Esto reduce la potencia de conmutación neta al25,3% y potencia total 11,4%. Lo hace con poco efecto en el tiempo (2.0%) y el tamaño del chip (1.2%). El diseño Multi-Corner Multi-Mode (MCMM) también ayuda al mejorar el tiempo, la potencia y las reglas de fabricación en diferentes situaciones.

Herramientas para hacer árboles de reloj

Las herramientas especiales facilitan la síntesis del árbol del reloj. Los más populares son Synopsys PrimeTime, Cadence Innovus y Mentor Graphics Olympus-SoC. Estas herramientas ayudan a diseñar y verificar los árboles de reloj para satisfacer las necesidades de tiempo y energía. También incluyen características para clock gating y MCMM, lo que hace que el proceso sea más rápido.

El uso de estas herramientas ayuda a que su diseño de ASIC funcione mejor y dure más tiempo. Resuelven problemas de tiempo y reducen el uso de energía, creando un chip eficiente y oportuno.

Enrutamiento

Conexión de componentes

El enrutamiento vincula partes de un chip con cables. Asegura que las señales se muevan rápida y correctamente entre las secciones del chip. Este paso es muy importante porque un mal enrutamiento puede ralentizar el chip, desperdiciar energía y dañar el rendimiento. La planificación de los recorridos de los cables evita cuidadosamente las áreas abarrotadas y mantiene el chip funcionando bien.

El enrutamiento crea rutas para las señales mientras sigue las reglas de diseño. Estas reglas incluyen mantener los cables separados, evitar las superposiciones y reducir los problemas de señal. Un buen enrutamiento hace que el chip sea más confiable y mejor para su trabajo.

Estrategias de enrutamiento

Las buenas estrategias de enrutamiento ayudan a que los chips funcionen más rápido y mejor. Diferentes métodos resuelven problemas como cables abarrotados y retrasos de tiempo. Por ejemplo, la unión híbrida conecta múltiples capas de chip, necesitando menos trayectorias de cable anchas. Los circuitos integrados 3D arreglan el hacinamiento de cables 2D pero agregan desafíos con las conexiones verticales. Las herramientas AI colocan bloques de conexión inteligentemente cerca de los bordes para equilibrar las capas de cables.

|

Estrategia de enrutamiento |

Cómo ayuda |

|---|---|

|

Vinculación híbrida |

Vincula varias capas, por lo que se necesitan menos rutas de cable anchas. |

|

ICs 3D |

Corrige el hacinamiento de cables 2D pero agrega desafíos de conexión vertical. |

|

Coloca los bloques de conexión cerca de las aristas para equilibrar las capas de cables. |

Métodos avanzados como el aprendizaje por refuerzo (RL) hacen que el enrutamiento sea más rápido. RL mejora la velocidad de conexión del cable en un 45% con respecto a los métodos más antiguos y es un 32% más rápido que los métodos centrados en el tiempo. En general, los procesos backend son un 22% más rápidos con los métodos de enrutabilidad y un 15% más rápidos con los métodos de temporización.

-

Mejoras del enrutamiento avanzado:

-

Conexiones de cables 45% más rápidasQue los métodos de routability.

-

32% más rápido que los métodos centrados en el tiempo.

-

La aceleración del proceso backend: 22% (capacidad de enrutamiento) y 15% (tiempo).

-

Herramientas para enrutamiento

Las herramientas de enrutamiento hacen que la conexión de piezas de chip sea más fácil y precisa. Las herramientas populares incluyen Cadence Innovus, Synopsys IC Compiler II y Mentor Graphics Olympus-SoC. Estas herramientas planifican las rutas de los cables, reducen el hacinamiento y mejoran el tiempo. También siguen reglas de diseño para satisfacer las necesidades de chips.

Las herramientas modernas a menudo usan AI para mejorar el enrutamiento. AI comprueba los diseños y encuentra las mejores rutas de cables, ahorrando energía y tiempo. El uso de estas herramientas hace que el enrutamiento sea más rápido y da mejores resultados.

Comprobaciones de verificación física

Comprobación del diseño del chip

La verificación física se asegura de que su chip siga las reglas de diseño y funcione. Este paso comprueba si el diseño de chip coincide con el plan original. También garantiza que el chip funcionará correctamente cuando se construya. La solución temprana de problemas ahorra dinero y mejora el rendimiento del chip.

Aquí se necesitan dos controles principales. Primero, confirme que el diseño sigue las reglas de la fábrica. Segundo, asegúrese de que el diseño coincida con el diseño lógico. Estas comprobaciones encuentran problemas como cables demasiado cerca, espaciado incorrecto o enlaces faltantes. Resolver estos problemas temprano hace que el proceso de fabricación de chips sea más suave.

Maneras de verificar los diseños

Hay diferentes maneras de comprobar el diseño de su chip. La comprobación de reglas de diseño (DRC) garantiza que el diseño sigue las reglas de fábrica. Layout Versus Schematic (LVS) compara el diseño con el plan de diseño para asegurarse de que coinciden. La Extracción Parasitaria (PEX) encuentra efectos eléctricos no deseados causados por el diseño.

Por ejemplo, DRC podría detectar cables demasiado juntos, lo que podría causar problemas. LVS comprueba que todas las conexiones del layout existen en el plan. PEX predice cómo los efectos no deseados podrían cambiar el rendimiento del chip. El uso de todos estos métodos proporciona una verificación completa del diseño de su chip.

Herramientas para Verificación de Chip

Herramientas especiales hacen la comprobación de diseños más rápido y más fácil. Los populares incluyen Cadence Pegasus, Synopsys IC Validator y Mentor Calibre. Estas herramientas automatizan tareas como DRC, LVS y PEX, ahorrando tiempo y reduciendo los errores. También dan informes detallados para solucionar problemas rápidamente.

Por ejemplo, Mentor Calibre es ideal para controles precisos DRC y LVS. Synopsys IC Validator maneja bien los diseños complejos. Cadence Pegasus trabaja rápido para chips grandes. El uso de estas herramientas garantiza que su chip cumpla con todas las reglas y funcione de manera confiable.

Preparación del archivo GDSII

Preparar el diseño para la fabricación

El último paso para hacer un ASIC es prepararlo para la fabricación. Aquí, comprueba que el diseño del chip cumple con todas las reglas de fábrica. También se asegura de que el chip funcione correctamente una vez que esté hecho. Es importante corregir cualquier error que pueda dañar el rendimiento o la duración del chip.

Este paso es muy importante porque convierte el diseño digital en un chip real. Un diseño bien preparado ayuda a evitar problemas costosos durante la producción. También mantiene el proceso suave y eficiente.

Pasos para crear un archivo GDSII

Para preparar el diseño, debe crear un archivo GDSII. Este archivo es como un mapa del chip. Muestra dónde van todas las partes, cómo se conectan los cables y detalles sobre las capas.

Primero, exporte el diseño de sus herramientas de diseño al formato GDSII. Luego, comprueba el archivo para asegurarse de que coincide perfectamente con el diseño. Finalmente, envía el archivo a la fábrica para construir el chip. Cada paso debe hacerse con cuidado para evitar errores que podrían causar problemas.

Herramientas para ayudar con los archivos GDSII

Existen herramientas que facilitan la creación y comprobación de archivos GDSII. Algunos populares son Cadence Virtuoso, Synopsys IC Compiler II y Mentor Graphics Calibre. Estas herramientas automatizan tareas como extraer datos de diseño, crear el archivo y encontrar errores. También aseguran que el diseño siga las reglas de fábrica, reduciendo la posibilidad de problemas de producción.

El uso de estas herramientas hace que el proceso de diseño de ASIC sea más rápido y confiable. Ayudan a garantizar que su chip funcione según lo planeado.

El proceso de diseño de ASIC es clave para fabricar chips de propósito especial. Ayuda a crear chips que usan menos energía y funcionan bien. Un plan claro facilita el proceso y reduce los costos. Esto lo hace genial para hacerDe 1.000 a 100.000 chips. El uso de métodos probados de los proveedores reduce los riesgos y acelera la producción.

El trabajo en equipo y las herramientas de diseño inteligente son muy importantes para el éxito. Estas herramientas hacen que las tareas sean más simples y precisas. También aseguran que el chip funcione según lo planeado. Al seguir pasos claros, puede construir chips que ahorren espacio y satisfagan las necesidades tecnológicas actuales.

Preguntas frecuentes

¿Qué es un ASIC y por qué es importante?

Un ASIC es un chip especial hecho para un trabajo. Funciona mejor y utiliza menos energía que los chips normales. Industrias como automóviles y teléfonos usan ASIC para soluciones personalizadas que se ajustan a sus necesidades.

¿Cómo se diseña un ASIC?

El diseño de un ASIC tiene muchos pasos como la planificación, comprobación y pruebas. Cada paso se asegura de que el chip funciona bien y se puede construir. Este proceso ayuda a crear chips confiables y de alto rendimiento.

¿Qué herramientas ayudan a hacer ASIC?

Se utilizan herramientas como Synopsys Design Compiler y Cadence Innovus. Ayudan a construir, organizar y verificar el chip para cumplir sus objetivos.

¿Por qué es importante comprobar la función del chip?

Comprobar que el chip funciona según lo planeado. Encuentra errores temprano, ahorrando tiempo y dinero. Este paso es clave para hacer un chip bueno y confiable.

¿Cómo afecta el diseño al chip?

El diseño muestra dónde van las piezas y cómo se conectan. Un buen diseño hace que el chip sea más rápido, ahorra energía y mejora su funcionamiento en general.